## Enhanced Semiconductor Nanocrystal Conductance via Solution Grown Contacts

Matthew T. Sheldon<sup>1</sup>, Paul-Emile Trudeau<sup>1</sup>, Taleb Mokari<sup>2</sup>, Lin-Wang Wang<sup>3</sup> and A. Paul Alivisatos<sup>1,4</sup>\*

1 University of California, Berkeley, California 94720, USA

2 Molecular Foundry, Materials Sciences Division, Lawrence Berkeley National Laboratory

3 Computational Research Division, Lawrence Berkeley National Laboratory

4 Lawrence Berkeley National Laboratory, Berkeley, California 94720, USA

msheldon@berkeley.edu

\*alivis@uclink4.berkeley.edu

ABSTRACT We report a 100,000-fold increase in the conductance of individual CdSe nanorods when they are electrically contacted via direct solution phase growth of Au tips on the nanorod ends. Ensemble UV-Vis and X-Ray photoelectron spectroscopy indicate this enhancement does not result from alloying of the nanorod. Rather, low temperature tunneling and high temperature (250-400 K) thermionic emission across the junction at the Au contact reveal a 75% lower interface barrier to conduction compared to a control sample. We correlate this barrier lowering with the electronic structure at the Au-CdSe interface. Our results emphasize the importance of nanocrystal surface structure for robust device performance and the advantage of this contact method.

KEYWORDS (Word Style "BG\_Keywords"). If you are submitting your paper to a journal that requires keywords, provide significant keywords to aid the reader in literature retrieval.

#### MAIN TEXT

Single nanostructure electrical measurements directly probe the fundamental limits of semiconductor device miniaturization, providing some of the most precise characterization available of electronic structure resulting from quantum confinement and dimensional control.<sup>1</sup> When the strategy is employed for colloidal semiconductor nanocrystals we also learn the ultimate transport efficiencies of these materials, crucial for determining their utility in photovoltaic applications, as one important example, without the convolution of particle-particle carrier hopping mechanisms or particle size dispersity that are difficult to account for in studies of nanocrystal thin film solids.<sup>2</sup>

Besides fabrication challenges, single particle experiments are complicated by the specific electronic structure of the semiconductor-metal interface between the nanoparticle and the device electrode, which critically determines the barrier physics to charge injection and thereby overall device performance. The nanocrystal surfactant coverage, heightened surface energy, and decreased density of states may contribute to the complex interface of a contacted device.<sup>3,4</sup> Indeed, the variety of II-VI semiconductor colloid single particle electrical behavior reported in the literature suggests the contact method may be as important as the sample itself for determining the device properties at such small scales. For example, previous work from this group tracked severe compositional modification of single nanocrystals into separate regions with coupled electrical response when contacted by traditional lithographic techniques.<sup>5</sup> This contrasts trapping<sup>6</sup> or STM experiments<sup>7</sup> that display tunneling behaviors that depend significantly on the strength of the coupling to the electrode and therefore also the nanocrystal interface electronic structure.

The goal of this study is to offer a systematic comparison of CdSe nanorods with and without Au tips

to test the influence of the contacts. Using a synthetic method reported previously, CdSe nanorods are tipped with Au in solution, giving an intimate, abrupt nanocrystal-metal contact free of surfactant. We compare electrical response to a control sample of standard CdSe rods, with nanocrystals of both type individually adsorbed to pre-defined Au junctions. We report a large increase in the conductance of the Au-tipped CdSe heterostructures and explain this in terms of the differing electronic structure of the Au-CdSe interface for both samples.

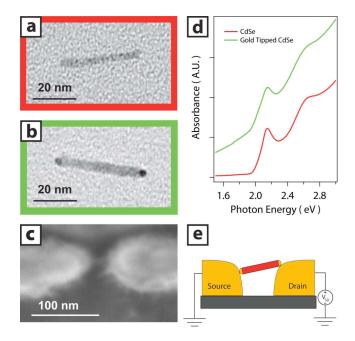

CdSe nanorods were synthesized and purified using a previously published method<sup>11</sup>, and dissolved in toluene. (red TEM, fig. 1). A fraction of the sample was tipped with Au according to a method described previously by Mokari.<sup>11</sup> (green TEM, fig. 1). Briefly, a toluene solution containing gold trichloride (AuCl<sub>3</sub>, 12 mg, 0.04 mmol), didodecyldimethylammonium bromide (DDAB, 40 mg, 0.08 mmol), and dodecylamine (DDA, 70 mg, 0.37 mmol) was sonicated for 5 minutes and then added dropwise to a suspension of nanorods stirring under N2. The product was precipitated with methanol and separated by centrifugation.

Source and drain electrodes with junctions spanning 20-40nm were fabricated on silicon wafer test chips using e-beam lithography, followed by deposition of 55 nm Au on 10 nm Ti. A film of 10 nm of silicon nitride or aluminum oxide was deposited via atomic layer deposition [ALD] before the electrodes to prevent shorting through the silicon substrate.

The nanorod samples were adsorbed to these pre-defined Au junctions by submerging the chip in the appropriate  $\mu$ M nanorod-toluene solution, and drying with N<sub>2</sub>. Once fabricated, the current through individual nanorod devices was characterized in a two-terminal geometry as a function of source-drain voltage and temperature. All data reported here were measured in a 10<sup>-6</sup> torr atmosphere with a Janis Research ST-500-2 micromanipulated probe station, chilled with liquid He or N<sub>2</sub> cryogen.

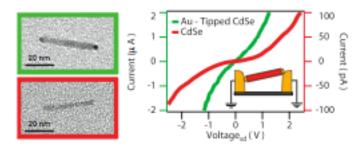

**Figure 1** TEM image of CdSe nanocrystal before (a) and after (b) Au tip growth. SEM image (c) and schematic (e) of single nanocrystal 2-terminal device. After submersing a silicon wafer test chip in a toluene-nanocrystal solution, the evaporating solvent orients individual nanocrystals across predefined Au electrodes fabricated via e-beam lithography. (d) Solution phase optical spectra indicate onset of first exciton absorption at 2 eV for both CdSe (red) and Au-tipped CdSe heterostructure (green) samples.

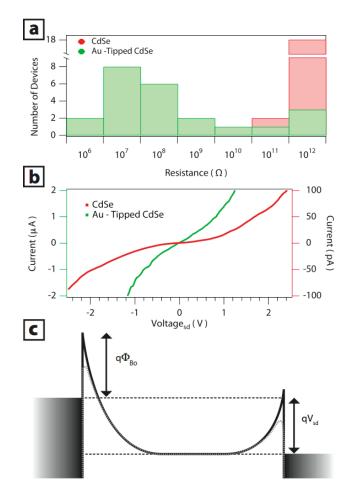

Characteristic room temperature electrical data of individual particles from this study are summarized for CdSe [red trace] and Au-tipped CdSe [green trace] nanocrystals in figure 2b. Devices made with Au-CdSe heterostructure nanocrystals display an average 6-decade increase in conductivity near zero applied bias (fig. 2a) compared to the control CdSe devices. This drastic improvement represents a lower limit for the enhancement the Au tip provides, as our experimental sensitivity was limited to resistance less than  $10^{13} \Omega$ .

Numerous studies report the conductivity of individual semiconductor nanostructures or estimate that value from the electrical response of thin film nanocrystal solids. The wide range of values in the literature confirms that conductance is highly sensitive to the semiconductor material, surface treatment and contact method. For II-VI semiconductors in particular, spin-cast CdSe nanocrystal thin films

without chemical surface treatments or annealing display almost no measurable conductance, greater than  $10^{14} \Omega$  cm resistivity or  $10^{20} \Omega$  resistance per nanocrystal.<sup>8</sup> When individual nanocrystals are contacted via evaporated metals, alloying and diffusion at the contact alters the semiconductor composition, complicating interpretation, though conductance is generally improved to give  $10^9 \Omega$ resistance per a CdTe nanorod.<sup>5</sup> In this study, because both measured device types consisted of a single CdSe nanocrystal contacted by Au, we propose that the factor that accounts for the stark difference in conductance is the alkylphosphonic acid surfactant layer bound to the pure nanocrystal surface.<sup>9</sup> This surfactant is not present at the Au-CdSe metal-semiconductor interface of the heterostructure nanocrystals. It is thus critical to understand how surface ligands influence interface electronic structure, and consequently overall device performance, which this report explores in detail.

**Figure 2** (a) Histogram of room temperature device resistance near 0 V applied bias. (b) Representative two-probe I-V trace of a CdSe device (red) and an Au-tipped CdSe device (green) at room temperature.

Note the color-coded axes correspond to pA (red) and  $\mu$ A (green) scales. (c) Simplified energy-band diagram of proposed barrier structure across a device under bias. The dashed grey line shows the barrier lowering due to the image potential, not drawn to scale.

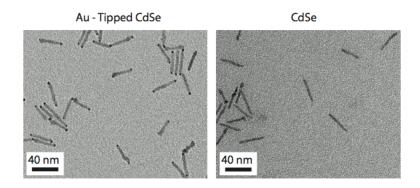

Ensemble TEM analysis [supplementary figure 1] indicates good monodispersity of the starting CdSe rods, with dimensions 4.8 ( $\pm$  0.8) by 32 ( $\pm$  5) nm. During synthesis of the heterostructures, the amount of precursor added was optimized for the desired degree of Au overgrowth to give spherical 3.4 ( $\pm$  0.8) nm diameter Au tips [fig 1b]. This treatment otherwise preserves the nanocrystal surface structure, so that surfactant coverage is identical along the walls of the nanorods both with and without Au tips.

The critical step of contacting individual nanocrystals to the lithographed electrodes also occurred via self-assembly. Individual nanorods spontaneously bridged the predefined junctions [fig. 1c] after submersion in a nanocrystal solution, placed there via the evaporating solvent front and likely oriented by the shrinking strand of solvent that minimized surface tension across the junction.<sup>10</sup> The technique is robust, with >75% junctions yielding working electrical devices confirmed by SEM. Control experiments with junctions submerged in pure toluene displayed no electrical response [supplementary figure 2]. Though we cannot confirm a single nanocrystal per junction in every device, due to the difficulty of imaging individual CdSe nanorods by SEM, the micrographs indicate we did not measure aggregates or ensembles of particles, and that both samples were present in similar surface concentrations near the junctions. Further, multiple particles in parallel across a junction would change the conductance by a multiplicative factor of the number of nanorods in parallel, which could not account for the several orders of magnitude increase observed here for the two different device types.

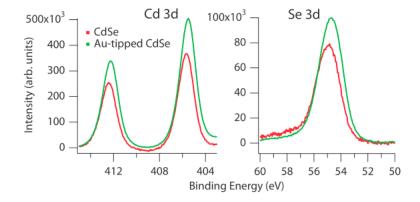

An alternative explanation for the enhancement in conductance of the Au-CdSe heterostructures could be that the Au tip growth method fundamentally alters the semiconducting region of the heterostructure, forming a conductive Au-Cd-Se alloy. However, this explanation is inconsistent with several lines of evidence. Previous studies<sup>11</sup> by High Resolution Transmission Electron Microscopy [HRTEM] of similarly prepared heterostructure nanocrystals indicate well defined lattice planes corresponding to CdSe and Au in the center and tips of the nanocrystal respectively, in intimate atomic contact. Cryogenic scanning tunneling microscopy [STM] measurements on individual heterostructures<sup>12</sup> corroborated these findings, reporting metallic conduction at the tips and an interior band structure corresponding to CdSe. In addition to these findings, in this study, X-ray photoelectron spectroscopy [XPS] measurements of spin-cast films identified insignificant chemical shift in the Cd or Se signals of the heterostructures [supplementary figure 3]. In addition, UV-Vis absorbance spectra of the two samples show an identical onset for the first exciton absorption at 2.0 eV (fig. 1d), indicating no clear difference in the composition of the semiconductor material in both nanostructures. Based on our measurements and the previous studies, clearly the CdSe region is not alloyed in the heterostructures. The sample purity is further confirmed by examination of the temperature dependence of the nanocrystal conductance.

Both samples in this study exhibit conductivity that is not monotonic with temperature, displaying a minimum conductance near 200K and a steady increase in conductance to the lowest and highest temperatures probed, from 4.2K to 400K. Across this temperature range the Au-tipped samples maintain conductance larger than the control CdSe samples, while both devices exhibit a similar trend in temperature dependence (fig. 3 and 4). However, the magnitude of the conductance enhancement has a strong temperature and voltage dependence, discussed fully below. In general, semiconductor conductivity is the product of carrier concentration and carrier mobility, with each parameter dependent on the thermal activation of free carriers or phonons respectively.<sup>13</sup> It is necessary to consider both contributions across different temperature device response (< 200K) suggests tunneling electrons traverse the nanocrystal via a pathway with resistance proportional to the temperature dependent phonon occupation. The high temperature behavior (> 250K) indicates a transport mechanism dominated by thermally activated carriers. In both temperature regimes we see evidence of a lowered conduction

barrier at the Au-CdSe interface of the heterostructures, which we correlate with the observed conductivity enhancement.

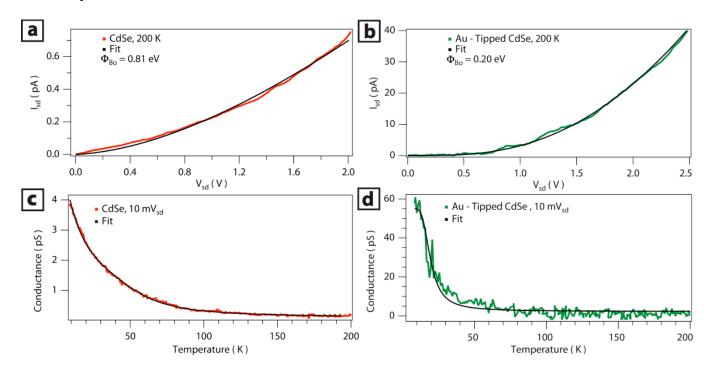

**Figure 3** Positive I-V trace of a CdSe device (a) and Au-CdSe heterostructure device (b) at 200K with fit (black) to eq. (1). The low bias conductance of a CdSe device (c) and an Au-CdSe heterostructure device (d) with fits to eq. (4) and eq. (3) respectively, reflect the contribution from the Einstein model for heat capacity.

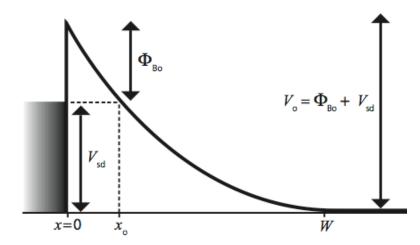

At low temperatures when the thermal activation of carriers is negligible, the current-voltage dependence of both samples suggests carriers tunnel onto the nanocrystal through a voltage-dependent contact barrier. Similar electrical response from individual colloidal CdSe nanocrystals was also observed by Gudinsken<sup>14</sup> and Steinberg<sup>15</sup>. Figure 2c diagrams a simplified proposed barrier structure across a biased nanocrystal device. The left barrier at the higher potential side has the limiting conductance that dominates the observed device response. The tunnel barrier width at the left electrode Fermi level decreases upon increasing bias and device response is symmetric under reverse polarity. The following expression derived in the supplemental gives the voltage-dependent tunneling current, I,

through such a barrier:

$$I = CV \cdot \exp\left(-2\sqrt{\frac{m\varepsilon_{\rm s}}{\hbar^2 N_{\rm D}}} \cdot \left[\sqrt{(V + \Phi_{\rm Bo})} \cdot \Phi_{\rm Bo} - V \cdot b\right] \quad \right) \tag{1}$$

with

$$b = \operatorname{ArcCosh}\left(\sqrt{\frac{V + \Phi_{Bo}}{V}}\right)$$

(2)

where  $\Phi_{Bo}$  is the barrier height,  $\varepsilon_s$ ,  $N_D$ , and *m* are the semiconductor permittivity, doping concentration, and effective mass of CdSe, and *C* is a wave function coupling constant of the electrode to the nanorod.

Figure 3a and 3b show the high quality of the least squares fit of the device response to equation (1) under positive bias at 200 K. Similar behavior is observed for samples under reverse bias and at lower temperature. The fit determines barrier heights of 0.81 eV for the CdSe device and 0.20 eV for the Autipped CdSe device. The lower barrier results in the improved conductance of the heterostructure devices. Further, the control CdSe device shows a two order of magnitude smaller coupling constant, C. Independent of applied bias, this lower coupling constant likely corresponds to an additional barrier between the electrode and the CdSe surface due to alkylphosphonic acid surfactant molecules. This barrier is not diagrammed in figure 2c. The fit also determines doping concentrations,  $N_{\rm D}$ , by assuming the bulk CdSe values for  $\varepsilon_s$ , and m.<sup>13</sup> For the Au-CdSe device in fig. 3,  $N_D = 4.4 \times 10^{18} \text{ cm}^{-3}$  and for the CdSe control device  $N_{\rm D} = 1.7 \text{ x } 10^{21} \text{ cm}^{-3}$ . We note that the model of Eq.(1) uses approximations of bulk geometry to solve Poisson's equation, with simplifications at high voltages, and ignores the effect of an image potential at the electrode interface. Further, the fit parameter containing these materials constants fluctuates over a large range of values during the fitting routine, complicating quantitative analysis. More sophisticated models that better account for the unique structure of the nanocrystal-electrode interface and contributions to current at large voltages will likely yield a more accurate fit. However, the barrier heights and doping concentration determined by this method are in good agreement with a high temperature thermal activation analysis. The high temperature analysis does not have the same limitations described here, and will be discussed more fully below.

We also plot the low temperature dependence of the low bias conductance for the same CdSe device (fig. 3c) and Au-CdSe heterostructure device (fig. 3d). The strong increase in conductance with lower temperature is clearly visible for both samples. This low temperature dependence is directly reflected in the temperature dependence of the coupling constant *C* in Eq.(1). This means that the wave function coupling between the electrode and both nanorod samples is reduced by inelastic scattering caused by phonon fluctuations. We propose that this reduction is directly proportional to the temperature-dependent occupation of phonons, as defined by the Einstein model<sup>16</sup> for heat capacity,  $C_V$ . The likelihood of inelastic phonon scattering depends on the number of available phonons. We model the low temperature, low bias resistance of the device,  $\Omega$ , also accounting for other in-series contributions,  $\Omega_{e_0}$ , to give

$$\Omega = \Omega_0 + \alpha C_V = G^{-1} \tag{3}$$

with

$$C_V = 3Nk_B \left(\frac{\theta_E}{T}\right)^2 \frac{e^{\theta_E/T}}{\left(e^{\theta_E/T} - 1\right)^2}$$

(4)

where  $\alpha$  is the proportionality constant, N is the number of oscillators in the solid,  $\theta_E$  is the Einstein temperature, a material-dependent fitting parameter related to the characteristic phonon frequency, and G is the low bias device conductance.

The least squares fit of equation (3) to the low temperature, low bias conductance of the Au-CdSe heterostructure device displayed in figure 3d shows that this proposed mechanism very accurately describes the trend. The fit also determines that  $\theta_E = 140\text{K} \pm 3\text{K}$ . We note that corrections to the Einstein heat capacity model are generally only significant below  $.1^*\theta_E$  or ~14K in this study, with the Debye T<sup>3</sup> Law only applicable up to a few degrees K, for example.<sup>16</sup> Figure 3c shows the low temperature, low bias conductance of the CdSe heterostructure device. The best fit to this data includes a linear temperature dependent term, *b*, to give:

$$\Omega = \Omega_0 + \alpha C_V + b T = G^{-1}$$

<sup>(5)</sup>

The high accuracy of the fit with this phenomenological correction suggests that a complete description requires consideration of other temperature dependent mechanisms for the CdSe device resistance ( $b = .01 \text{ T}\Omega/\text{K}$ ). Our analysis cannot distinguish if scattering from the surfactant shell or the semiconducting region contributes to the observed behavior. Future work will examine the role of surface treatments on the magnitude and specific temperature dependence of the trend.

At temperatures above 250K, we see strong evidence of a transport mechanism dominated by thermally activated charge carriers. Numerous scientific studies have determined that Au contacts to bulk CdSe form Schottky barriers.<sup>18</sup> In the absence of interface states, the ideal barrier height determined by these experiments is 800 meV, the difference of the work function of Au ( $\Phi_{m,Au} = 5.38$  eV) and the electron affinity of CdSe ( $\chi_{CdSe} = 4.58 \text{ eV}$ ).<sup>13, 18</sup> Considering the typical behavior at bulk Au-CdSe interfaces, and the contact barriers observed during the low temperature analysis above, our devices likely consist of a rectifying junction at each Au contact. For a particular bias polarity, the higher potential side limits the total current across the device. Indeed, a high temperature conduction mechanism of thermionic emission over a reverse-biased Schottky diode well describes our observed data. This mechanism results from same interface barrier diagramed in figure 2c, with electrons thermally activated over the barrier rather than tunneling through it, but with the inclusion of an image potential at the electrode that raises or lowers the barrier under forward or reverse bias, respectively. The super-linear current-voltage response (fig. 2b) results from barrier height lowering with increased bias because of the image force according to

$$I = AA^{**}T^2 \exp\left(\frac{-q\Phi_{\rm BE}}{k_{\rm B}T}\right)$$

(6)

where

$$\Phi_{\rm BE} = \Phi_{\rm Bo} - \sqrt{\frac{qE}{4\pi\varepsilon_{\rm S}}} \tag{7}$$

and

$$E = \sqrt{\frac{2qN_{\rm D}}{\varepsilon_{\rm S}} \left( V + \Phi_{\rm bi} - \frac{k_{\rm B}T}{q} \right)}$$

(8)

where *A* is the contact area,  $A^{**}$  is the effective Richardson constant,  $\Phi_{BE}$  is the effective barrier height,  $\Phi_{Bo}$  is the ideal barrier height in the absence of an image force, *E* is the maximum electric field at the junction,  $\varepsilon_s$  and  $N_D$  are the semiconductor permittivity and doping concentration of CdSe, and  $\Phi_{bi}$  is the built-in potential.<sup>13</sup> Importantly, these relations show that  $\ln(I)$  is linear with  $V^{4}$  in the limit of voltage greater than the built-in potential. Also, the slope of an activation energy plot of  $\ln(I/T^2)$  versus 1/Tgives the bias-dependent effective barrier height,  $\Phi_{BE}$ . This thermionic emission model is only valid at relatively high temperatures where  $A^{**}$  and  $\Phi_{BE}$  are temperature-independent, and other contributions to carrier mobility and concentration are negligible.

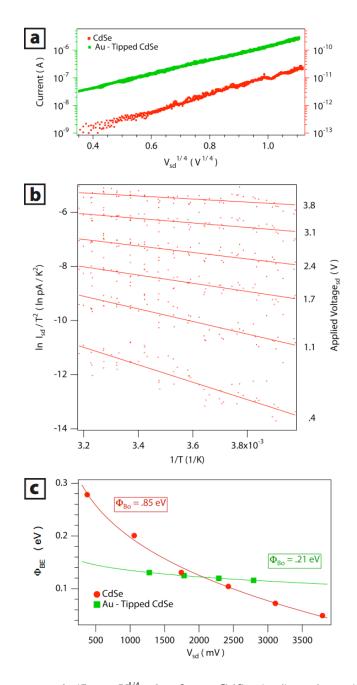

The linearity of the ln (*I*) versus  $V^{4}$  plots in figure 4a demonstrates the validity of the thermionic emission model description. We emphasize that an extensive examination of many of the other proposed mechanisms for transport in nanoscale semiconductors, including variable range hopping<sup>2</sup>, spacecharge-limited<sup>19</sup>, Fowler-Nordheim tunneling<sup>15</sup>, or single electron tunneling<sup>6</sup> did not describe the data as accurately as the standard thermionic emission model we propose. However, the devices necessarily deviated from the linear response displayed in Figure 4a at decreased temperatures, where the low temperature analysis discussed above is appropriate. It is likely in the high temperature range that the thermally activated carriers, especially at low bias, mask any background tunneling current.<sup>20</sup> The slope of the activation energy plot of  $\ln(I/T^{2})$  versus 1/T for a CdSe device at varying bias (fig. 4b) was used to determine the voltage dependence of the effective barrier height,  $\Phi_{BE}$ . These data are summarized for both device types in figure 4C. Here we see clear evidence of the bias-dependent barrier height lowering predicted by the thermionic emission model. Solving equations (7) and (8) for  $\Phi_{BE}$  gives

$$\Phi_{\rm BE} = \Phi_{\rm Bo} - \sqrt{\frac{q}{4\pi\varepsilon_{\rm S}}} \sqrt{\frac{2qN_{\rm D}}{\varepsilon_{\rm S}}} \left( V + \Phi_{\rm bi} - \frac{k_{\rm B}T}{q} \right)$$

(9)

The thermal energy,  $k_{\rm B}T$ , is small compared to V and  $\Phi_{\rm bi}$  allowing the simplification<sup>21</sup>  $\Phi_{\rm bi} = \Phi_{\rm Bo} - k_{\rm B}T$

$\ln(N_{\rm C}/N_{\rm D}) \approx \Phi_{\rm Bo}$  where  $N_{\rm C}$  is the effective conduction band density of states, to give

$$\Phi_{\rm BE} \cong \Phi_{\rm Bo} - \sqrt{\frac{q}{4\pi\varepsilon_{\rm S}}} \sqrt{\frac{2qN_{\rm D}}{\varepsilon_{\rm S}}} \left(V + \Phi_{\rm Bo}\right)$$

(10)

The least squares fit to equation (10) with  $\Phi_{Bo}$  as a free parameter is excellent (fig. 4c) with  $\Phi_{Bo} = 0.85$  eV and for the CdSe device and  $\Phi_{Bo} = 0.21$  eV for the Au-CdSe heterostructure device. These values are in excellent agreement with the low temperature tunneling fitting, where  $\Phi_{Bo} = 0.81$  eV and 0.20 eV are obtained for CdSe and Au-CdSe devices respectively.

Recall that  $\Phi_{Bo}$  is the ideal barrier height, with a predicted value of 800 meV for a bulk Au contact to CdSe free of surface or interface states. The control CdSe devices display a barrier very close to this value, giving good correspondence with the reported behavior at ideal bulk contacts despite that surfactant shell that likely remains on the nanocrystal. However the Au-CdSe heterostructure devices deviate from this value significantly, suggesting that interface structure drastically modifies the electronic environment at the contact. Specifically, our analysis shows a 75% decrease in the Schottky barrier of the Au-CdSe heterostructure device compared to the CdSe control device. Schottky barrier lowering resulting from induced mid gap states is well characterized at bulk Au-CdSe interfaces<sup>22</sup>, giving barrier heights highly dependent on contact structure. Similarly, we attribute the barrier decrease to electronic hybridization or induced mid-gap states at the electrode interface, which accommodate the charge redistribution due to Fermi level equilibration, for lower overall interface polarization. The decreased barrier at the Au-CdSe interface of the heterostructure nanocrystals gives rise to the large conductance enhancement observed for those devices.

**Figure 4** (a) Room temperature  $\ln(I)$  vs  $V^{1/4}$  plot for a CdSe (red) and an Au-CdSe heterostructure (green) device. The linear behavior is consistent with a thermionic emission model and was observed across devices above 250K. (b) Activation energy  $\ln(I/T^2)$  vs 1/T plot at several bias values for a CdSe device. The fitted slopes (solid traces) give the bias-dependent effective barrier height  $\Phi_{BE}$ , summarized in (c) for the same CdSe device (red circles) and an Au-CdSe heterostructure device (green squares). The fit in (c) to equation 5 (solid traces) shows the reduced barrier height  $\Phi_{Bo}$  at the Au-CdSe contact of the heterostructure device.

The fit to the data displayed in figure 4b and 4c must be interpreted with care. Our analysis follows from the solution to the Poisson equation conventionally employed to describe bulk semiconductormetal interfaces.<sup>13</sup> Although much recent experimental work<sup>21, 23, 24</sup> applied this model directly to nanoscale electrical devices, as we have here, theoretical treatments<sup>3,4</sup> suggest corrections to this picture may be required. In particular, there is little theoretical discussion of the impact of large surface-volume ratios and ligand shells on interfacial charge redistribution, especially for colloidal nanostructures as small as in this study. Indeed, if we assume bulk values for the CdSe semiconductor permittivity, the fit to equation (10) gives the seemingly unphysical prediction of less than one dopant per hybrid Au-CdSe nanocrystal,  $N_{\rm D} = 3.5 \times 10^{17}$  cm<sup>-3</sup>. For the CdSe control device in fig. 4,  $N_{\rm D} = 1.3 \times 10^{21}$  cm<sup>-3</sup>, a more reasonable carrier concentration. Also note that a factor of 10 larger doping concentration is obtained for the Au-CdSe nanocrystal compared to the low temperature tunneling current fit, while the CdSe nanocrystal dopant concentration is very similar to the low temperature fit. Besides the approximations mentioned above, one possible reason for this discrepancy between fits is that the tunneling formula of Eq.(1) does not consider the image potential. If the image effect were also included in the low temperature model, the fit would determine a lower barrier height, giving a smaller value of  $N_{\rm D}$ . The barrier reduction is more significant in the low barrier case of an Au-CdSe device, thus it has a smaller effect on the fitted dopant concentration at a larger barrier, as in a CdSe control device.

A possible explanation for the apparently low dopant concentration in the Au-CdSe device is that the actual dopants are localized at the surface, not inside the rod as the bulk formula assumes. The decharging of these dopant sites causes the depletion layer and contributes to the potential barrier lowering. If the dopant sites are located at the surface, and the depletion layer length is similar to the rod diameter, then the ability of de-charging to lower the potential at the center of the rod, where the majority of current flows, is less efficient. Accounting for this would be similar to including a large effective screening constant in the fitting formula, leading to a much larger and more reasonable  $N_{\rm p}$ , or

the equivalent surface doping concentration. The fitted depletion length, W, by eq. (S2) gives W = 7nm for the Au-CdSe device, consistent with this interpretation. The fitted doping concentration for the CdSe device is much larger than for the Au-CdSe device. Here again, it is possible that the device exhibits behavior due to de-charging of the surfactant related surface states at the tip of the rod. These states are directly in the current path, and thus very effective for lowering the potential, giving an apparently large  $N_{\rm D}$ . Despite these complications, a key feature of the thermionic emission model fit to determine the barrier height, as in figure 4, is that it requires no assumptions about material constants, doping concentration, or other parameters at the complex electrode interface.

In summary, we provide direct measurement of the effect of surfactant on a semiconductor nanocrystal surface and at a metal-semiconductor hybrid interface. We show that the superior performance of Au-tipped heterostructures results from a lower Schottky barrier, and that the synthetic method for tip growth does not alter the chemical composition of the semiconductor. Further, our work demonstrates the increasing sophistication of high quality electrical devices achievable via self-assembly, and verifies this process as an excellent route to the next generation electronic and optoelectronic devices utilizing colloidal nanocrystals.

ACKNOWLEDGMENT We thank the UC Berkeley Microfabrication Laboratory for use of their facility. M.S. thanks the Center of Integrated Nanomechanical Systems for a fellowship (Grant No. 0425914). P.-E.T. thanks Canada's National Science and Engineering Research Council for a fellowship. SEM work was performed at the Imaging and Manipulation Facility of the Molecular Foundry, Lawrence Berkeley National Laboratory, and all other work was funded by the Helios Solar Energy Research Center. Both facilities are supported by the Office of Science, Office of Basic Energy Sciences, U.S. Department of Energy, under Contract No. DE-AC02-05CH11231.

**Supporting Information Available**. Additional TEM, XPS data, control experiments, and derivation of equation (1). This material is available free of charge via the internet.

#### REFERENCES

1. Grabert, H.; Devoret, M. H., Single Charge Tunneling, Coulomb Blockade Phenomena in Nanostructures. Plenum Press: New York, 1992; Vol. 294.

2. Houtepen, A.; Kockmann, D.; Vanmaekelbergh, D., Reappraisal of Variable-Range Hopping in Quantum-Dot Solids. *Nano Letters* **2008**, 8, (10), 3516-3520.

3. Léonard, F.; Talin, A., Size-Dependent Effects on Electrical Contacts to Nanotubes and Nanowires. *Phys. Rev. Lett.* **2006**, 97, (2), 4.

4. Landman, U.; Barnett, R. N.; Scherbakov, A. G.; Avouris, P., Metal-semiconductor nanocontacts: Silicon nanowires. *Phys. Rev. Lett.* **2000**, 85, (9), 1958-1961

5. Trudeau, P. E.; Sheldon, M.; Altoe, V.; Alivisatos, A. P., Electrical Contacts to Individual Colloidal Semiconductor Nanorods. *Nano Lett* **2008**, 8, (7), 1936-1939.

6. Klein, D.; Roth, R.; Lim, A.; Alivisatos, A.; McEuen, P., A single-electron transistor made from a cadmium selenide nanocrystal. *Nature* **1997**, 389, (6652), 699-700.

7. Banin, U.; Millo, O., TUNNELING AND OPTICAL SPECTROSCOPY OF SEMICONDUCTOR NANOCRYSTALS. *Annu. Rev. Phys. Chem.* **2003**, 54, (1), 465-492.

8. Mokari, T., Selective Growth of Metal Tips onto Semiconductor Quantum Rods and Tetrapods. *Science* **2004**, 304, (5678), 1787-1790.

9. Morgan, N.; Leatherdale, C.; Drndić, M.; Jarosz, M.; Kastner, M.; Bawendi, M., Electronic transport in films of colloidal CdSe nanocrystals. *Phys. Rev. B* **2002**, 66, (7), 9.

10. Alivisatos, A., Perspectives on the Physical Chemistry of Semiconductor Nanocrystals. *J. Phys. Chem.* **1996**, 100, (31), 13226-13239.

11. Liddle, J. A.; Cui, Y.; Alivisatos, P., Lithographically directed self-assembly of nanostructures. *Journal of Vacuum Science & Technology B: Microelectronics* ... **2004**.

12. Steiner, D.; Mokari, T.; Banin, U.; Millo, O., Electronic Structure of Metal-Semiconductor Nanojunctions in Gold CdSe Nanodumbbells. *Phys. Rev. Lett.* **2005**, 95, (5), 4.

13. Sze, S. M., Physics of Semiconductor Devices. 2nd ed.; John Wiley & Sons: New York, 1981.

14. Gudiksen, M. S.; Maher, K. N.; Ouyang, L.; Park, H., Electroluminescence from a singlenanocrystal transistor. In *Nano Lett*, 2005; Vol. 5, pp 2257-2261.

15. Steinberg, H.; Lilach, Y.; Salant, A.; Wolf, O.; Faust, A.; Millo, O.; Banin, U., Anamolous temperature dependent transport through single colloidl nanorods wired using electron beam induced deposition. *to be submitted* **2009**.

16. Kittel, C., Introduction to solid state physics. 7th ed.; John Wiley & Sons: New York, 1996.

17. Brillson, L. J., Interface bonding, chemical reactions, and defect formation at metalsemiconductor interfaces. In *J Vac Sci Technol A*, 2007; Vol. 25, pp 943-949.

18. Talin, A.; Léonard, F.; Swartzentruber, B.; Wang, X.; Hersee, S., Unusually Strong Space-Charge-Limited Current in Thin Wires. *Phys. Rev. Lett.* **2008**, 101, (7), 1-4.

19. Zhang, Z.; Jin, C.; Liang, X.; Chen, Q.; Peng, L., Current-voltage characteristics and parameter retrieval of semiconducting nanowires. *Applied Physics Letters* **2006**, 88, (7), 073102.

20. Nam, C. Y.; Tham, D.; Fischer, J. E., Disorder effects in focused-lon-beam-deposited pt contacts on GaN nanowires. In *Nano Lett*, 2005; Vol. 5, pp 2029-2033.

21. Monch, W., Electronic Properties of Semicondcutor Interfaces. Springer-Verlag: Berlin, 2004.

22. Lin, Y.; Jian, W., The Impact of Nanocontact on Nanowire Based Nanoelectronics. In *Nano Lett*, 2008; Vol. 8, pp 3146-3150.

23. Tarancon, A.; Casals, O.; Pellicer, E.; Rodriguez, J., Electrical properties of individual tin oxide nanowires contacted to platinum electrodes. *Physical Review B* **2007**.

#### TABLE OF CONTENTS FIGURE

### **Supplementary Information**

# Enhanced semiconductor nanocrystal conductance via solution grown contacts

Matthew T. Sheldon<sup>1</sup>, Paul-Emile Trudeau<sup>1</sup>, Taleb Mokari<sup>2</sup>, Lin-Wang Wang<sup>3</sup>, and A.Paul Alivisatos<sup>1,4</sup>\*

- 1. University of California, Berkeley, California 94720, USA

- 2. Molecular Foundry, Materials Sciences Division, Lawrence Berkeley National Laboratory

- 3. Computational Research Division, Lawrence Berkeley National Laboratory

4. Lawrence Berkeley National Laboratory, Berkeley, California 94720, USA

\*alivis@uclink4.berkeley.edu

Supplementary Figure 1: Ensemble transmission electron microscopy [TEM] Statistical analysis of micrographs like those above displaying Au-tipped CdSe nanorods (left) and control CdSe nanorods (right) indicate good sample monodispersity. The nanorods have dimensions 4.8 (± 0.8) by 32 (± 5) nm with 3.4 (± 0.8) nm diameter Au spheres after tip growth.

**Supplementary Figure 2: X-ray photoelectron spectroscopy** The Cd 3d signal (left) and Se 3d signal (right) for an ensemble of CdSe nanorods (red) and Au-tipped CdSe nanorods (green) show no significant difference in binding energy. A peak shift or broadening of ~2 eV would indicate a change in the oxidation state or chemical environment of the Cd or Se atoms present in the Au-tipped CdSe sample.

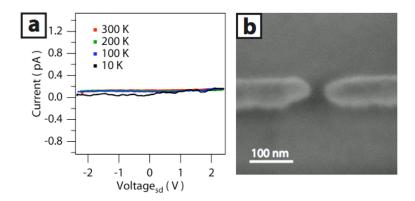

Supplementary Figure 3: Background current of an empty Au junction (a) There is no current response from an Au junction without a nanorod present, across the temperature range of our study. (b) Scanning electron micrograph [SEM] of a device with no nanorods.

#### Derivation of Equation (1)

The procedure follows from the general strategy outlined by Sze, with the barrier structure diagramed below. Electrons tunnel from left to right under bias.

$N_{\rm D}$  = doping density

- $\varepsilon_{\rm s}$  = semiconductor permittivity

- q = elementary charge

W = depletion width

m = effective mass

Poisson's equation defines the potential as a function of distance from the electrode, x, in terms of the voltage across the contact  $V_o$  (=V<sub>sd</sub>+ $\Phi_0$ )

$$V(x) = \frac{q}{2\varepsilon_{\rm s}} N_{\rm D} (W - x)^2 \tag{S1}$$

where

$$W = \sqrt{\frac{2\varepsilon_{\rm s} V_{\rm o}}{q N_{\rm D}}}$$

(S2)

and

$$x_{o} = W - \sqrt{\frac{2\varepsilon_{s}}{4\pi q N_{D}} V_{sd}}$$

(S3)

The overall current due to tunneling will be equal to:

$$I_{\rm sd} \propto V_{\rm sd} \cdot e^{-2\Gamma} \tag{S4}$$

where  $\Gamma$  is the tunneling phase factor:

$$\Gamma = \int_{0}^{x_{o}} k(x) dx = \int_{0}^{x_{o}} \sqrt{\frac{2mq}{\hbar^{2}} \left[\frac{4\pi q N_{\rm D}}{2\varepsilon_{\rm s}} \left(W - x\right)^{2} - V_{\rm sd}\right]} dx$$

(S5)

with the definition for the electron wave vector:

$$k(x) = \sqrt{\frac{2mq}{\hbar^2} \left( V(x) - V_{\rm sd} \right)}$$

(S6)

The integral in equation (S5) can be solved by substitution, note that:

$$\int_{1}^{a} \sqrt{y^{2} - 1} \, dy = \frac{1}{2} \left( a \sqrt{a^{2} - 1} - b \right) \text{ where } b = \operatorname{ArcCosh}(a) \tag{S7}$$

then

$$\Gamma = \sqrt{\frac{4m\varepsilon_{\rm s}V_{\rm sd}^2}{4\pi\hbar^2 N_{\rm D}}} \int_{1}^{V_{\rm o}/V_{\rm sd}} \sqrt{y^2 - 1} dy$$

(S8)

giving

$$\Gamma = \sqrt{\frac{m\varepsilon_{\rm s}}{\hbar^2 N_{\rm D}}} \cdot \left[ \sqrt{\left(V_{\rm sd} + \Phi_{\rm o}\right) \cdot \Phi_{\rm o}} - V_{\rm sd} \cdot \operatorname{ArcCosh}\left(\sqrt{\frac{V_{\rm o}}{V_{\rm sd}}}\right) \right]$$

(S9)

Substitution of equation (S9) for  $\Gamma$  into equation (S4) reproduces the expression for the tunneling current, equation (1), in the main body of the text.

DISCLAIMER: This document was prepared as an account of work sponsored by the United States Government. While this document is believed to contain correct information, neither the United States Government nor any agency thereof, nor The Regents of the University of California, nor any of their employees, makes any warranty, express or implied, or assumes any legal responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by its trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or The Regents of the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof or The Regents of the University of California.