# On the Design of Reversible QDCA Systems

Sarah E. Frost-Murphy, Marco Ottavi, Michael P. Frank, and Erik P. DeBenedictis

Prepared by Sandia National Laboratories Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy's National Nuclear Security Administration under Contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831

| Telephone:       | (865) 576-8401             |

|------------------|----------------------------|

| Facsimile:       | (865) 576-5728             |

| E-Mail:          | reports@adonis.osti.gov    |

| Online ordering: | http://www.osti.gov/bridge |

Available to the public from U.S. Department of Commerce National Technical Information Service 5285 Port Royal Rd. Springfield, VA 22161

| Telephone:    | (800) 553-6847                                             |

|---------------|------------------------------------------------------------|

| Facsimile:    | (703) 605-6900                                             |

| E-Mail:       | orders@ntis.fedworld.gov                                   |

| Online order: | http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online |

SAND2006-5990 Unlimited Release Printed October 2006

## On the Design of Reversible QDCA Systems

S.E. Frost-Murphy University of Notre Dame Notre Dame, IN 46556, and Multiscale Computational Materials Methods Department

> M. Ottavi Scalable Computing Systems Department

> > M.P. Frank Florida State University Tallahassee, FL 32310

E.P. DeBenedictis Scalable Computing Systems Department

> Sandia National Laboratories P.O. Box 5800 Albuquerque, NM 87185

#### Abstract

This work is the first to describe how to go about designing a reversible QDCA system. The design space is substantial, and there are many questions that a designer needs to answer before beginning to design. This document begins to explicate the tradeoffs and assumptions that need to be made and offers a range of approaches as starting points and examples. This design guide is an effective tool for aiding designers in creating the best quality QDCA implementation for a system.

## Contents

| Pr       | reface                                                               | 14 |

|----------|----------------------------------------------------------------------|----|

|          | Implementation Technology                                            | 14 |

|          | Logic (Reversibility) Schema                                         | 14 |

|          | Fault Tolerance                                                      | 15 |

| 1        | Introduction to QDCA                                                 | 17 |

|          | The Problem                                                          | 17 |

|          | Brief Introduction to Reversible Computing                           | 18 |

|          | A Computer Architect's Introduction to Quantum-dot Cellular Automata | 19 |

|          | Prior QDCA Architecture Work                                         | 22 |

|          | The Real Device                                                      | 23 |

|          | Original Contributions                                               | 24 |

|          | Organization                                                         | 24 |

| <b>2</b> | Physical Properties                                                  | 25 |

|          | Kink Energy                                                          | 25 |

|          | Gain                                                                 | 26 |

|          | Parameters for Conway-Mead Type Design Rules                         | 27 |

|          | Adiabaticity: A Case Study                                           | 31 |

|          | Solution of Differential Equation                                    | 34 |

| 3        | Clock Schemes                                                        | 37 |

|          | Clocking Details                                                     | 37 |

|          | Before Design                                                                | 37 |

|----------|------------------------------------------------------------------------------|----|

|          | Floorplanning Approaches                                                     | 37 |

|          | Clock Signal Approaches                                                      | 38 |

|          | Clocking Strategies                                                          | 38 |

|          | Landauer                                                                     | 38 |

|          | Retractile Cascade                                                           | 39 |

|          | Bi-directional Shift (aka Pulse)                                             | 40 |

|          | Uni-directional Bennett                                                      | 41 |

|          | No Clocking                                                                  | 47 |

|          | Summary                                                                      | 47 |

| 4        | Clock Circuit Issues                                                         | 49 |

|          | Overview on clock distribution circuit for QDCA                              | 49 |

|          | Capacitive coupling                                                          | 50 |

|          | Capacitive coupling with the neighboring wires                               | 50 |

|          | Capacitive coupling with the ground plane and dissipative effects $\ldots$ . | 53 |

|          | Resonant RLC circuit for low power clock distribution                        | 53 |

|          | Parallel load effect                                                         | 56 |

|          | Evaluations                                                                  | 56 |

|          | Conclusion                                                                   | 60 |

| <b>5</b> | QDCA Circuit Design                                                          | 61 |

|          | Circuit Design Strategies                                                    | 63 |

|          | Uni-directional Irreversible                                                 | 63 |

|          | Uni-directional Gate Level Reversible                                        | 63 |

|          | Uni-directional Sub-gate Level Reversible                                    | 64 |

|          | Bi-directional Gate Level Reversible                                         | 64 |

|   | Bi-directional Sub-Gate Level Reversible     | 65  |

|---|----------------------------------------------|-----|

|   | Matching Circuit and Clocking Strategies     | 66  |

|   | Special Concerns for Reversible Circuits     | 68  |

| 6 | Architectural Approaches                     | 73  |

|   | Retractile Cascade Fully Reversible Pipeline | 74  |

|   | Throughput                                   | 76  |

|   | Number of Unique Clock Signals Required      | 77  |

|   | Mirror Circuit Fully Reversible Pipeline     | 79  |

|   | Collapsed Bennett                            | 81  |

|   | Partially Reversible Pipeline                | 83  |

|   | Computation Stages                           | 85  |

|   | Memory Stages                                | 88  |

|   | Performance evaluation                       | 89  |

|   | Case Study: parity checker XOR tree          | 92  |

|   | Discussion                                   | 98  |

|   | Summary                                      | 98  |

| 7 | Conclusion 1                                 | 101 |

References

# List of Figures

| 1   | Exemplary Hierarchical Composition of Logic Schema                                                                                                                                                                                                         | 15 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | QDCA Cell (a) Polarization and corresponding logic values, (b) Signal propagation in QDCA. The cell on the left is polarized, the cell on the right is unpolarized. The cell on the right transitions to assume the polarization of the driving left cell. | 19 |

| 1.2 | Fine wires near the QDCA layer create the clocking fields. Thicker wires distribute the clocking signals to the fine wires                                                                                                                                 | 20 |

| 1.3 | Propagation of clock signal in a single cell through time                                                                                                                                                                                                  | 20 |

| 1.4 | Shaded boxes indicate clocking zones. a) 90 degree cells forming a "wire". b) 45 degree cells forming a wire                                                                                                                                               | 21 |

| 1.5 | Wire crossover                                                                                                                                                                                                                                             | 21 |

| 1.6 | a) Three-input Majority Gate, b) Inverter, c) AND gate d) OR gate                                                                                                                                                                                          | 22 |

| 2.1 | Considered sizes of Cell                                                                                                                                                                                                                                   | 25 |

| 2.2 | Kink Energy: (a) Ground State (b) Excited state                                                                                                                                                                                                            | 26 |

| 3.1 | Example of a zone floorplanned circuit. This clocking zone layout is from a reversible crossover circuit. Notice that small zones abut each other on both the $x$ and $y$ dimensions                                                                       | 38 |

| 3.2 | Zone Clocking: Entire regions rise and fall together. Here, a simple set of clocking zones computes from left to right.                                                                                                                                    | 39 |

| 3.3 | Example of a zone clocked circuit. This clocking zone layout is from a reversible crossover circuit. Notice that small zones abut each other on both the $x$ and $y$ dimensions                                                                            | 40 |

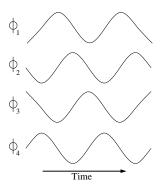

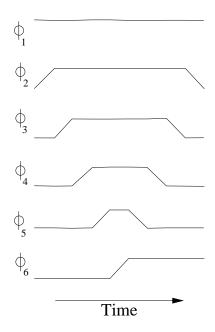

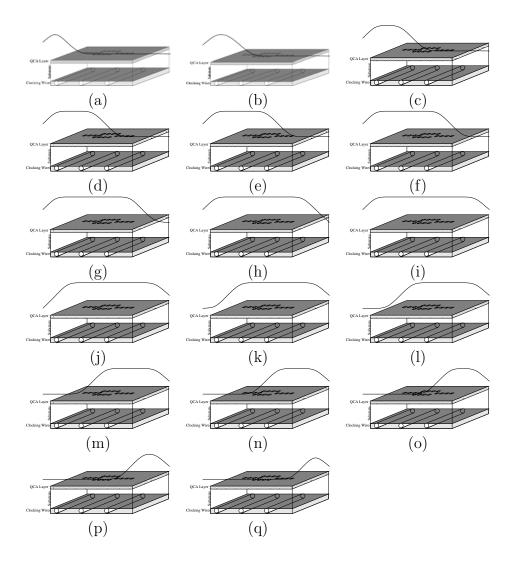

| 3.4 | Example of wave forms generated by each clocking wire for a four phase wave-style clock signal. This corresponds to a Landauer type clocking signal as in figure 3.6                                                                                       | 41 |

| 3.5 | Example of wave forms generated by each clocking wire for a zone-style clock signal. This corresponds to a clocking signal as in figure 3.2                                                                                                                | 41 |

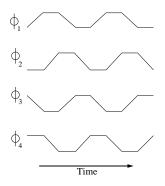

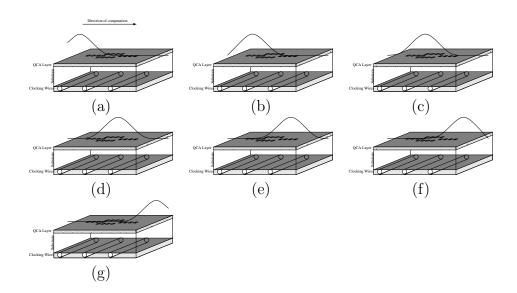

| 3.6                                                                                                   | Landauer Clocking: Computation proceeds from left to right. Data is<br>latched at each peak. Computation occurs on the rising edge (to the<br>right of each peak) as the wave moves to the right                                           | 42                                                                                 |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

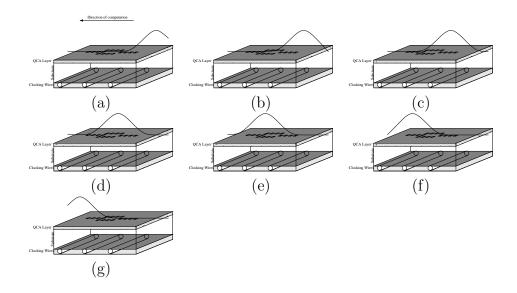

| 3.7                                                                                                   | Retractile Cascade Clocking: Computation proceeds from left to right.<br>Data is latched and remains latched until the result has been latched at<br>the right. The clock is then retracted until only the input and output<br>are latched | 42                                                                                 |

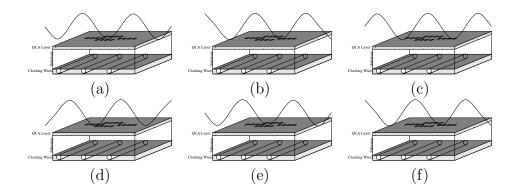

| 3.8                                                                                                   | Example of wave forms needed to generate retractile cascade, or Bennett, clocking.                                                                                                                                                         | 43                                                                                 |

| 3.9                                                                                                   | Bi-directional Shift: Shift Right                                                                                                                                                                                                          | 43                                                                                 |

| 3.10                                                                                                  | Bi-directional Shift: Shift Left                                                                                                                                                                                                           | 44                                                                                 |

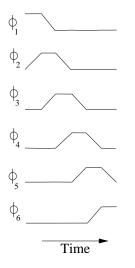

| 3.11                                                                                                  | Example of wave forms needed to generate the bi-directional shift to the right                                                                                                                                                             | 44                                                                                 |

| 3.12                                                                                                  | Uni-directional Bennett                                                                                                                                                                                                                    | 45                                                                                 |

| 3.13                                                                                                  | Example of wave forms needed to generate uni-directional Bennett clocking.                                                                                                                                                                 | 47                                                                                 |

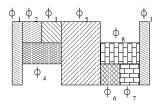

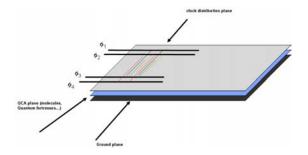

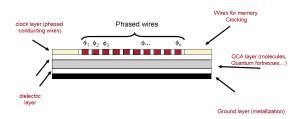

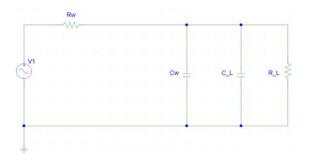

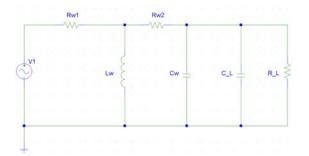

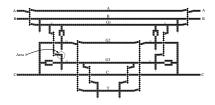

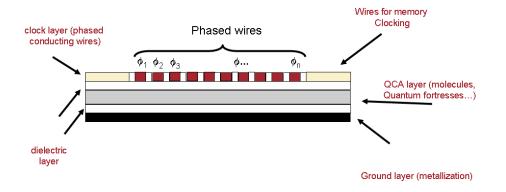

| 4.1                                                                                                   | Possible clock distribution circuitry for QDCA                                                                                                                                                                                             | 50                                                                                 |

|                                                                                                       |                                                                                                                                                                                                                                            |                                                                                    |

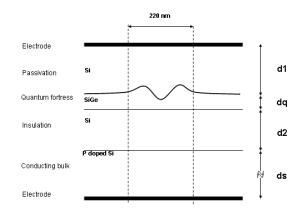

| 4.2                                                                                                   | Cross Section of a generic QDCA implementation                                                                                                                                                                                             | 50                                                                                 |

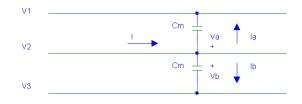

| 4.2<br>4.3                                                                                            | Cross Section of a generic QDCA implementation<br>Parasitic coupling with neighbor wires                                                                                                                                                   |                                                                                    |

|                                                                                                       |                                                                                                                                                                                                                                            |                                                                                    |

| 4.3<br>4.4                                                                                            | Parasitic coupling with neighbor wires                                                                                                                                                                                                     | 51<br>54                                                                           |

| 4.3<br>4.4                                                                                            | Parasitic coupling with neighbor wires                                                                                                                                                                                                     | 51<br>54<br>54                                                                     |

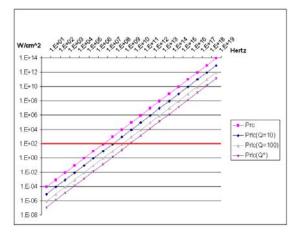

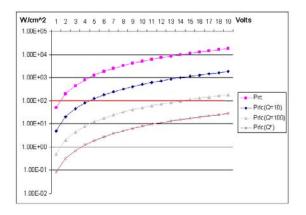

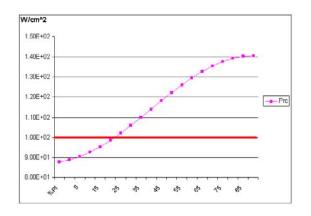

| <ul><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                                         | Parasitic coupling with neighbor wires                                                                                                                                                                                                     | 51<br>54<br>54<br>57                                                               |

| <ol> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ol>                                        | Parasitic coupling with neighbor wires                                                                                                                                                                                                     | 51<br>54<br>54<br>57                                                               |

| <ol> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ol>                           | Parasitic coupling with neighbor wires                                                                                                                                                                                                     | 51<br>54<br>54<br>57<br>57                                                         |

| <ol> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ol> | Parasitic coupling with neighbor wires                                                                                                                                                                                                     | <ul> <li>51</li> <li>54</li> <li>54</li> <li>57</li> <li>57</li> <li>59</li> </ul> |

| 5.2 | The basic fan-out circuit is an example of a uni-directional circuit that |    |

|-----|---------------------------------------------------------------------------|----|

|     | is reversible at the sub-gate level but is not bidirectional              | 64 |

- 5.3 QDCA layout of an example of a bi-directional circuit that is reversible at the whole-gate level. This is one implementation of a Toffoli gate. . . 65

- 5.4 Schematic of an example of a bi-directional circuit that is reversible at the whole-gate level. This is one implementation of a Toffoli gate..... 65

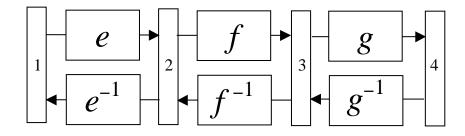

| 6.1 | Bidirectional-retractile scheme for reversible pipelining invented by<br>Younis and Knight. The vertical rectangles represent pipeline regis-<br>ters. The labels $e, f,$ and $g$ represent reversible functions; this partic-<br>ular pipeline is intended for computing the overall function $g \circ f \circ e$ , or<br>its inverse, depending on which direction it is operated in. The boxes<br>represent retractile circuits for computing the functions shown, where<br>the direction from inputs to outputs is indicated by the arrows. The<br>normal sequence of operation is as follows. Assume that block $e$ has<br>just produced its output, which has been latched into pipeline stage<br>2. Now, the complete cycle until new input arrives on stage 2 is as<br>follows. (1) $f$ is operated in the forwards direction, and meanwhile, $e$<br>is retracted, and $e^{-1}$ is operated. (2) $f$ 's output is latched into stage 3,<br>and meanwhile, the contents of stage 1 are unlatched reversibly under<br>control of $e^{-1}$ . (3) $g$ is operated in the forwards direction, while $f$ is<br>retracted, reversibly clearing its contents, and $f^{-1}$ is operated, resup-<br>plying an image of stage 2's contents, and $e^{-1}$ is retracted. (4) The<br>stage 2 contents are unlatched reversibly under control of $f^{-1}$ , and the<br>stage 4 contents are latched. Now stage 2 is empty and stage 4 contains<br>valid data. Meanwhile, stage 1 is being written with a new valid input.<br>(5) $e$ is charged, $g$ discharged, $g^{-1}$ charged, (6) stage 2 is charged, stage<br>3 discharged. After this we are back to the initial conditions and can<br>begin a new cycle | 75 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

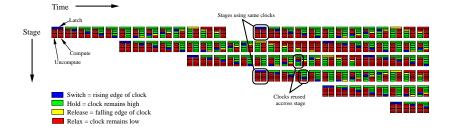

| 6.2 | Four-step timing sequence for bidirectional pipeline. Notice the latency<br>is only 1 tick per stage. This design requires 12 distinct clocks (12 types<br>of clocking regions). For this design to work, it must be possible to<br>adiabatically charge up the logic region and the pipeline register within<br>a single transition time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76 |

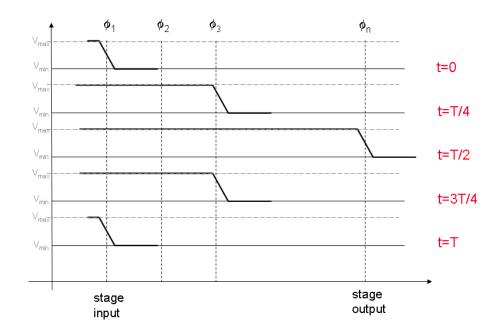

| 6.3 | Clocking signals needed for a pipeline with a compute phase with four clocking wires. Notice that sets of clocking signals can be repeated in whole between stages (e.g. at time 16 between stages 1 and 4) and across stages such as between the uncompute section of stage i and the compute section of stage i+1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 78 |

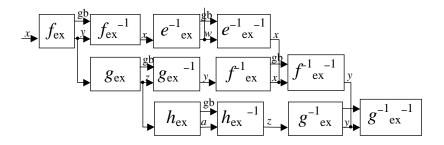

| 6.4 | Reversible pipeline based on mirror circuits. The structure is optimized to minimize latency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79 |

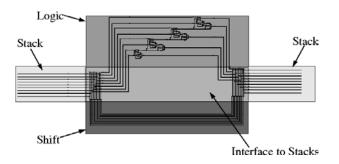

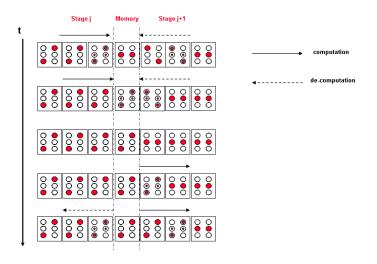

| 6.5 | Bennett's algorithm divides an algorithm into stages (8 stages in this example) and selectively computes and decomputes them to store the least amount of data necessary to maintain the reversibility of an irreversible algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81 |

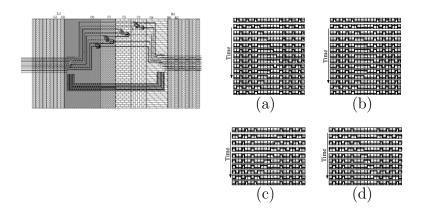

| 6.6  | The regions of the collapsed Bennett layout include two stacks, a logic<br>or computational area, a shift area that allows data to be transferred<br>between the stacks, and an interface between the stacks and the logic<br>and shift regions | 82 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

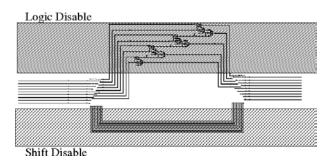

| 6.7  | There are two disable sections in this layout. The top area disables<br>the logic, while the bottom area disables the shift. While disabled, the<br>QDCA cells have no value and do not contribute to the computation<br>of any nearby cells    | 83 |

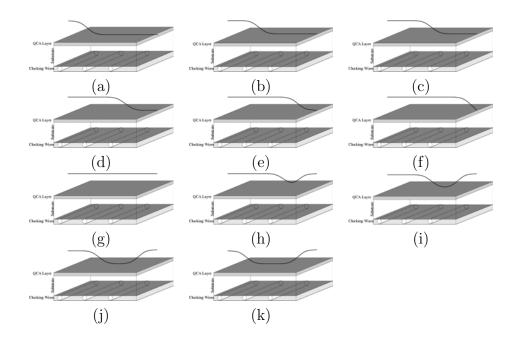

| 6.8  | Clocking signals required for four modes of operation of collapsed Ben-<br>nett clocking layout: (a) Compute, (b) UnCompute, (c) Shift Left, (d)<br>Shift Right                                                                                 | 83 |

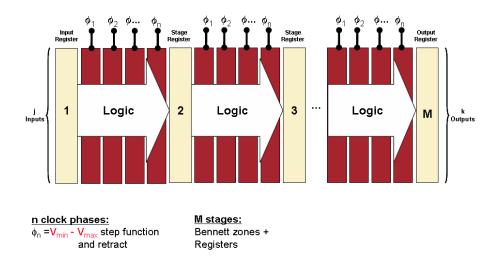

| 6.9  | Proposed pipelined approach: Top view                                                                                                                                                                                                           | 84 |

| 6.10 | Proposed pipelined approach: Cross Section                                                                                                                                                                                                      | 84 |

| 6.11 | Advantages of Bennett clocking: area and power consumption                                                                                                                                                                                      | 87 |

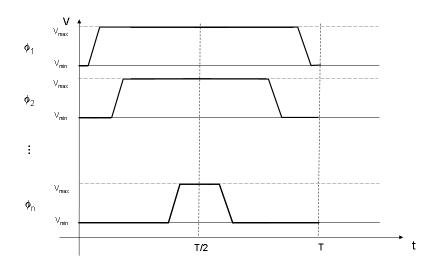

| 6.12 | Clocking wave for the Bennett scheme                                                                                                                                                                                                            | 87 |

| 6.13 | Clock signal to the buried wires                                                                                                                                                                                                                | 88 |

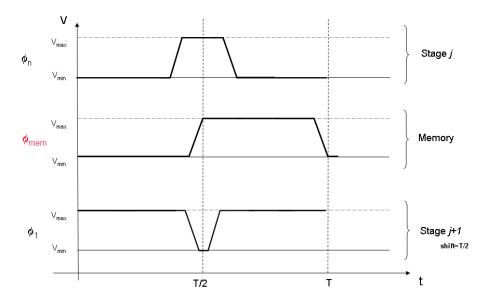

| 6.14 | Clocking signal for the memory zones                                                                                                                                                                                                            | 89 |

| 6.15 | Asymmetric interaction on the memory cell                                                                                                                                                                                                       | 90 |

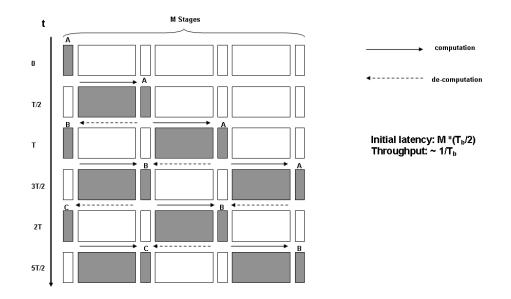

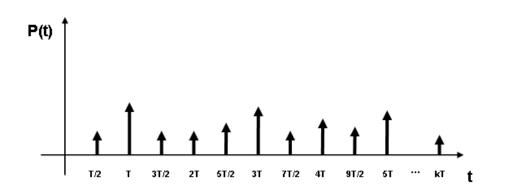

| 6.16 | Pipelined stages with Bennett clocking                                                                                                                                                                                                          | 91 |

| 6.17 | Possible shape of $P(t)$                                                                                                                                                                                                                        | 91 |

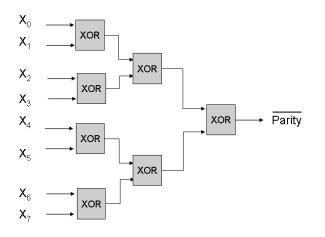

| 6.18 | Case Study: XOR tree parity checker                                                                                                                                                                                                             | 92 |

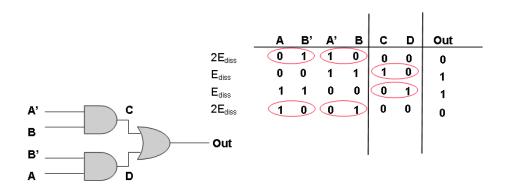

| 6.19 | Dissipation in the XOR gate                                                                                                                                                                                                                     | 93 |

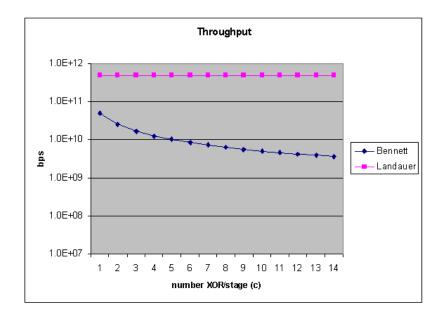

| 6.20 | Throughput comparison                                                                                                                                                                                                                           | 95 |

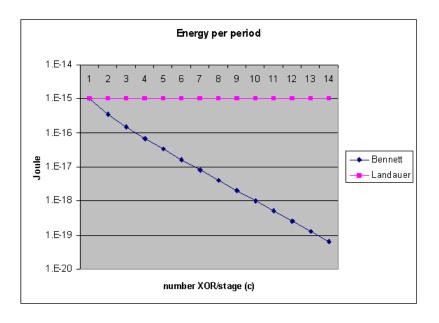

| 6.21 | Comparison of Energy dissipation per period                                                                                                                                                                                                     | 96 |

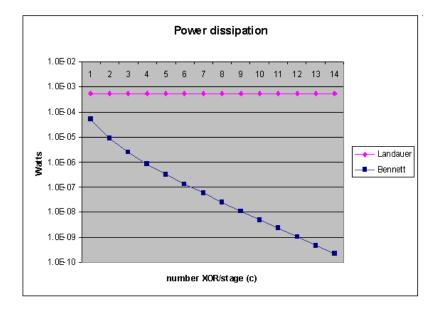

| 6.22 | Comparison of Power dissipation                                                                                                                                                                                                                 | 96 |

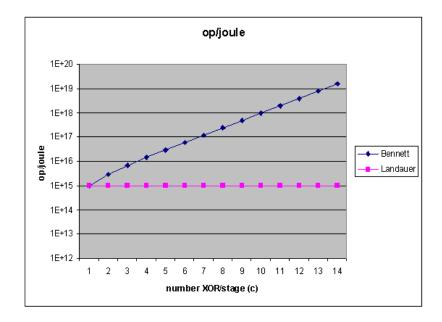

| 6.23 | Comparison of operations per joule                                                                                                                                                                                                              | 97 |

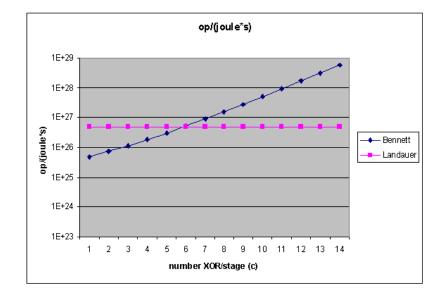

| 6.24 | Comparison of operations per joule per second                                                                                                                                                                                                   | 97 |

## List of Tables

| 1.1 | Truth Table of AND Operation                                        | 18  |

|-----|---------------------------------------------------------------------|-----|

| 2.1 | Niemier's Molecular QDCA Design Rules                               | 30  |

| 3.1 | Comparison of Clocking Strategies                                   | 46  |

| 4.1 | Physical parameters                                                 | 58  |

| 4.2 | Circuit parameters                                                  | 58  |

| 5.1 | Questions Before Design                                             | 62  |

| 5.2 | Reversibility of Circuit Design Strategies and Clocking Strategies  | 67  |

| 5.3 | Important Circuit Design Strategies and Clocking Strategies Matches | 68  |

| 5.4 | rMAJ Operation Truth Table                                          | 69  |

| 5.5 | rMAJ <sup>-1</sup> Operation Truth Table                            | 69  |

| 6.1 | Pipelining within a Pipe Stage                                      | 76  |

| 6.2 | Symbol Meanings for Retractile Cascade Pipeline Equations           | 77  |

| 6.3 | Summary of Assumptions, Part I                                      | 99  |

| 6.4 | Summary of Assumptions, Part II                                     | 100 |

## Preface

The purpose of this document is as follows: Assume you are tasked to implement a system, but can choose any design style. You decide to try QDCA to see if it offers advantages over other options. This design guide then becomes effective for creating the best quality QDCA implementation. To figure out if a QDCA implementation is actually better, trial designs of QDCA and alternatives would need to be compared.

There are two independent decisions to be made at the top level: implementation technology and a logic schema that includes reversibility. A third consideration on fault tolerance follows.

#### Implementation Technology

A handful of QDCA technologies have been proposed, and there are variants within each. For example, there are molecular implementations, "quantum fortress", electrostatically gated quantum dots, metal island, etc. Each of these differ in cell size, operating temperature, manufacturability, and fault tolerance.

Within each of the technology options above, there will be sub-options. For example:

- 1. How many physical clocks are allowed; clock drivers integrated on chip

- 2. Clock zones limited to columnar regions, arbitrary patterning on top of chip, or clock patterning top and bottom

- 3. High or low ratio of dissipation versus bit erasure energy

- 4. Physical support for crossovers yes/no.

#### Logic (Reversibility) Schema

Generally, it will be a good idea to have reversibility at the lower levels. Most logic occurs at the lower levels (the "inner loop") so making the lower levels reversible translates most directly to power savings. However, the effort of making logic reversible cascades to higher levels where the benefit is less (i. e. the "outer loop"). A generally reasonable strategy is to draw a line at some logic level, with reversibility employed below the line and not above it.

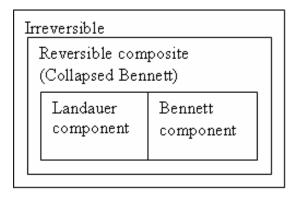

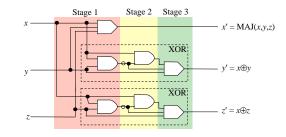

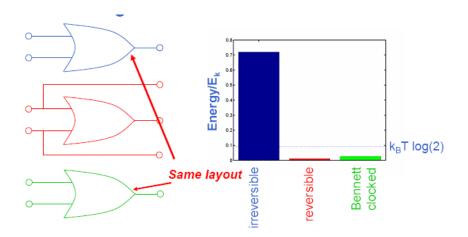

Figure 1. Exemplary Hierarchical Composition of Logic Schema

The reversible logic part of the design will need to comply with some sort of reversibility schema. The Bennett and Landauer clocking schema were proposed in the early papers, but over time it seems that these are just two instances of schema out of a larger space (see figure). QDCA cells obey a fairly simple set of rules about when they will work reversibly, work irreversibly, and don't work at all. Given the technology and sub-options as discussed above, it is feasible to define a low-level clocking structure (of which Landauer and Bennett are instances). It is then possible to hierarchically combine low-level modules into higher-level ones more reminiscent of a classical microprocessor. "Collapsed Bennett" design is an example of a higher-level schema.

#### Fault Tolerance

It is expected that manufacturing of QDCA systems will need to cope with the occurrence of a high level of defects at manufacturing.

With molecular implementations, QDCA cells each made of two dipoles or dots will be deposited on a patterned substrate. At this level however, new types of defect are likely to occur. Missing or additional cells are inevitable for molecular implementation, because the process of cell deposition is very sensitive a small variation in process parameters may result in a defect.

In order to provide a model for test, the functional effect of these defects will need to be characterized, moreover to increase the production yield some techniques of fault tolerance will need to be provided to the system. Some of the defects that will be enountered are discussed in terms of design rules in chapter two.

Although a detailed analysis of the possible fault tolxxerant techniques is not in the

scope of this report, the the adoption of these techniques will introduce a consequent redundancy in terms of space or time that will need to be considered in the design.

## Chapter 1

## Introduction to QDCA

#### The Problem

The goal of computer designers and manufacturers is to produce smaller, faster computers. In 1965, Gordon Moore described the success of the industry in this matter noting that between 1959 and 1965, the number of components on a die grew exponentially [26]. This trend has continued with the number of transistors on a die nearly doubling every 18-24 months. This success has been achieved primarily by shrinking the size of the transistor, aided by the increasing size of the die. For instance, Intel's 4004 released in 1971 was made of 2300, 10 micron transistors on a 12  $mm^2$  die [41]. In contrast, today's chips contain tens or hundreds of millions of transistors near 0.07 microns on dies on the order of several hundred square millimeters.

However, the current strategy of shrinking the transistors and maintaining the same design paradigm will soon be insufficient to meet physical, economic, and architectural barriers. The smallest transistors in production today operate despite quantum effects. In the near future, the operation of transistors will be dominated by the quantum world. The current device, the CMOS transistor, will need to be replaced by one that embraces these quantum effects and takes advantage of the physics that governs at the nano-scale. Fabrication costs, short lifetime of chip generations, rising capital costs, and demand for computing power from consumers all create economic challenges for the semiconductor industry [39]. Finally, as the gap between processor and memory speeds continues to grow, the von Neumann bottleneck will create a greater and greater architectural barrier to continued performance increases.

These barriers point to the need for a new kind of fundamental device and architecture, such as quantum-dot cellular automata (QDCA). The device characteristics of QDCA, which will be introduced below, are quite different from CMOS characteristics. This changes the cost landscape which in turn changes the look of efficient designs. The design frameworks presented in this document take advantage of the characteristics of QDCA, in particular the natural marriage of QDCA and reversible computing.

| Irreversible AND |   |         | Reversible AND |   |   |   |         |

|------------------|---|---------|----------------|---|---|---|---------|

| А                | В | A and B | А              | В | А | В | A and B |

| 0                | 0 | 0       | 0              | 0 | 0 | 0 | 0       |

| 0                | 1 | 0       | 0              | 1 | 0 | 1 | 0       |

| 1                | 0 | 0       | 1              | 0 | 1 | 0 | 0       |

| 1                | 1 | 1       | 1              | 1 | 1 | 1 | 1       |

Table 1.1.

Truth Table of AND Operation

#### **Brief Introduction to Reversible Computing**

Reversible computing builds on a well-established thermodynamics history starting with Maxwell's Demon, Maxwell's 1867 thought experiment that showed that destroying, or erasing, information results in heat dissipation, specifically at least kt \* ln(2) where k is Boltzman's constant and T is the temperature of the system.

In traditional computing based on CMOS technology, the energy dissipated by the device and clock independent of the function being performed dominated any energy dissipation due to irreversibility. However, non-traditional technologies such as QDCA offer a new opportunity to experimentally verify the connection between physical devices and information.

The key insight of reversible computing is that information does not need to be destroyed during computation. There is a fundamental connection between logical reversibility and physical reversibility, and if a logically reversible system is implemented by physically reversible devices, there need not be any power dissipation due to information erasure.

To be reversible, a function needs to be one-to-one. Any function can be made to be one-to-one by saving the inputs. For instance, it is clear from examining the truth table of the AND operation (table 1) that AND is naturally irreversible since there are three zeros in the output making it impossible to determine what the inputs were from just the output. However, by copying the inputs to the output the function becomes one-to-one. In this way, any irreversible function can be made to be reversible at the expense of carrying additional information, or garbage data, forward through the computation.

To take full advantage of reversible computing, the physical implementation of the logic must be physically reversible. Traditional CMOS is not physically reversible since  $V_{dd}$  is constantly being dumped to ground. In contrast, QDCA has the potential for very low power operation to the point that energy dissipated due to information destruction will be a significant if not dominant factor of the overall heat dissipation of the system. For perhaps the first time, QDCA systems may allow the connection between information destruction and heat generation to be seen and used in a real

#### A Computer Architect's Introduction to Quantumdot Cellular Automata

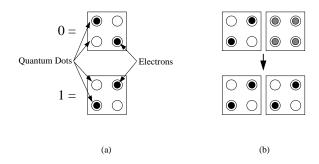

QDCA is a novel alternative to the transistors, silicon, and CMOS paradigm. Rather than using charge movement, current, to propagate signals and perform operations, QDCA uses devices as charge holders, using Coulombic repulsion of electrons as the primary computing force. A QDCA cell consists of four quantum dots arranged in a square with two excess electrons that can occupy the dots. Because the electrons are repelled by each other, they naturally reside in opposite corners. As a result, the cell has two stable states. The first is an electron in the bottom left corner and the top right corner. A cell with this configuration has a polarization of +1 and represents logical "1". The second stable state is an electron in the top left corner and the bottom right corner, a polarization of -1 representing a logical 0 (figure 1.1). The electrons can tunnel between the quantum dots allowing them to change configurations.

Figure 1.1. QDCA Cell (a) Polarization and corresponding logic values, (b) Signal propagation in QDCA. The cell on the left is polarized, the cell on the right is unpolarized. The cell on the right transitions to assume the polarization of the driving left cell.

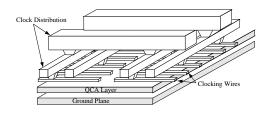

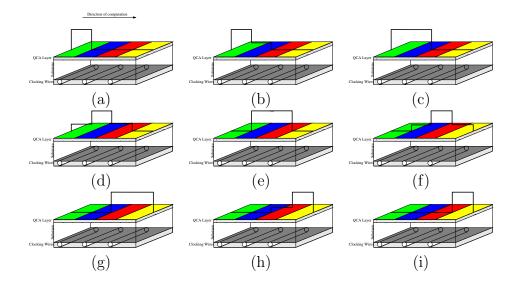

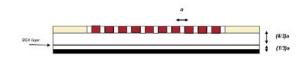

Traditionally in QDCA, computation is performed by controlling the tunneling with a four phase "clock" signal (figure 1.3). There are other clocking strategies that will be discussed later in this work in chapter three. Unlike CMOS circuits, the QDCA clock is a fundamentally different phenomenon than the data. The clocking wires generate an electric field that controls the tunnelling of electrons between dots on the QDCA layer (figure 1.2). The clocking field will be generated by fine wires near the QDCA layer. These wires will need to be connected by thicker wires to the signal generators.

Figure 1.2. Fine wires near the QDCA layer create the clocking fields. Thicker wires distribute the clocking signals to the fine wires.

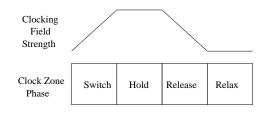

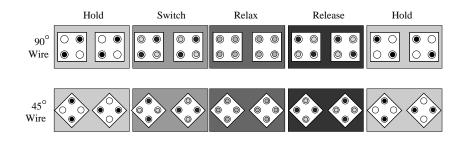

The clock raises and lowers the barriers between the dots, alternately prohibiting and allowing the electrons to tunnel between dots. The raising and lowering behavior of the clock signal is described by four phases called switch, hold, release, and relax. In the switch phase, the barriers begin low, allowing tunneling, and are raised to prohibit tunneling. In this phase, the cell transitions from having no value to having a definite value. The hold phase follows switch in which the barriers are maintained high, preserving the value assumed during switch. In the release phase, the barriers are falling, allowing the cell to go from a well-defined state to an undefined state in which the cell has no natural polarization. Finally, the relax phase maintains low barriers and no polarization.

Figure 1.3. Propagation of clock signal in a single cell through time.

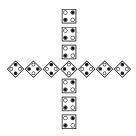

If QDCA cells are lined up side by side and clocked appropriately, they act as a wire, propagating a signal down its length (figure 1.4a). Cells laid out in this side by side manner are called 90 degree cells. The alternative is 45 degree cells which are laid out corner to corner (figure 1.4b). In a 45 degree wire, the signal is inverted at each cell. If the first cell holds a "1", the second cell will hold a "0", followed by a "1" in the third cell, and so on.

QDCA cells exist on a single plane. Theoretically, the two types of wires are able to crossover each other in this single plane without effecting the values being transmitted (figure 1.5). This makes complex circuits possible. This strategy will require very precise fabrication techniques. In addition to this physical crossover strategy,

Figure 1.4. Shaded boxes indicate clocking zones. a) 90 degree cells forming a "wire". b) 45 degree cells forming a wire.

temporal and logical crossover strategies have also been proposed.

Figure 1.5. Wire crossover.

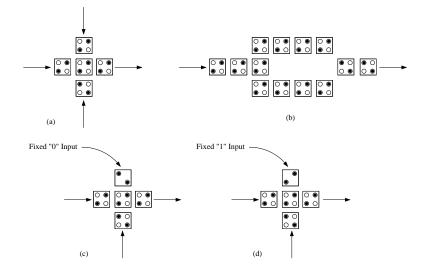

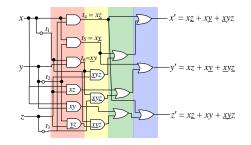

The basic logic gate in QDCA is the three input majority gate (figure 1.6a). Three input cells are arranged on the edges of a center "device cell." The output of the gate is on the fourth edge of the device cell. The input cells and the device cell share the same clock zone. Because of this and simple coulombic repulsion, the device cell assumes the value of the majority of the inputs. When this device cell is frozen in the hold phase, it drives the output cell which then proceeds as a normal QDCA wire. It is notable that the majority gate is a natural, native device in QDCA. It requires nothing more than the QDCA cells and clocking already introduced. This majority gate can be converted to either an AND gate or an OR gate by fixing one of the inputs to be permanently "0" (figure 1.6c) or "1" (figure 1.6d) respectively.

An inverter is needed for logical completeness, and is formed by taking advantage of the 45 degree interaction (figure 1.6b).

Notice that the majority gate is not natively reversible. However, as discussed above, it can be made to be reversible by saving its inputs. This can be done either by the QDCA circuit or by the clocking strategy. This choice will be further discussed in chapter four.

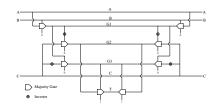

**Figure 1.6.** a) Three-input Majority Gate, b) Inverter, c) AND gate d) OR gate

In addition to these basic gates, the design landscape also includes three other important features. The first is the inherent latching in wires. In essence, the wires are shift registers. This adds a new dimension to designing QDCA circuits rather than CMOS circuits, allowing a designer to pipeline at a very fine level. Connected to this inherent latching and pipelining, the second feature of QDCA is the close connection between layout and timing [35]. There is an upper and lower bound on the size of clocking zones. Distances and time, then, are very tightly coupled. Finally, bits in QDCA designs are always in motion. The clock and the cells are made of different technologies. Perhaps in the future it may be feasible to have the circuit influence the operation of the clock, but for the design strategies presented in this work, it is assumed that once the clock starts running, it continues to operate independently of the information in the circuit. This, too, changes the design decisions made. These aspects of design will also be discussed somewhat further in chapter five

#### **Prior QDCA Architecture Work**

Computer engineering QDCA research first focused on device basic logical devices and an adder as an example of a QDCA circuit [44]. Niemier's work was the first look at the effect QDCA has on architecture and system design. His initial work focused on the hand designing of a simple but complete processor in QDCA much as the first Intel 8086 processor was designed [28][17]. In the course of this work, Niemier identified several key elements of circuit design in QDCA including the connection between layout and timing [35], the potential of processing-in-wire and fine-grained pipelining [32] [31] [34] [30], and initial floorplanning for logic [28]. In addition, since the first molecular QDCA circuits that will be fabricated will need to be regular structures, the design of implementable FPGAs was explored [36] [33]. Another key work explored the layout parameters and layout rules that will govern the layout of QDCA circuits [29].

Memory systems have also been explored. Frost designed a very dense, finely pipelined memory to work in conjunction with Neimier's processor [13][11]. A novel execution model, the bouncing threads execution model, was explored in conjunction with the H-memory model [14]. Memory cells have been explored by Ottavi [38], Walus [45], and earlier by Fountain and Berzon [4].

Research is also being pursued to build fault models for QDCA circuits in order to build fault tolerant circuits and to build CAD tools to facilitate testing and design of circuits [10]. In addition, the first algorithm that addresses the circuit partitioning problem in QDCA has been developed [1].

#### The Real Device

QDCA is very real. QDCA cells have been fabricated and their operation experimentally verified [3] [37]. These QDCA cells were constructed with metal dots on a micron scale and operate at 70 mK. As the size of the cell grows smaller, the operational temperature will rise [23]. A molecular implementation, then, would allow room temperature operation as well as offering significant potential density gains in circuits. Lieberman, *et al* have investigated several two dot-molecules such as the Creutz-Taube ion and mixed-valence ruthenium dimers. In addition, they have explored options for attaching these molecules to etched self-assembled monolayers [25]. Other groups at Notre Dame are investigating four-dot molecules[24] and alternate fabrication strategies such as DNA tiling.

In addition to the QDCA cells, a functioning QDCA circuit requires a clock signal and input/output capabilities. Lent, *et al* have designed an implementable clocking scheme in which buried metal wires are used to create the clocking field [15]. Bernstein, *et al* are investigating mechanisms for detecting the output of QDCA circuits. The output of the metal-dot systems were detected using single electron transistor electrometers [3] [25].

Current estimates place fabrication of simple molecular circuits being possible within three to five years. More complex circuits and large scale fabrication will require more time, but are expected to be possible before the end of the roadmap is reached and nanoscale devices are required to meet density, speed, power and performance demands.

### **Original Contributions**

This work is the first attempt to describe how to go about designing a reversible QDCA system. The design space is substantial, and there are many questions that a designer needs to answer before beginning to design. This document begins to make the tradeoffs and assumptions that need to be made explicit and offer a range of approaches as starting points and examples.

#### Organization

This design guide is organized in a roughly bottom up fashion. Chapter 2 discusses some physical properties of the device that designers should be aware of. Chapter 3 discusses ways in which the clocking field can be organized. CHpater 4 discusses the circuit implementation of the clocking signal. Chapter 5 explores circuit design QDCA, and Chapter 6 discusses some architectural approaches to designing QDCA systems.

## Chapter 2

## **Physical Properties**

There is a subtantial body of literature describing the QDCA device. There are a few low-level properties in particular that designers should be cognizant of. These properties include kink energy, gain, and what parameters should be considered for Conway-Mead type design rules for QDCA. In addition, in considering the design of reversible systems, it may be worthwhile to examine adiabaticity in the context of the clocking wires.

#### Kink Energy

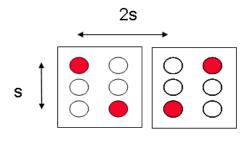

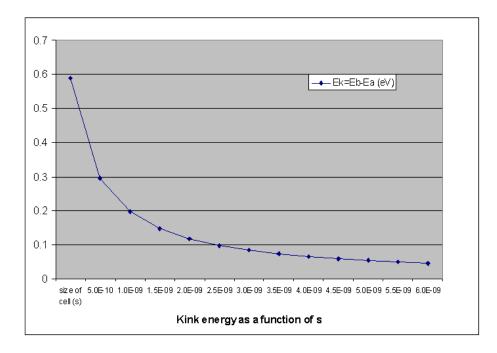

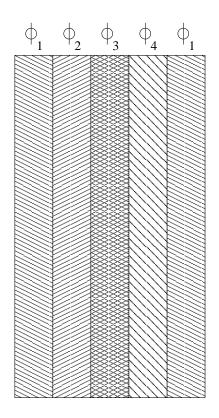

The kink energy of a system composed of two QDCA cells is defined as by the Coulombic energy of the two cells in opposite polarization (as shown in Figure 2.1) with respect to the energy of the cells being in the same polarization status.

The Coulombic energy between two quantum dots is:

$$E_{i,j} = \frac{1}{4\pi\epsilon_0\epsilon_r} \frac{q_i q_j}{d_{ij}}$$

Figure 2.1. Considered sizes of Cell

Figure 2.2. Kink Energy: (a) Ground State (b) Excited state

The energy between two neighboring cells indexed (1) and (2) is therefore:

$$E_{1,2} = \sum_{i=1}^{4} \sum_{j=1}^{4} \frac{1}{4\pi\epsilon_0\epsilon_r} \frac{q_{1i}q_{2j}}{d_{ij}}$$

Where the contributions internal to each single cells have been neglected as they amount to the same value in any cell.

Therefore the Kink energy among the two cells is the difference between the energies of the configurations (a) and (b) shown in figure 2.2.

The energy of configuration (a) is the ground state energy and can be written as:

$$E_a = \frac{1}{4\pi\epsilon_0\epsilon_r}q^2\left(\frac{1}{2s} + \frac{1}{2s} + \frac{1}{\sqrt{(3s)^2 + s^2}} + \frac{1}{\sqrt{s^2 + s^2}}\right)$$

The energy of configuration (b) is the energy of the first excited state and can be written as:

$$E_b = \frac{1}{4\pi\epsilon_0\epsilon_r}q^2\left(\frac{1}{3s} + \frac{1}{s} + \frac{2}{\sqrt{(2s)^2 + s^2}}\right)$$

The Kink energy is  $E_k = E_b - E_a$  and it is therefore a function of the dielectric constant between the dots, the size of the cell and the charge on each dot  $E_k = f(\epsilon_r, s, q)$ . Assuming q = 1 and  $\epsilon_r = 1$  (vacuum) the  $E_k$  is plotted in Figure 2 as a function of s

#### Gain

Gain is critical for any electronic device to guarantee signal restoration. The theory of ower gain in clocked QDCA was explored by Timler and Lent [43], and gain was

experimentally demonstrated by Kummamuru, *et.al.* [19]. The details of the calculations and experiment will be left for the reader to explore. It is very significant that QDCA demonstrates gain, though, because many emerging devices lack gain and therefore have a very limited range of circuit design techniques and architectures. QDCA, though, does demonstrate gain and has a wide variety of circuit and architectural opportunities.

#### Parameters for Conway-Mead Type Design Rules

One of the challenges when working with any emerging device is that there is not a set of well unuderstood abstractions, or interfaces between device physicists, circuit designers, and computer architects. For instance, Conway and Mead's work in defining design rules for MOS in terms of a fundamental unit  $\lambda$  truly revolutionized the design of circuits and computers.

For emerging devices, it is an ongoing challenge to try to define design rules that capture everything the circuit designer needs to know about the underlying structure to guarantee a circuit that works as expected without muddying the waters with too much information about the details of the device physics. Niemier took the first steps toward design rules for molecular QDCA by identifying possible sources of error in QDCA circuit fabrication and proposing the beginnings of design rules for QDCA [29]. The discussion that follows is a summary of his work.

For Mead and Conway, the sources of error avoided by the design rules are related to the resolution of the process fabricating the circuit. The Mead-Conway rules use the unit length  $\lambda$  to minimize the impact of fabrication errors such as over etching, misalignment of mask levels, distortion of the silican wafer due to high temperature processing, and over or under exposure of resist. The Mead-Conway rules abstract away from these sources of error to communicate to the circuit designer the information needed to design circuits that will most likely function as expected. The abstraction covers information such as the minimum width of a wire to guarantee current flow, the minimum wire spacing to separate information, and the overlap between layers to assure good contact.

Similarly, the possible errors result from improper electrostatic interactions that effect of which scale with differently with distance d. These include charge-charge interactions (1/d), charge-dipole interactions  $(1/d^2)$ , dipole-dipole interactions  $(1/d^3)$ , charge induced dipole interactions  $(1/d^4)$ , dipole induced dipole interactions  $(1/d^5)$ , dispersion effects  $(1/d^6)$ , and van der Waals effects  $(1/d^{12})$ . These errors occur due to cells not attaching to the substrate, improper distance between cells, misalignment of cells, improper cell rotation, and cells of differing heights. Analogous to the Mead-Conway rules, the QDCA rules abstract these errors to five broad categories. The rules seek to define spacing to guarantee information transfer, spacing to guarantee information isolation, spacing and rotation rules to guarantee proper gate operation, spacing and rotation rules for physical crossovers, and a set of rules to guarantee the clocking field behavior.

Specifically, Niemier's design rules are:

• Cell Spacing

1A: Maximum allowed spacing between cells that will transmit data. Cells that are too far apart will not have the required coulombic interaction to reliably assume the same configuration.

1B: Minimum distance cells can be apart and still transmit data. Depending on the particular implementation, cells may need to be a minimum distance apart to transmit data. For instance, if cells are too close, electrons may tunnel between cells rather than within a cell.

• Wire

2A: Wire lengths with no disorder. Even in a perfectly fabricated wire, there will be a limit on the length of a wire in a zone controlled by a single clocking signal. This will depend on the kink energy which will depend on the particular QDCA implementation.

2B: Wire lengths and disordered wires. The kink energy decreases with disorder. Different types of disorder with be possible with different implementations and substrates.

2C: Distance between two parallel wires. To avoid the analogous error to crosstalk, wires will need to be a minimum distance apart.

2D: Incomplete wires. This can be thought of as a special case of rule 1A, the maximum spacing between cells.

• Crossovers

3: Crossover (governed by 1A and 2B). The physical crossing of 45 degree wires and 90 degree wires will be governed partly by rules 1A and 2B, but the set of rotations allowed and required will be more specific than the general 1A and 2B cases.

• Majority Gate

4: Majority gate (governed by 1A and 2B). Similar to the crossover case above, the majority gate can be thought of as a special case of rules 1A and 2B. However, there is the added complication of the interaction of the device cell with the inputs.

• Rippers

5: Ripper (governed by 1A, 1B, and 2B). A value can be "ripped" off a 45 degree wire bt a 90 degree cell (the opposite interaction of the crossover). This, too, is a special case of rules 1A, 1B, and 2B.

• Clock Related

6A: Move charge in clocking wires adiabatically. In addition to standard VLSI rules, to maintain low power operation, the clocking signals should be generated adiabatically. This will influence the types of circuits that generate and distribute the clocking signals.

6B: Voltage needed across QDCA layer to properly clock it. The QDCA implementation will define the voltage that needs to be felt across the QDCA layer. The thickness and makeup of the substrate will then dictate what sort of voltage the clocking wires need to generate.

6C: Clocking wire placement error. The clocking wires need to be fabricated in a normal process that will have fabrication errors as discussed by Mead and Conway. These need to be taken into account when designing the entire QDCA system.

6D\*: Clock signal phase error. This rule was identified by Ottavi. There may be error in the generation of the clocking signal so the relative phases of the clocking signals would be off. This effect needs to be accounted for as well.

• Misc. Other Rules

M1: Switching and discharge times of the clock. The clock may have very different switching times than the QDCA cells. This may result in the degradation or disruption of data on the QDCA layer.

M2: The y-component of a generated electric field. This is somewhat related to rule 6B, but it also encompasses the shape of the electric field being generated and the appropriate distance of the wire from the QDCA layer.

| Label | Rule                                        |

|-------|---------------------------------------------|

| 1A    | maximum allowed spacing between cells to    |

|       | transmit data                               |

| 1B    | minimum allowed spacing between cells to    |

|       | transmit data                               |

| 2A    | wire lengths with no disorder               |

| 2B    | wire lengths with disordered wires          |

| 2C    | distance between two parallel wires         |

| 2D    | incomplete wires                            |

| 3     | crossover (governed by 1A and 2B)           |

| 4     | majority gate (governed by 1A and 2B)       |

| 5     | rippers (governed by 1A, 1B, and 2B)        |

| 6A    | move charge in clocking wires adiabatically |

| 6B    | voltage needed across QDCA layer to prop-   |

|       | erly clock it                               |

| 6C    | clocking wire placement error               |

| M1    | switching and discharge times of the clock  |

| M2    | y-component of a generated electric field   |

| M3    | power dissipation                           |

| M4    | multiple clock systems                      |

Table 2.1.

Niemier's Molecular QDCA Design Rules

M3: Power dissipation. It is unclear what design rules would be required or helpful to handle power dissipation issues. However, this will be an important consideration for any QDCA system.

M4: Multiple clocks in a system. Different regions of the QDCA circuit may be clocked by completely different clocking circuits. These regions will still need to be able to communicate with eachother.

Niemier's work was the first attempt to define design rules for any emerging nanotechnology. His work began to define what kinds of rules are needed for QDCA. There is still more work to be done to define the rules and develop some sort of QDCA equivalent to  $\lambda$ . This discussion should communicate a sense for what sorts of challenges are important at the fabrication level and how they will effect the circuit and system level.

#### Adiabaticity: A Case Study

The clocking system will be explored in depth in chapters three and four. However, it may be useful to consider the details of adiabaticity using the clocking system as the example.

Consider an ideal sinusoidal voltage source

$$v_{\rm s} = V \sin(\omega t),\tag{2.1}$$

where V is the voltage amplitude and  $\omega = 2\pi f$  is the angular frequency.

Let us now consider, in a simple lumped-element model, the effect when this source is connected to a load with a capacitance of C through a path with series resistance of R. Let i, v, q be the instantaneous current towards the load through the resistor, the instantaneous voltage across the capacitor, and the instantaneous charge stored on the capacitor, respectively. These are all functions of t. We'll assume that v(0) = 0(the capacitor is initially discharged).

Now, let's build up our model of the circuit dynamics. From the definition of capacitance, we have

$$C = \mathrm{d}q/\mathrm{d}v,\tag{2.2}$$

while from the definition of current and the fact that charge builds up on a capacitor, we have that the instantaneous current is

$$i = \mathrm{d}q/\mathrm{d}t. \tag{2.3}$$

Meanwhile, Ohm's Law gives us that the instantaneous current is also

$$i = (v_{\rm s} - v)/R.$$

(2.4)

Combining eqs. 2.2-2.4 and solving for dv/dt, we obtain the differential equation:

$$\frac{\mathrm{d}v}{\mathrm{d}t} = (v_{\mathrm{s}} - v)/RC,\tag{2.5}$$

or, writing out  $v_{\rm s}$  explicitly,

$$\frac{\mathrm{d}v}{\mathrm{d}t} = (V\sin\omega t - v)/RC.$$

(2.6)

The solution to eq. 2.6 (derived in the appendix) is

$$v(t) = \frac{V}{\sqrt{(RC\omega)^2 + 1}} \sin[\omega t - \tan^{-1}(RC\omega)], \qquad (2.7)$$

where notice that the signal at the load has been taken down in amplitude by the damping factor  $d = \sqrt{(RC\omega)^2 + 1} > 1$  and lags in phase by  $\theta = \tan^{-1}(RC\omega)$ . Both terms depend on the critical dimensionless parameter  $\alpha = RC\omega = t_c/t_r$  where  $t_c = RC$  is the time constant (the e-folding time for the exponential decay) for charging the load C through resistance R, while  $t_r = t_{cyc}/2\pi$  is the time for the source signal to rotate 1 radian, where  $t_{cyc} = 1/f = 2\pi/\omega$  is the clock cycle period. We might call  $\alpha$  the "quickness" of the clock oscillation, judged relative to the circuit's natural transition time of  $t_c$ .

Now, plugging (2.7) back into (2.5), the voltage drop across the resistor is

$$v_{\rm s} - v = \frac{V\alpha}{\sqrt{\alpha^2 + 1}} \cos[\omega t - \tan^{-1}\alpha], \qquad (2.8)$$

so by (2.4) the current is

$$i = \frac{CV\omega}{\sqrt{\alpha^2 + 1}} \cos[\omega t - \tan^{-1}\alpha].$$

(2.9)

Using p = iv, the instantaneous power dissipated in the resistor is then

$$p = \frac{CV^2 R C \omega^2}{\alpha^2 + 1} \cos^2[\omega t - \tan^{-1} \alpha].$$

(2.10)

Over one complete cycle of length  $t_{\rm cyc} = 2\pi/\omega$ , the energy dissipated is thus

$$E_{\rm cyc} = \int_{t=0}^{2\pi/\omega} p \,\mathrm{d}t,$$

(2.11)

$$= \frac{CV^2 R C \omega^2}{\alpha^2 + 1} \int_{t=0}^{2\pi/\omega} \cos^2[\omega t - \tan^{-1}\alpha] dt$$

(2.12)

$$= \frac{CV^2 R C \omega^2}{\alpha^2 + 1} \int_{\theta=0}^{2\pi} \cos^2 \theta \, \frac{\mathrm{d}\theta}{\omega}$$

(2.13)

$$= CV^{2} \frac{\pi \alpha}{\alpha^{2} + 1} = \frac{\pi}{\alpha + \alpha^{-1}} CV^{2}$$

(2.14)

where in (2.13) we have temporarily substituted  $\theta = \omega t$  and removed the phase lag, which is irrelevant to the full-cycle integration.

The most important thing to note about eq. 2.14 is its behavior for small quickness  $\alpha \to 0$ , that is for slow charging, when the radial time  $t_{\rm r} = t_{\rm cyc}/2\pi \gg RC$ . Just as with the classical case of adiabatic charging with a linear ramp, note that here too, as the signal rise time increases and the clock frequency decreases, the energy dissipated per cycle decreases roughly proportionately, since  $\alpha/(\alpha^2 + 1) \to \alpha$  as  $\alpha \to 0$ .

Note also that for very large quickness  $\alpha \to \infty$ , it is also the case that  $E_{\text{cyc}} \to 0$ , since  $\alpha/(\alpha^2 + 1) \to 1/\alpha$  as  $\alpha \to \infty$ . However, in this case, the low dissipation can be attributed to the fact that the load voltage does not have time to change very much in a cycle, due to the substantial size of the damping factor  $d = \sqrt{\alpha^2 + 1}$ , which approaches  $\alpha$  as  $\alpha \to \infty$ .

The maximum dissipation per cycle is  $E_{\rm cyc} = \frac{\pi}{2}CV^2$  which occurs when  $\alpha = 1$ , that is when  $\omega = 1/RC$ . This is the case of "least adiabatic" charging, but in fact dissipates only  $\pi/8 \approx 40\%$  as much energy as the  $4CV^2$  that would be dissipated by a square wave taking the load through the identical range of voltages [-V, +V].

In general, we can characterize the *degree of adiabaticity* of a given process as the ratio between the energy transferred  $E_{\rm tr}$  and the energy dissipated  $E_{\rm diss}$ . For the charging and discharging of a load between -V and +V, the total amount of electrostatic energy moved onto and off of the load is  $E_{\rm tr} = \frac{1}{2}C(2V)^2 = 2CV^2$ , whereas with a sinusoidal driver we saw that the actual dissipation in a cycle was only  $E_{\rm diss} =$  $CV^2\pi\alpha/(\alpha^2 + 1)$ . Therefore, the degree of adiabaticity A of the complete sinusoidal charge/discharge process is

$$A = \frac{2(\alpha^2 + 1)}{\pi \alpha} = \frac{2}{\pi} (\alpha + \alpha^{-1}), \qquad (2.15)$$

which has a minimum of  $4/\pi = 1.27$  when  $\alpha = 1$ . Or, putting things another way, we can define the *energy efficiency*  $\eta = 1 - 1/A = (E_{\rm tr} - E_{\rm diss})/E_{\rm tr} = E_{\rm rec}$  which is the ratio between the amount of energy recovered  $E_{\rm rec} = E_{\rm tr} - E_{\rm diss}$  and the amount of energy transferred. Phrased this way, the efficiency of the sinusoidal charge/discharge cycle is

$$\eta = 1 - \frac{\pi}{2(\alpha + \alpha^{-1})}$$

(2.16)

whose minimum is

$$\eta = 1 - \pi/4 \approx 21.46\% \tag{2.17}$$

when  $\alpha = 1$ , whereas the efficiency approaches 100% as  $\alpha \to 0$ , with the distance from 100% in that limit being proportional to  $\alpha$  since the expression (2.16) for  $\eta$ approaches  $1 - \pi \alpha/2$ . Note, in contrast, that the energy efficiency of a standard abrupt (square wave) charge/discharge process always approaches 0% whenever the load voltage range approaches full-swing, since the energy delivered from the constant-voltage source after the rising edge is  $CV^2$ , and exactly this much energy is dissipated upon charging and then discharging the load (half of it or  $\frac{1}{2}CV^2$  after each clock edge). Whereas for the adiabatic driver, the case  $\alpha \to 0, d \to 1$  where the load voltage range approaches full swing (and also with phase lag  $\theta$  approaching zero) is also the same limit in which the energy efficiency of the charge transfer approaches 100%.

We can thus see that in all cases, sinusoidal charging dissipates less energy per complete charge-discharge cycle than sharp-edged square-wave charging, dissipating at most about 21% of the energy transferred, and at best nearly 0% when the clock period  $t_{\rm cyc}$  is large compared to  $2\pi RC$ , since in this limit, as  $\alpha = RC/t_{\rm cyc} \rightarrow 0$ , the fraction of the capacitor charging energy that is actually dissipated on each cycle approaches  $\pi \alpha/2$ , that is, it goes down in proportion to the quickness of the clock transitions, as would be expected for an asymptotically adiabatic process.

#### Solution of Differential Equation

This section shows how to solve the differential equation (2.6) from first principles, without delving into formulations in terms of complex impedances which may be non-intuitive for some readers.

We know from our general background knowledge that a circuit composed of linear elements (resistors, capacitors, and inductors) and driven by constant-frequency sinusoidal sources will always attain what is known as an AC steady state. Thus, the solution to (2.6) must also be a sinusoid of constant amplitude, frequency, and phase shift; furthermore, it must have the same average (DC) level as the source, since the resistor cannot support a constant DC voltage drop.

Thus, we know that the solution to (2.6) must be of the form

$$v(t) = V_{\rm L}\sin(\omega_{\rm L} + \theta_{\rm L}) \tag{2.18}$$

where  $V_{\rm L}$  is the amplitude of the voltage swing (from  $-V_{\rm L}$  to  $+V_{\rm L}$ ) of the signal on the load node,  $\omega_{\rm L}$  is the angular frequency of this signal which we will see must be the same as the driving frequency  $\omega$ , and  $\theta_{\rm L}$  is the relative phase of the load.

Starting from (2.18), we can take its derivative

$$\frac{\mathrm{d}v}{\mathrm{d}t} = V_{\mathrm{L}}\omega_{\mathrm{L}}\cos(\omega_{\mathrm{L}}t + \theta_{\mathrm{L}}) \tag{2.19}$$

which we can then plug into the left side of (2.6), along with (2.18) itself in place of