LIVERMORE NATIONAL

LABORATORY

# SURVEY OF NOVEL PROGRAMMING MODELS FOR PARALLELIZING APPLICATIONS AT EXASCALE

Rich Cook, Evi Dube, Ian Lee, Lee Nau, Charles Shereda, and Felix Wang

November 17, 2011

#### **Disclaimer**

This document was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor Lawrence Livermore National Security, LLC, nor any of their employees makes any warranty, expressed or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or Lawrence Livermore National Security, LLC. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or Lawrence Livermore National Security, LLC, and shall not be used for advertising or product endorsement purposes.

This work performed under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under Contract DE-AC52-07NA27344.

# **Table of Contents**

| 1. | EXECUTIVE SUMMARY                                        | 5  |

|----|----------------------------------------------------------|----|

| 2. | INTRODUCTION: OVERVIEW OF THIS STUDY AND ITS OBJECTIVES. | 6  |

|    | 2.1. Resources                                           | 7  |

| 3. | PARALLEL PROGRAMMING MODELS OVERVIEW                     | 8  |

|    | 3.1. Chapel (Cascade High-Productivity Language)         | 10 |

|    | 3.1.1. Overview                                          |    |

|    | 3.1.2. Present State of the Model                        | 11 |

|    | 3.1.2.1. Robustness and Known Issues                     |    |

|    | 3.1.3. Tool Availability                                 | 13 |

|    | 3.1.4. Performance                                       |    |

|    | 3.1.5. Suitability to LLNL Application Codes             |    |

|    | 3.1.6. Resources and Additional Information              |    |

|    | 3.2. X10 programming language                            |    |

|    | 3.2.1. Overview                                          |    |

|    | 3.2.2. Present State of the Model                        |    |

|    | 3.2.3. Tool Availability                                 |    |

|    | 3.2.3.1. Debugger                                        |    |

|    | 3.2.3.2. Performance analysis tools                      |    |

|    | 3.2.3.3. Other Tools                                     |    |

|    | 3.2.4. Performance                                       |    |

|    | 3.2.5. Suitability to LLNL Application Codes             |    |

|    | 3.2.6. Bibliography                                      |    |

|    | 3.3. Fortress                                            |    |

|    | 3.3.1. Overview                                          |    |

|    | 3.3.2. Present State of the Model                        |    |

|    | 3.3.2.1. Robustness and Known Issues                     |    |

|    | 3.3.3. Tool Availability                                 |    |

|    | 3.3.4. Performance                                       |    |

|    | 3.3.5. Suitability to LLNL Application Codes             |    |

|    | 3.3.6. Resources and Additional Information              |    |

|    | 3.3.7. Bibliography                                      |    |

|    | 3.4. CILK PLUS LANGUAGE EXTENSIONS                       |    |

|    | 3.4.1. Overview                                          |    |

|    | 3.4.2. Present State of the Model                        |    |

|    | 3.4.2.1. Robustness and Known Issues                     |    |

|    | 3.4.3. Tool Availability                                 |    |

|    | 3.4.4. Performance                                       |    |

|    | 3.4.5. Suitability to LLNL Application Codes             |    |

|    | 3.4.6. Resources and Additional Information              |    |

|    | 3.5. INTEL PARALLEL BUILDING BLOCKS: ARBB & TBB          |    |

|    | 3.5.1. Overview: TBB and ArBB Common Characteristics     | 29 |

|    | 3.5.1.1. Threading Building Blocks                       |    |

|    | 3.5.1.2. Array Building Blocks                           |    |

| 3.5.2.   | Present State of Model                    |    |

|----------|-------------------------------------------|----|

| 3.5.2.   | 1. Robustness and Known Issues            |    |

| 3.5.3.   | Tool Availability                         |    |

| 3.5.4.   | Performance                               |    |

| 3.5.5.   | Suitability to LLNL Application Codes     |    |

| 3.5.6.   | Resources and Additional Information      |    |

| 3.5.7.   | Bibliography                              |    |

| 3.6. UP  | С                                         |    |

| 3.6.1.   | Overview                                  |    |

| 3.6.2.   | Present State of the Model                |    |

| 3.6.2.   | 1. Robustness and Known Issues            |    |

| 3.6.3.   | Tool Availability                         |    |

| 3.6.4.   | Performance                               |    |

| 3.6.5.   | Suitability to LLNL Application Codes     | 40 |

| 3.6.6.   | Resources and Additional Information      |    |

|          | PI & Charm++                              | 42 |

| 3.7.1.   | Overview                                  |    |

| 3.7.2.   | Present State of Model                    |    |

|          | 1. Robustness and Known Issues            |    |

| 3.7.3.   | Tool Availability                         |    |

| 3.7.4.   | Performance                               |    |

| 3.7.5.   | Suitability to LLNL Application Codes     |    |

| 3.7.6.   | Bibliography                              |    |

|          | ENCL                                      |    |

| 3.8.1.   | Overview                                  |    |

| 3.8.2.   | Present State of Model                    |    |

| 3.8.3.   | Robustness and Known Issues               |    |

| 3.8.4.   | Tool Availability                         |    |

| 3.8.5.   | Performance                               |    |

| 3.8.6.   | Suitability to LLNL Application Codes     |    |

| 3.8.7.   | Resources and Additional Information      |    |

|          | DA                                        |    |

| 3.9.1.   | Overview                                  |    |

| 3.9.2.   | Present State of Model                    |    |

| 3.9.3.   | Robustness and Known Issues               |    |

| 3.9.4.   | Tool Availability                         | 53 |

| 3.9.5.   | Performance                               |    |

| 3.9.6.   | Suitability to LLNL Application Codes     |    |

| 3.9.7.   | Resources and Additional Information      | 54 |

| 4. RECON | IMENDATIONS                               |    |

| APPENDIX | A. ADDITIONAL EXASCALE PROGRAMMING MODELS |    |

## **1. Executive Summary**

A range of programming models (and the languages that constitute the practical implementation of these models) exist to address parallel programming challenges. At present, however, one model dominates LLNL application codes: SPMD message-passing using MPI for internode communication, and occasionally, OpenMP for intranode parallelism.

In this survey, we characterize the following novel programming models that may be of use to LLNL teams as supercomputing moves toward exascale.

- Chapel

- X10

- Fortress

- Cilk Plus

- Intel Parallel Building Blocks

- UPC

- AMPI and Charm++

- OpenCL

- CUDA

Some of these models make better use of intra-node resources than the present model, or are targeted at GPUs. Others present an entirely new way of addressing large-scale simulation problems, or one that promises more compact and comprehensible code. None are as robust or stable as the present model. For each model, we provide an overview and discuss the model's present state, robustness, and suitability to LLNL application codes. Several models are not discussed in detail and are mentioned in the appendix.

Our recommendations for action consist of the following:

- We recommend a further study of Chapel specifically, an application port.

- We recommend devoting resources to monitoring X10 and Intel PBB.

- We suggest maintaining an Intel PBB implementation.

- We recommend that MPI support staff at LLNL familiarize themselves with AMPI and Charm++ to see if some of its innovations can be applied to issues such as fault tolerance at large scale.

- We recommend maintaining in-house expertise in OpenCL and CUDA but caution against developing a significant codebase, especially in CUDA, which is proprietary.

# 2. Introduction: Overview of This Study and Its Objectives

We conducted this study in response to the need of application teams to determine how to make effective use of the future exascale supercomputing environment at Livermore. The exascale generation of supercomputers will have massive on-node parallelism, much more than current hardware. Making use of this on-node parallelism will certainly require code modification and creative approaches, and may necessitate the adoption of new language paradigms. We investigated some of these new paradigms to determine:

- a) The ease in learning and adopting these languages.

- b) The specific benefits to switching to the new language paradigm. For instance, the language may be far more comprehensible than current models, and mask explicit parallelism to greatly reduce the amount of code required for the same amount of work. Or, it may allow programmers to make use of a form of parallelism not available through other paradigms, such as CUDA or OpenCL for GPUs.

- c) The robustness of the model.

- d) The potential of this model to meet programming needs in the future, regardless of its present state.

#### **Background:**

It is widely expected that the computer systems anticipated in the 2015 – 2020 timeframe will be qualitatively different from current and past computer systems. They will be built using massive multi-core processors with 100's of cores per chip, their performance will be driven by parallelism, constrained by energy, and with all of their parts, they will be subject to frequent faults and failures. (Trivelpiece, 2010)

Coined *Exascale Computing*, the changes will occur in many areas. There will be multiple memory types, including programmable (scratchpad) memory along with generally more heterogeneous/hierarchical systems than today, and the memory: FLOPS ratio is expected to worsen. (Dubrow, 2011)

For *Exascale Computing*, the main programming environment challenges are expected to be within the new node rather than across nodes, since that is where the biggest changes appear to be headed. The total number of nodes is not changing dramatically, so current practices of MPI between nodes to this scale provides one option of utilizing the exascale systems. Another option is to utilize unified programming models at the global level (Chapel, X10, UPC, Co-array Fortran, etc.).

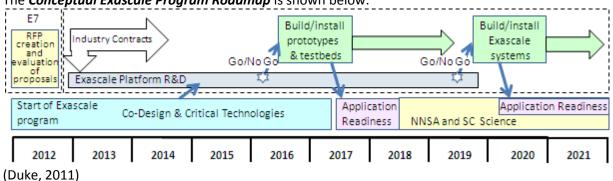

#### The Conceptual Exascale Program Roadmap is shown below:

#### **Objective:**

Our objective in preparing this survey was to determine and document the characteristics of the most promising next-generation parallel programming models that may have applicability at exascale. Targeted at development teams and support staff, it provides a basic overview of each model – enough for a developer to determine if further investigation is warranted for their development effort. Section references and bibliographies can be used as pointers for conducting further work.

## 2.1. Resources

- 1. <u>http://science.energy.gov/ascr/news-and-resources/workshops-and-conferences/grand-challenges/</u>

- 2. The International Exascale Software Project Roadmap,; http://www.exascale.org/mediawiki/images/2/20/IESP-roadmap.pdf

- 3. Chamberlain, Brad (February 2010) *Programming Models (and Programming environments) at the Exascale*; <u>http://chapel.cray.com/presentations/Chamberlain-ProgEnv-CrossCut.pdf</u>

- 4. Dubrow, Aaron (October 5, 2011) *IEEE Conference Keynoters Lay Out Path to Exascale Computing*; HPC in the Cloud, HPC Wire; <u>http://www.hpcinthecloud.com/hpcwire/2011-10-05/ieee\_conference\_keynoters\_lay\_out\_path\_to\_exascale\_computing.html</u>

- 5. Duke, Karl (July 2011) *Exascale RFI*; https://www.fbo.gov/download/8d0/8d04ef8edaca4638063a4a0b7afe9a1d/ExascaleRFI.pdf

- Stevens, Rick etal. (March 2011) A DOE Laboratory plan for providing Exascale applications and technologies for critical DOE mission needs;; http://computing.ornl.gov/workshops/scidac2010/presentations/r\_stevens.pdf

- Trivelpiece, Alvin (January 19-20, 2010) Exascale Workshop Panel Meeting Report; <u>http://science.energy.gov/~/media/ascr/pdf/program-</u> documents/docs/Trivel piece exascale workshop.pdf

- 8. Yelick, Katherine ; *Programming Models for Exascale*; <u>https://hpcrd.lbl.gov/E3SGS/Yelick-Pmodels.pdf</u>

# 3. Parallel Programming Models Overview

In the course of preparing this survey we discovered that we were using the term *parallel programming model* to refer to different concepts. The term can be defined in several different ways. For example:

- a) Informally, a "parallel programming model" can be thought of as a loose, generic term encompassing languages, language extensions, libraries, and other 'things' that are used to accomplish a particular programming objective that requires parallelism. Each unique system such as Chapel or Cilk Plus or MPI or OpenMP, regardless of whether it is a language or a library or language extension, constitutes a programming model in this definition.

- b) One might more formally define "parallel programming model" as being a particular combination of data visibility (local, global), control strategy (local, SPMD, etc), and programming capabilities that describe a method for solving a computational problem, specifically one that requires computational parallelism to solve. An example of this definition of programming model is "Asynchronous Partitioned Global Address Space (PGAS)."

In this survey, we use "programming model" primarily to refer to the systems that are practical implementations of the underlying models. This corresponds with definition (a).

| System (a)                        | Programming Model (b)                      | Data Model                                                            | Control Model                |

|-----------------------------------|--------------------------------------------|-----------------------------------------------------------------------|------------------------------|

| Chapel                            | Partitioned Global<br>Address Space (PGAS) | Global memory view                                                    | Global view                  |

| X10                               | Asynchronous PGAS                          | Global memory view                                                    | Global view                  |

| Fortress                          | PGAS                                       | Global memory view                                                    | Global view                  |

| Cilk Plus                         | Multithreaded                              | Global memory view<br>(single node only)                              | Global view (single<br>node) |

| Intel Parallel Building<br>Blocks | Multithreaded                              | Global memory view<br>(single node only)                              | Global view (single<br>node) |

| UPC                               | PGAS                                       | Global memory view                                                    | Global view                  |

| Charm++                           | Object-oriented                            | Local memory view                                                     | ?                            |

| AMPI                              | Message passing                            | Local memory view                                                     | Local view                   |

| OpenCL                            | GPU language                               | GPU memory view<br>(data is transferred to<br>and from GPU<br>memory) | Global view (single<br>node) |

| CUDA                              | GPU language                               | GPU memory view<br>(data is transferred to<br>and from GPU<br>memory) | Global view (single<br>node) |

The following chart shows the models that we examined for this survey and connects definition (a) with definition (b) for each of these models.

Three of these languages, X10, Chapel, and Fortress, began their lives through the DARPA-funded HPCS effort. X10 is from IBM, Chapel from Cray, and Fortress from Sun (now Oracle). Phase II of the project lasted from 2003 to 2006 and funded all three projects; Phase III began in July 2006; it funded work on X10 and Chapel and dropped funding for Fortress, although Sun continued work on the project for some time in the absence of DARPA money. The original goal of the DARPA effort was to increase programmer

productivity by a factor of 10 by the year 2010. Given that it is now late 2011 and none of these three languages are quite ready to be used for real production codes, that original goal was apparently overly aggressive and optimistic.

The next two languages, Cilk Plus and Intel Parallel Building Blocks, are Intel-driven languages. UPC is a PGAS language developed at LBNL, while Charm++/AMPI is a UIUC project that advances the message passing model. The last two languages, OpenCL and CUDA, allow for programming Graphical Processor Units.

Listed below are additional parallel programming models, presented for comparison purposes. OpenMP, Coarray Fortran, Titanium, and Global Arrays are discussed briefly in Appendix A.

| System (a)      | Programming Model (b) | Data Model                               | Control Model                                                |

|-----------------|-----------------------|------------------------------------------|--------------------------------------------------------------|

| MPI             | Message passing       | Local memory view                        | Local (for library –<br>global control resides<br>elsewhere) |

| OpenMP          | Multithreaded         | Global memory view<br>(single node only) | Global view (single node)                                    |

| Coarray Fortran | PGAS                  | Local memory view                        | SPMD                                                         |

| Titanium        | PGAS                  | Local memory view                        | SPMD                                                         |

| Global Arrays   | PGAS                  | Global memory view                       | SPMD                                                         |

Descriptions of the individual languages appear in the following subsections.

| Owner / Development                                                                  | Cray Inc. (head of team is based in Seattle, WA)           |  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------|--|

| Location                                                                             |                                                            |  |

| Project Website                                                                      | http://chapel.cray.com/index.html                          |  |

| Download Page                                                                        | http://chapel.cray.com/download.html                       |  |

| Platforms Available Most UNIX-based systems, Mac OS X, Windows. Works in conjunction |                                                            |  |

|                                                                                      | the GASNet library which works with various interconnects. |  |

## 3.1. Chapel (Cascade High-Productivity Language)

#### 3.1.1. Overview

Chapel (Cascade High-Productivity Language) is a general-purpose parallel programming language being developed by Cray, Inc. under the DARPA High Productivity Computing Systems (HPCS) program. Chapel was developed from first principles, and the principles guiding the design are:

- general parallel programming,

- locality-aware programming,

- object-oriented programming, and

- generic programming.

As per the language specification documentation, the first two principles were motivated by a desire to support general, performance-oriented parallel programming through high-level abstractions. The second two principles were motivated by a desire to narrow the gulf between high-performance parallel programming languages and mainstream programming and scripting languages.

Taken from its name, Chapel's purpose is to increase programmer productivity while enhancing code robustness. The Chapel development team has four stated productivity goals (Chamberlain B., Chapel tutorial, 2011)

- *Programmability*. All aspects of programming (reading, modifying, maintaining, etc.) should be dramatically improved over current programming models.

- *Performance*. Performance should be competitive with MPI-parallel codes, and better on advanced architectures.

- *Portability*. As universal as MPI and more portable than OpenMP.

- *Robustness*. Semantics and better abstractions eliminate common coding errors.

Several aspects of the language exist to achieve these productivity goals. Based on the Partitioned Global Address Space (PGAS) model, Chapel provides a global view for expressing both data structures and the control flow of the program. Global-view data structures allow programmers to express data aggregates globally even though their implementations may distribute them across the locales of a parallel system. The programmer therefore codes as if a single process is running across many processors, rather than coding for a many-process model. Work is shared across threads. This provides for a more general expression of parallelism than more common contemporary parallel languages that use the Single Program Multiple Data (SPMD) approach. Chapel also operates under a multiresolution philosophy, meaning that programmers can initially write very abstract code and subsequently add more detail to tune for their target architecture. Object-oriented design, type inference, and other features allow for rapid prototyping and code reuse (Chamberlain B., Chapel presentations, 2009)

Chapel has several general and parallel language constructs that are meant to reduce the amount of code necessary to express a concept or perform work. Among many others, these include constructs to

deal with the distributed nature of a global-view data structure, concurrency constructs, and data and task parallelism constructs.

*Domains* in Chapel are a first-class representation of an index set. They provide the programmer with a way to express operations that more closely mimics the original problem without much of the overhead that comes from checking boundaries or complex indexing. A domain's indices may also be distributed across multiple locales on a platform, thus supporting global-view data structures. Additionally, domains may be modified in size fairly easily and arrays associated with those domains will be reallocated accordingly. This is handled by the runtime through the use of domain maps and it provides a good deal of flexibility to potential algorithms without requiring otherwise extraneous portions of code on the part of the programmer. Domains come in three types, base domains, subdomains, and sparse subdomains, and may also be classified as being regular (e.g. rectangular) or irregular (e.g. associative).

*Locales* are described by the Chapel Language Specification as a portion of the target parallel architecture that has processing and storage capabilities (Cray Inc., 2011). In a clustered system, this would be equivalent to a node with multiple processors sharing a memory space. Locales may be referenced within program code, and they provide a way for programmers to reason about and exploit locality.

Data parallelism is generally invoked by the *forall* keyword where iterations of an otherwise serial loop may be calculated independently of other iterations. The number of threads that are used for this all-way parallelism depends on how many cores exist on a processor, but may be changed through configuration variables. Other methods for managing data parallelism include reductions, scans, and shorthand forms in dealing with arrays as a whole.

Task parallelism is invoked using the *begin* and *cobegin* keywords for unstructured task parallelism and the *coforall* keyword for structured task parallelism. In general, there is a distinct thread for each task spawned through a task parallelism construct, and there may be many more threads than there are cores on a processor. In the case of structured task parallelism, each iteration is processed as a separate task from other iterations, and generally, the serial code inside an iteration is more complex than its data parallel counterpart. Because the threads of a task parallel region of code may exceed the number of cores in a processor, the kernel may switch among threads leading to possible issues with concurrency for poorly written codes.

Chapel introduces synchronization variables that provide a way for the programmer to perform more complex types of parallel control beyond the constructs already presented. Synchronization variables possess *full* and *empty* states that methods reading and writing to them can use to prevent data races as well as to determine blocking behavior. Although synchronization variables allow more fine-grained control of the program, the use of too many may be costly both in terms of programming productivity and performance.

#### 3.1.2. Present State of the Model

Chapel is currently an evolving language. Many of the core features of the language have been implemented functionally, however these features are not fully optimized. Additionally, there are several features in the language specification that have yet to be developed. As the language matures, many of these features are expected to be integrated and optimized.

Chapel is available for several platforms with many platform-specific options handled by the Chapel compiler. Inter-node parallelism is based on the PGAS model with communication handled primarily through a Global-Address Space Networking (GASNet) layer. Future plans include additional communication layer options such as Pacific Northwest National Laboratory's (PNNL) Aggregate Remote Memory Copy Interface (ARMCI) library. Intra-node parallelism uses a multithreaded execution model using pthreads as the standard for the threading mechanism. Support for other mechanisms exist, including more lightweight implementations such as Qthreads developed at Sandia National Laboratory (SNL) as well as platform specific options such as MTA when targeting the Cray XMT platform. Support has recently emerged for using GPUs as accelerators in Chapel, in particular using Nvidia GPUs with CUDA. As with the other levels of parallelism, the support at the GPU level is expected to expand, probably with OpenCL as a next target. Several papers can be found describing these options under Section 3.1.6.

Perhaps the main limitation we found of the current state of the Chapel language is the lack of task synchronization within a parallel section of code. Task synchronization would allow the interleaving of serial and parallel code with less overhead than entering and exiting from a structured parallel section. It would also improve ease of programmability, as per the productivity goals. Although cross-task synchronization was achieved using synchronization variables, the resulting mechanism took a great deal of programming effort – more than should be required for such a task. In the literature, there is mention about introducing task *colors* for grouping purposes, and it is likely that this would include constructs for cross-task synchronization. (Chamberlain, Deitz, & Navarro, pgas 11, 2011)

Another current limitation for the Chapel language is the lack of an API to the runtime system. Although the language exposes several parameters that are important to the runtime configuration of a program (e.g. dataParTasksPerLocale), there is no built in way to modify these constants once they are set at execution time. Moreover, there are no methods that expose information or modification of specific threads or cores, meaning that there is no built-in way of exploiting NUMA effects. It is possible that these details of the language will be resolved in a later revision.

## 3.1.2.1. Robustness and Known Issues

Chapel is designed to provide the programmer more ease in coding than are other languages. This results in generally more readable code and with respect to robustness, a lessened chance for syntactical coding errors leading to more reliable code from the beginning. As mentioned previously, the *domain* construct provides a more natural way of expressing the subtleties of indexing a data structure of an algorithm, and this absolves the programmer of much of the effort required in complex bound checking and corner cases. Some language features have not been fully developed yet, with garbage collecting projected to be a significant addition. The features that are currently functional do not seem to have many issues besides being less than optimal in terms of performance.

We noticed an issue with passing a variable by reference multiple times before modifying it in a child process within a parallel section. Serially, this does not pose an issue, but within a parallel section, such as a *coforall* statement, if the variable is modified as though it were serial (i.e. updated by a single task in the collection), an immediate read in parallel may cause unpredictable results. The same algorithm behaves correctly if the multiply referenced variable is replaced by a global variable, however.

The interoperability with other languages is presently not fully functional, and there are definitely issues with calling Chapel generated code from an external language. Moreover, as Chapel does not support explicit pointers, it will require a great deal of effort to successfully glue Chapel together with languages

such as C. There is currently a project, BRAID, which is being developed at LLNL to interface PGAS based languages to traditional HPC languages. (Prantl, Epperly, Imam, & Sarkar, 2011) The BRAID system for Rewriting Abstract Intermediate Descriptions provides glue code in places where languages such as Chapel make references outside of themselves; BRAID then goes through another, older and very robust project, Babel, which is used to integrate with a multitude of other languages. The project is also targeted to handle the distributed arrays that are present in Chapel, introducing a new Scientific Interface Description Language (SIDL) datatype: *DistributedArray*. The robustness of BRAID for Chapel is good and many data structures and types are supported to communicate with other languages. The report from the Chapel compiler team indicates that a new keyword is in development that would allow Chapel modules to be called from an external language more easily. This development would enable support for creating libraries in Chapel for external use.

#### 3.1.3. Tool Availability

At presently there is no Chapel specific debugger available. However, the Chapel compiler allows the programmer to enable a debugging flag (i.e. -g) and compile to the C programming language. The resulting source code may then be stepped through and run through any generic debugger (e.g. gdb) that is able to debug C code. With respect to parallel debugging, it is unclear whether tools exist that work with Chapel, although there are a few compiler flags (i.e. -*blockreport* and -*taskreport*) that may be used on a single locale to debug deadlock conditions. Native support for debugging Chapel that includes language specific knowledge is planned.

Tools for profiling are being added to the priority queue along with performance optimizations and scalability work. There has been success in profiling non-trivial Chapel code using HPCToolKit. The expectation is that as the language grows, more and more of these tools will become available to Chapel. Currently, there are a few Chapel tools for communication diagnostics as well as some memory tracking features to aid the programmer in determining memory leaks. External tools such as HPCToolKit will require more effort on the part of the programmer to work correctly with Chapel.

#### 3.1.4. Performance

Performance is not a defining feature of the Chapel language in its present state. In conversations with the Chapel team, we have learned that there are several low-hanging fruit remaining with respect to Chapel performance that they wish to address. The Chapel team notes that performance and scalability are high priorities for them.

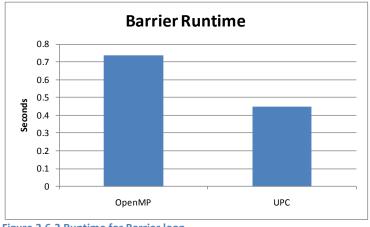

Following a port of the ASC Sequoia benchmark, CLOMP, to the current Chapel version at time of writing (1.3.0), it was discovered that there were speedups in many cases when executing in parallel with Chapel over the serial version of the code. However, for smaller amounts of work per iteration in the parallel loop section, there was greater relative influence of the overheads present in Chapel and slowdowns occurred for the benchmark's "target input" case relative to the serial version. Because Chapel does not yet possess a native barrier call, a manual barrier using synchronization variables had to be implemented for the CLOMP port, and as expected the performance was severely lacking (an order of magnitude) behind the OpenMP barrier call. Moreover, it was discovered that the synchronization constructs of Chapel do not scale with the number of processors as well as expected for a language targeted at multiprocessor platforms. As per our conversations with the Chapel team on the scalability focus, this critical aspect of the language is expected to improve.

Performance measurements with respect to several of the HPC Challenge benchmarks have been performed. (Chamberlain, Choi, Deitz, & Iten, 2009) The most current published results from the

challenge are from 2009 by the Chapel team; their entry for class 2 (most productivity) was awarded "most elegant implementation". Although the language has evolved since then, the performance results show that Chapel was comparable to an MPI version of the code for the Global and EP STREAM Triad benchmarks. Performance on the Random Access benchmark was not competitive with MPI. While a productivity rather than performance measure, the paper also noted that Chapel consistently beat MPI in terms of lines of source code (Chapel had far fewer lines for the same program).

#### 3.1.5. Suitability to LLNL Application Codes

Switching to Chapel would require a dramatic shift in thinking for LLNL application teams coming from an MPI background, distributed memory model, and explicit parallelism framework. Although such a shift may be necessary for the next generation of parallel computing, ideally, this shift would be incremental. This would require that Chapel objects be capable of being directly linked against non-Chapel objects, and against objects that link against MPI. Currently, application teams would be required to rewrite a good portion of their code base due to Chapel's inability to exist as a secondary language. However, work is in progress to create libraries in Chapel, and furthermore, the BRAID project is expected to provide the necessary glue for Chapel to communicate with existing languages.

Chapel provides several constructs that are compatible with the types of codes in use at LLNL. For example, the domain construct supports the creation of adaptive meshes and sparse matrices, and Chapel provides an easy way for programmers to index into the associated data structure. Moreover, the mapping between the global view of these data structures and the locales where they reside is provided through domain maps via the runtime, allowing for less programming overhead than with message passing. Domains may also be distributed across the locales of a clustered system using the *distributions* construct. Standard distributions in Chapel are the block and cyclic layouts, but users may also define their own distributions to better fit their problems. These distributions do not affect codes semantics, but rather are used for implementation and performance effects.

The primary advantages Chapel has over MPI are in programming ease and elegance. Because it is a multiresolution language, it allows for quicker prototyping of algorithms, with architecture specific optimizations added in later. This provides greater code robustness due to a decreased chance for communication errors. Finally, because Chapel is multi-level, it is able to provide homogeneous coding semantics, whereas one may have to add OpenMP to MPI code to fully utilize processor capabilities. With respect to performance, Chapel currently lags behind OpenMP and MPI in general, although it is comparable in some cases and is expected to improve overall as the language progresses.

#### 3.1.6. Resources and Additional Information

The information on Chapel is internet based, and primarily written from the perspective of the Chapel development team or Chapel proponents.

Many resources including several papers, presentations, and tutorials are available through the Chapel homepage: <u>http://chapel.cray.com/</u>

Chapel Language Specifications: <u>http://chapel.cray.com/spec/spec-0.82.pdf</u>

Presentations and videos: http://chapel.cray.com/presentations.html

Tutorials:

- Chapel Overview for Hands-On Session; Discovery 2015; http://chapel.cray.com/tutorials.html

- An Overview of the Chapel Parallel Programming Language; CUG 2011 Tutorial; http://chapel.cray.com/tutorials.html

- Parallel Programming in Chapel: The Cascade High-Productivity Language, SC10 Tutorial; http://chapel.cray.com/tutorials.html

Download: <u>http://chapel.cray.com/download.html</u>

Sourceforge: <a href="http://sourceforge.net/projects/chapel/">http://sourceforge.net/projects/chapel/</a>

Programmer Assistance: The chapel-users email archive found on the Chapel Sourceforge page contains email archives that a developer may find useful. A development version of Chapel may also be downloaded, which contains more information on the workings of the Chapel compiler and its features. http://sourceforge.net/mailarchive/forum.php?forum\_name=chapel-users

Additionally, Colorado State has a wiki and quick reference worth perusing. <u>https://www.cs.colostate.edu/wiki/Chapel\_language</u> <u>https://www.cs.colostate.edu/wiki/mediawiki/images/b/b2/QuickReference.pdf</u>

Wikipedia page: <u>http://en.wikipedia.org/wiki/Chapel\_%28programming\_language%29</u>

Babel homepage: <u>https://computation.llnl.gov/casc/components/#page=homePapers</u>:

- 1. Chamberlain, Bradford L.; Choi, Sung-Eun; Deitz, Steven J.; Iten, David (2009) *HPC Challenge Benchmarks in Chapel*; HPC Challenge; <u>http://chapel.cray.com/hpcc/hpcc09.pdf</u>

- 2. Chamberlain, Brad; Deitz, Steven; Navarro, Angeles (September 2011); *User-Defined Parallel Zippered Iterators in Chapel*; <u>http://pgas11.rice.edu/papers/ChamberlainEtAl-Chapel-Iterators-PGAS11.pdf</u>

- 3. Epperly, Thomas; Prantl, Adrian; Chamberlain, Bradford L (September 2011) *Composite Parallelism:Creating Interoperability between PGAS Languages, HPCS Languages and Message Passing Libraries*; <u>http://chapel.cray.com/papers/CompParallelismProgress.pdf</u>

- 4. Prantl, Adrian; Epperly, Thomas; Imam, Shams; Sarkar, Vivek (September 2011) Interfacing Chapel with traditional HPC programming languages; PGAS 2011; <u>http://pgas11.rice.edu/papers/PrantlEtAl-Chapel-Interoperability-PGAS11.pdf</u>

- 5. Sidelnik, Albert; Garzar´an, Mar´ıa J.; David Padua; Chamberlain, Bradford L. (April 2011) Using the High Productivity Language Chapel to Target GPGPU Architectures;; <u>https://www.ideals.illinois.edu/bitstream/handle/2142/18874/techreport\_chplgpu.pdf?sequen\_ce=2</u>

- Sridharan, S; etal (5/7/2011) A Scalable Implementation of Language-based software Transactional Memory fpr Transactional Memory for Distributed Memory Systems; Future Technologies Group Technical Report Series; ORNL; <u>http://ft.ornl.gov/pubs-archive/chplstm1-2011-tr.pdf</u>

- Weiland, Michèle ; Haddow, Thom (2009) ; Performance Evaluation of Chapel's Task Parallel Features; CUG 2009; <u>http://cug.org/5-</u> publications/proceedings\_attendee\_lists/CUG09CD/S09\_Proceedings/pages/authors/01-<u>5Monday/4A-Weiland/weiland-paper.pdf</u>

- 8. Wheeler, Kyle B. etal (June 2011) *The Chapel Tasking Layer Over Qthreads*; CUG 2011; <u>http://chapel.cray.com/publications/CUG11-wheeler.pdf</u>

| 3.2. X10 programming language | 3.2. | <b>X10</b> | programming | language |

|-------------------------------|------|------------|-------------|----------|

|-------------------------------|------|------------|-------------|----------|

| Owner / Development | IBM Research                                                        |  |

|---------------------|---------------------------------------------------------------------|--|

| Location            |                                                                     |  |

| Project Website     | http://x10-lang.org/                                                |  |

| Download Page       | http://x10-lang.org/software/download-x10/release-list.html         |  |

| Plaforms Available  | AIX/Power, Linux/Power, Cygwin/x86, Linux/x86 and x86_64, MacOS/x86 |  |

|                     | and x86_64                                                          |  |

#### **3.2.1. Overview**

X10 is a parallel asynchronous Partitioned Global Address Space language based on Java and developed by IBM. Like Chapel and Fortress, the X10 project started in 2006 as a response to the DARPA HPCS program.

Because X10 is an extension to Java rather than an entirely new language, it is ostensibly easy to learn for Java developers. It uses Java math functions and garbage collection, and, like Java, uses regions and points for array manipulation. X10 incorporates ideas from object-oriented languages such as classes, objects, inheritance, and generic types; like functional languages, it also uses type inference, anonymous functions, closures, and pattern matching (Hudak, 2010).

From Chapel, Fortress, and X10: Novel Languages for HPC:

The name X10 is derived from the developers' aim to create, by 2010, a language that is ten times more productive than those languages and libraries that are commonly used for current HPC codes... The design goals for X10 are to create a language which enables the development of safe, scalable, analysable and flexible code. Java was chosen as a basis for X10 because it supports three out of these four goals. It is also a widespread and accepted modern OO language that is accompanied by reliable tools, libraries and documentation (Weiland, 2007).

X10 does not support Java concurrency, arrays, or built-in types, but adds several key concepts in order to support parallelism: *places* and *activities* (Weiland, 2007).

#### Places

A place is the X10 term for a unique memory location. X10 is designed so that the number of memory locations is distinct from the number of threads. Places are containers for activities and objects, and their number is fixed at launch. If an application is normally launched with mpirun, the number of places is equivalent to the number of MPI processes launched.

#### Activities

Activities are PGAS threads in X10. Activities can be dynamically created during program execution, unlike UPC or MPI, which maintain a fixed number of threads or processes for an entire run.

Every X10 program begins with a single activity in Place 0. X10 provides several keywords to control activities:

- The *at* keyword evaluates an expression at a particular place. Using at blocks the parent process until the evaluation completes. At can be used to read or write remote values (similar to MPI\_Put and MPI\_Get) or to invoke a remote method.

- The *async* statement causes an expression to be spawned in parallel as a child activity and evaluated asynchronously. Control proceeds immediately to the subsequent statement.

- The *finish* statement (finish{ async N; async N+1; ...} S) waits to perform statement S until all async statements N, N+1,... have completed. This is useful for identifying dependencies and implying a barrier.

- The *atomic* statement evaluates an expression atomically.

X10 is called an asynchronous PGAS language because of the ability to explicitly control concurrency through constructs such as async and finish. The independence of memory locations (places) and threads (activities) is a necessary precondition for this capability (Saraswat, 2008).

The stated motivation behind X10 is to provide a language that addresses the inherent complexities of the increasingly popular many-core architectures (of which nVidia Fermi and the Intel MIC are examples) in a single, unified programming model. The goals of the project are to create a language that is simple (hence its Java base), safe (from design errors, and through static checking), powerful (capable of expressing typical HPC codes), scalable, and universal (can be used and deployed on a host of architectures) (Hudak, 2010).

Two runtime environments are available for X10: A Java-based one, in which all places are in a single Java Virtual Machine, and a multi-process C++ runtime (Hudak, 2010).

## 3.2.2. Present State of the Model

We conducted several interviews with developers of the X10 language. According to a former developer (Sayantan Sur), X10 was not, at the time of the interview, robust enough to reliably support the more complex features of the language or to port a meaningful application (Sur, 2011). A current developer (David Grove) stated that there are X10 codes in existence with up to about 10,000 lines. He believes that the present state of the language is that it is 'more than a toy,' meaning that it is beginning to reach beyond the prototype phase. Grove acknowledged that a specific problem exists with sparse non-negative factorization, but said that X10 can perform at scale, and performs well at load balancing irregular applications. Grove noted that the 2.2 release of the software (released May 2011) has many improvements such as a finalized language specification, decent error messages, and a usable IDE. There is an eclipse-based debugger that interacts with gdb. He stated that this release should be a reasonable candidate for experimenting with HPC applications (Grove, 2011).

Sur noted that funding for X10 comes primarily from IBM Business Analytics, which is focused on cloud computing and a loosely coupled parallelism model. He believed that until there is strong funding from the HPC community, tightly coupled parallelism will not be well supported or tested (Sur, 2011). Grove noted that a collaboration with the Australian National University ANU Chem team was providing insight into what needed improvement in the language (Grove, 2011).

As of interview time, Grove estimated the X10 community at somewhere between 50 and 100 active participants (Grove, 2011).

Finally, according to the X10 website, "X10 is in active development, so the language and libraries are still changing, so coding to X10 is still a bit of a moving target. Notable current gaps include library

support, interoperability, IDE and compiler performance, and runtime performance of certain X10 idioms. Of course, we are actively working on all these issues" (IBM).

#### 3.2.3. Tool Availability

#### 3.2.3.1. Debugger

IBM developerWorks provides an X10 debugger called 'The IBM Parallel Debugger for X10 Programming.' The debugger consists of a client-side component and a host system component. The components talk to one another over a TCP/IP connection. Using the debugger on the client side requires the use of X10DT, the Eclipse-based IDE for X10 (IBM developerWorks).

The X10 Parallel Debugger is a fairly new product, so bugs are to be expected. However, the goal of the project is to provide a complete parallel debugger for X10 code, so in the long-term, it should be robust.

#### 3.2.3.2. Performance analysis tools

At present no performance tools specifically designed for native X10 code exist. However, a prototype performance tool based on the Parallel Performance Wizard (PPW) and the GASP interface has been proposed by Alan George of the University of Florida (IBM).

Additionally, there are several existing methods for doing performance analysis on X10 codes. The first method is to profile the C++ executables produced by X10; the X10 website suggests using Google profiling tools and Valgrind-based tools on  $x10c++^1$  executables (IBM).

The C++ X10 runtime also contains tracing options that can be set through environment variables. Allocations, serialization points, and messaging between places can all be traced; other tracing options are also available (IBM).

There are a number of suggestions and best practices for achieving optimal performance from your X10 application on the X10 Performance Tuning page (IBM) (see bibliography for link).

#### 3.2.3.3. Other Tools

Additional tools that are either proposed or in current development for X10 are described on the X10 Tool Development page (IBM) (see bibliography for link). Besides the novel performance toolset, tools in development include a consistency checker and a deterministic replay tool.

#### 3.2.4. Performance

We did not find published studies of the performance of X10 code compiled to C++.

Some of the X10 team has, however, conducted research on the performance of X10 compiled to Java. In the X10-to-Java case, KmeansSequential benchmark results lagged native Java by a range of factors depending on the X10 release; the latest release in the comparison was 2.1.2, released in February of 2011. That release took 1.8x as long to complete as the native Java implementation. KMeansSPMD performance was tested up to 12 places, with a maximum speed up of 7.7x using X10 release 2.1.2 (Takeuchi, 2011).

<sup>&</sup>lt;sup>1</sup> x10c++ executables are X10 executables that have been compiled to C++ code.

According to Grove, X10 code scales fairly well and is capable of running up to a few hundred or as many as 1000 cores – the HPC Challenge Benchmarks have been run at this scale (Grove, 2011). Sur stated that running at Terascale is not presently possible (Sur, 2011).

Sur also stated that the language is not yet performance competitive with C or C++ for serial applications. He estimated that this would take a number of years before it attains competitive equilibrium with C++ (Sur, 2011). Grove admitted that the X10 implementations of some codes tested underperforms, but he believed that this relates partly to the application code design and not strictly to the X10 language (Grove, 2011).

## 3.2.5. Suitability to LLNL Application Codes

Like Chapel, programming in X10 would be a radical shift for LLNL application code teams. However, this is not necessarily a negative if the shift provides benefit in the form of reduced time to code, large reductions in lines of code, and greater maintainability. Also like Chapel, at present X10 cannot exist as a secondary language; while C or C++ object files can be linked into an X10 application, the reverse is not possible. We are not aware of any BRAID-like projects to provide the capability to link against standalone X10 objects from a non-X10 program.

According to Sur, who developed the MPI runtime for X10, the present focus of X10 development is on making it suitable for use in distributed computing applications (Sur, 2011). Because these are more loosely coupled application codes than MPI parallel application codes, they do not stress the parallel runtime as much as a scientific application code would. This means that presently the language is not being heavily tested with tightly coupled scientific applications. Sur speculated that it would be a relatively long amount of time before X10 would be ready for parallel scientific application code development, partly because serial performance still significantly lags that of native C or C++ compiled code.

We asked Grove about the state of object compatibility between X10 objects and non-X10 objects. He said that it was possible to make calls to non-X10 functions from within X10, but that calling back into X10 from an external object was 'rough' and while perhaps feasible, not very elegant (Grove, 2011).

X10's asynchronous PGAS framework provides the programmer with greater flexibility than a standard PGAS model by allowing threads (activities) to be created dynamically and by making it possible for dynamic load balancing to occur. This means heterogeneous systems and applications that require load balancing should both be supported, increasing the potential for adoption. This may have value for some LLNL applications that exhibit workload heterogeneity.

Multidimensional arrays in X10 are declared as multidimensional, rather than as arrays of arrays as in C or C++. This can be beneficial for identifying programming errors and allowing for the memory layout of the implementation to be independent of the array reference notation (Brezin, 2010). Currently X10 does not appear to provide features equivalent to Chapel's domain maps or the distributions construct.

Like Chapel, X10 should greatly reduce the amount of code required for a particular parallel application, relative to the amount of code in an MPI-based or MPI/OpenMP code. This is due to the absence of message passing code, as global memory locations can be addressed as if they are local.

The fact that X10 is an extension to Java makes it a language that should be well understood by a large number of programmers. Like Java or C++, however, there are characteristics of the language syntax

that may make it more difficult for some programmers to maintain or work with. A solid understanding of existing classes will be necessary to optimally program and maintain application code, and in many cases there may be a nontrivial learning curve associated with acquiring this understanding.

## 3.2.6. Bibliography

- 1. Brezin, J. e. (2010, December 2). An Introduction to Programming with X10.

- 2. Grove, D. (2011, January). (C. Shereda, Interviewer)

- Hudak, D. (2010, October). The X10 Language and Methods for Advanced HPC Programming. Retrieved September 2011, from Ohio Supercomputer Center: <u>www.osc.edu/~dhudak/Site/About\_Me\_files/x10-tutorial.ppt</u>

- 4. IBM developerWorks. (n.d.). IBM Parallel Debugger for X10 Programming. Retrieved September 2011, from IBM developerWorks: <u>https://www.ibm.com/developerworks/mydeveloperworks/groups/service/html/communityvie</u> w?communityUuid=e3fb8100-3ee3-4402-bf67-bf66b29797ea

- 5. IBM. (n.d.). Frameworks and Libraries. Retrieved 10 2011, from X10: Performance and Productivity at Scale: <u>http://x10-lang.org/x10-community/x10-in-use/frameworks-a-libraries.html</u>

- 6. IBM. (n.d.). Tool Development. Retrieved 10 2011, from X10: Performance and Productivity at Scale: <u>http://x10-lang.org/x10-community/x10-in-use/tool-development.html</u>

- IBM. (n.d.). X10 Frequently Asked Questions. Retrieved September 2011, from X10: Performance and Productivity at Scale: <u>http://x10-lang.org/home/faq-list.html#FAQ-</u> <u>WhatisthepurposeofX10%3F</u>

- 8. IBM. (n.d.). X10 Performance Tuning. Retrieved September 30, 2011, from X10: Performance and Productivity at Scale: <u>http://x10-lang.org/documentation/performance-tuning.html</u>

- 9. Saraswat, V. (2008, May 21). APGAS: Programming for concurrency and distribution. Retrieved September 2011, from IBM TJ Watson Research Center: http://www.cs.waseda.ac.jp/gcoe/eng/whatsnew/img/080428VSaraswat1-APGAS.pdf

- 10. Sur, S. (2011, January 15). (C. Shereda, Interviewer)

- 11. Takeuchi, M. e. (2011). Compiling X10 to Java. X10 '11 (p. 10). San Jose, CA: <u>http://dist.codehaus.org/x10/documentation/papers/X10Workshop2011/CompilingX10ToJava.p</u> <u>df</u>.

- Weiland, M. (2007, October 10). Chapel, Fortress, and X10: Novel Languages for HPC. Retrieved September 2011, from HPCx, The University of Edinburgh: <u>http://www.hpcx.ac.uk/research/hpc/technical\_reports/HPCxTR0706.pdf</u>

| Owner / Development<br>Location | Sun Microsystems (Oracle), now an OpenSource project                                                                                       |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Project Website                 | <u>http://labs.oracle.com/projects/plrg/index.html</u><br><u>http://projectfortress.sun.com/Projects/Community</u> (Old page, broken link) |

| Download Page                   | http://java.net/projects/projectfortress/sources/sources/show                                                                              |

| Platforms Available             | Windows, Linux, Solaris, Mac OS X (Java Virtual Machine)                                                                                   |

## 3.3. Fortress

#### **3.3.1. Overview**

The name Fortress is derived from the developer's goal of creating a "secure FORTRAN," i.e. "a language for high-performance computation that provides abstraction and type safety on par with modern programming language principles" (Allen, et al., 2008). Fortress began as Sun Microsystem's entry into the DARPA HPCS program that began in 2002 with the goal of "enhancing human productivity as well as improving computer performance, scalability and availability" (Acocella, 2006). Fortress was not funded for Phase III of the project, which began in July 2006, losing out to competitors X10 (IBM) and Chapel (Cray). The project was then converted to an open-source project, which has an uncertain future, especially following the acquisition of Sun Microsystems by Oracle in 2009/10. A project page still exists for Fortress, now located on the Java.net website and there is apparently active work being done on the language, although it is not being promoted and seems to be a hobby limited to some of the initial team from Sun.

The core problems that Fortress seeks to address include working on:

- Mathematical Notation:

- Provide a way to better realize mathematical notation within high-performance programming language.

- Dimension Checking:

- Provide support for static checking of units and physical dimensions in an OO-type system that would allow polymorphic programs.

- Communication Efficiency:

- How to effectively move large amounts of data around while continuing computation?

- Memory Consistency:

- Large Global Shared Memory Space: "we must trade away the simplicity of cache coherent shared memory and manage consistency more explicitly" (Oracle, Project Fortress Overview)

- Synchronization:

- Absence of cache coherency requires major changes to the shared-memory synchronization mechanisms (compare and swap, load locked/store conditional) making certain operations more difficult (asynchronous message sends, barrier synchronization, and parallel prefix).

Use of mathematical notation is a key component of the Fortress language specification. The idea is that mathematical notation is a framework which has been developed over thousands of years, and is readily taught and understood by scientists and engineers alike. In fact, even the concept of dimensions and units of measure are built into the language allowing for equations and functions to carry this

information with them.

Fortress uses a large global shared memory space to get around problems involved with message passing frameworks. Currently there are few details about the specifics of how this will work in particular, though it's possible this information currently still resides on the Sun website pages, which have not completely been moved over to the Oracle servers.

Fortress aims to provide *inherent parallelization*. For instance, loops in Fortress are parallel unless they are explicitly performed using sequential generators. Individual iterations of a loop are treated by default as being completely independent, so that the compiler can parallelize them to take advantage of the hardware available.

#### 3.3.2. Present State of the Model

The first stable release (Version 1.0) of the Fortress language specification was released in April 2008, along with a compliant implementation targeting the Java Virtual Machine (Wikipedia). Currently there is a download link from the Java.net site which provides information about how to download the source code for the language and the compiler; however, at present there are no real programming examples and much of the documentation is missing or outdated.

The compiler is still actively being developed by Guy Steele and others. Currently only a subset of the language specification has been implemented. Guy Steele has created web entries in 2011 concerning performance and implementation of the compiler, and the team has recent publications in top tier programming language conferences. However, most of these publications highlight problems that affect many programming languages and the Fortress team's solutions to these problems, rather than focusing solely on the Fortress language.

#### 3.3.2.1. Robustness and Known Issues

Fortress was developed to run on the Java Virtual Machine which allows a very widespread audience for the language. Some estimates are that there are over 4.5 billion JVM-enabled devices and 6.5 million Java developers worldwide (Oracle, Learn about Java Technology). Such familiarity helps to alleviate some of the ramp-up required to adopt new programming languages or programming models.

Development and progress on Fortress beyond the language specification itself has been slow. There are a number of factors contributing to this, including Oracle's acquisition of Sun Microsystems in 2009/10 and the cancellation of funding under the DARPA HPCS program. Currently the development is handled primarily by the original Sun Programming Languages Team, now part of the Oracle Programming Languages Group, and their development has focused on adding functionality to the Fortress compiler.

#### 3.3.3. Tool Availability

Currently there is very little information regarding the tools available to Fortress developers. This is primarily due to the fact that the compiler is the primary development goal of the Fortress team, and currently does not fully implement the language specification. Due to the compiler being incomplete, there are no currently available tools for debugging or measuring the performance benefits of Fortress relative to other parallel models.

#### 3.3.4. Performance

Currently there are no performance numbers or porting examples available to compare Fortress to other prominent HPC languages.

#### 3.3.5. Suitability to LLNL Application Codes

Due to Fortress's distinction as being a "secure FORTRAN," the language is designed such that it would be familiar for a FORTRAN developer to pick up easily. Language syntax and an emphasis on units, dimensions, and mathematical notation are aimed at increasing the readability of the code by the physicists, chemists, engineers, and mathematicians that are the source of the content of an application (Steele & Maessen, 2006).

#### 3.3.6. Resources and Additional Information

Oracle Project Page: <u>http://labs.oracle.com/projects/plrg/index.html</u> Java.net Page: <u>http://java.net/projects/projectfortress/pages/Home</u> Wikipedia Page: <u>http://en.wikipedia.org/wiki/Fortress\_%28programming\_language%29</u>

Parallel Programming and Parallel Abstractions in Fortress: http://www.brics.dk/pilambda/old/docs/Aarhus-Fortress-Parallelism-2006public.pdf

#### 3.3.7. Bibliography

- Acocella, K. (2006, 11 21). IBM Press room 2006-11-21 DARPA Selects IBM for Supercomputing Grand Challenge. Retrieved 09 20, 2011, from IBM : <u>http://www-</u> 03.ibm.com/press/us/en/pressrelease/20671.wss

- 2. Allen, E., Chase, D., Hallett, J., Luchangco, V., Maessen, J.-W., Ryu, S., et al. (2008). The Fortress Language Specification. Sun Microsystems, Inc.

- 3. Oracle. (n.d.). Learn about Java Technology. Retrieved 08 25, 2011, from Java: http://www.java.com/en/about/

- 4. Oracle. (n.d.). Project Fortress Overview. Retrieved 08 25, 2011, from Oracle Labs: http://labs.oracle.com/projects/plrg/Fortress/overview.html

- 5. Steele, G., & Maessen, J.-W. (2006). Fortress Programming Language Tutorial. Ottawa, Canada: PLDI.

## 3.4. Cilk Plus Language Extensions

| Owner / Development<br>Location | Intel                                                                      |

|---------------------------------|----------------------------------------------------------------------------|

| Project Website                 | http://software.intel.com/en-us/articles/intel-cilk-plus/                  |

| Download Page                   | http://software.intel.com/en-us/articles/intel-software-evaluation-center/ |

| Platforms Available             | Windows, Linux, Intel based parallel machines                              |

#### **3.4.1. Overview**

Cilk Plus, the concept developed originally at MIT, has been made a part of Intel Parallel Building Blocks. It is fairly straightforward as an extension of C/C++. The language is meant to be processor oblivious, which provides the programmer scalability without the need to rewrite code in order to utilize new architectures with additional cores. As such it is targeted mainly at legacy code that may be easily parallelized through the aid of the Cilk Plus keywords and parallel constructs. The language does not contain constructs for multiple nodes and an existing framework such as MPI would be required for communication across nodes of a platform.

The main concept behind the Cilk Plus programming model is work-stealing. That is, when a *worker* (roughly equivalent to a thread) has completed all of its assigned work, it attempts to steal *strands*<sup>2</sup> of work from other workers. This allows for good load balancing across the cores running worker threads. Each worker is assigned a worker id, which is an integer ranging from 0 to *n*-1, where *n* is the total number of workers allocated (the default is the number of cores available on a node). Here, worker 0 is referred to as the user thread, which is where the serial sections of code are executed. The remaining workers are referred to as Cilk threads, and these are where the parallel sections of code are executed after work is load balanced. The user thread is also utilized during these parallel sections for a total of *n* executing threads. Work-stealing is handled by the Cilk Plus runtime system. (Frigo, 2011)

Cilk Plus contains only a handful of keywords that control the bulk of the parallel related tasks that a programmer would use. These are the *cilk\_spawn*, *cilk\_sync*, and *cilk\_for* keywords. The language provides additional features such as elemental functions that take advantage of vector operations available on the hardware. Definitions for reductions are present to simplify certain codes.

The most commonly used keyword in Cilk Plus is *cilk\_spawn*, which is used to branch parallel sections of code. Each spawn creates a strand of work that is scheduled for a worker to process. Both the user thread and Cilk threads may be used to perform spawned work, and the default thread that runs the strand is the parent thread that spawned it. If and only if there is a larger quantity of work to do, multiple strands are broken up to be processed by other workers.

Following a *cilk\_spawn* in which there are dependencies on the return from the spawn, the Cilk Plus program must provide a matching *cilk\_sync* to ensure that the spawned threads have finished their strands of work before moving forward. This synchronization point is local, meaning a parent thread may continue once its children threads have all finished, as opposed to a global synchronization, where all threads must finish. This allows for more fluid workflow control in a program, especially with respect to task-based parallelism.

<sup>&</sup>lt;sup>2</sup> A **strand** describes a serial section of the program. More precisely, the definition of a strand is "any sequence of instructions without any parallel control structures."

The *cilk\_for* keyword is used primarily where there is a higher level of data parallelism, where the many iterations in a standard for loop are independent of one another, allowing for parallel execution. One of the key advantages to using the *cilk\_for* keyword, as opposed to a standard loop with *cilk\_spawn* inside the iteration, is that the *cilk\_for* splits up the work using a divide-and-conquer approach. This decreases the overall execution time because it counters some of the overhead associated with the otherwise serialized spawning.

There is an optional compiler directive that allows the programmer to choose the granularity of *cilk\_for* parallelization. This is *#pragma cilk grainsize* where the value of the parameter may be an expression. The default grainsize chosen by the compiler if none is explicitly specified is:

#### min(512,N/(8\*p))

where N is the number of iterations, and p is the number of workers.

The Cilk Plus runtime provides a handful of API functions to obtain information such as the worker a strand is on as well as the modification of certain parameters. Through the runtime calls, programs may manually shutdown or initialize the runtime scheduler. This allows for the number of workers to be changed between parallel sections of code, for instance. This manual starting and stopping of the runtime may only be performed outside of *spawning functions*, that is, a function containing any one of the Cilk Plus keywords.

#### 3.4.2. Present State of the Model

Development for the predecessor of Cilk Plus began as simply Cilk at MIT around 1994 and has since been refined and adopted by Intel, with the release of Cilk Plus in 2010. In spite of the relatively young age of the language, because of its minimal size and background, essentially all of the functionality of the language is implemented. Furthermore, Intel has provided its own additions to the language to utilize certain features of target architectures, such as vector operations through elemental functions. The Cilk Plus language extension specification is currently only supported by the Intel C++ Compiler. Although Cilk Plus is meant to be, as per Intel, a language specification with the implementation dependent on the platform, at present it only runs on a select set of compatible processors. It is expected that the Cilk Plus implementation for the Intel C++ Compiler will continue to be refined.

Because Cilk Plus is an extension to C/C++, its compatibility with existing languages is excellent, especially considering the Babel project at LLNL provides the necessary glue to communicate between several of the HPC languages currently used (Epperly et al. 2011). Cilk Plus code is also compatible with OpenMP, and both OpenMP directives and Cilk Plus keywords may be present in the same code file. Although both of these languages use pthreads currently, they use separate thread pools. However, the program must not interweave the two thread pools, or it will break. A downside to using both Cilk Plus and OpenMP in the same program is that the Cilk Plus runtime negatively affects the performance of OpenMP – Cilk Plus will steal processing time from OpenMP in order to execute (Intel Documentation, 2010). This issue may be preventable, although we did not determine a method for doing so.

Cilk Plus currently operates in a manner similar to the specifications of the MIT Cilk releases (MIT Supertech 1998). As such it both benefits from the advantages, such as load balancing, and suffers from the same pitfalls as its predecessor. Perhaps the most critical pitfall of Cilk Plus is its high overhead. When compiling Cilk Plus code, both fast and slow versions are created for nano- and micro-scheduling,

respectively. A function call to even the fast version requires the allocation of the procedure's frame, saving of the procedure state, checking for stolen frames, freeing frames, and a frame pointer. The slow version induces extra overhead by extracting arguments through the frame pointer and by managing synchronization with potential child procedures on neighboring cores. All of the excess work-stealing tasks not present in a serial implementation are also unpreventable. This is because when a Cilk Plus spawning function spawns work, the thread that it is located on is assigned the entirety of that work. It is then the responsibility of the other Cilk threads to steal the excess work from the original thread. This means that work-stealing in a parallel algorithm using Cilk Plus is inevitable. It is unclear how much more the current mechanism may be optimized, given the same framework. (Ganesh, 2011)

#### 3.4.2.1. Robustness and Known Issues

T he functionality of the language is implemented, and these features are fairly robust, albeit less than optimal in terms of performance. Given the simplicity of the language extension there is not much chance for a programmer to make errors when coding. The tests we ran regarding local synchronization indicate that the language appears to scale well with increased core counts. The work-stealing mechanism performs load balancing fairly reliably and a load imbalanced scenario performs similarly to that of a load balanced scenario. We believe this can be attributed to the way that Cilk threads steal from the main worker thread.

There appears to be an underutilization of processor cores for relatively small amounts of work. Although related to the mechanism behind the work-stealing, Cilk Plus does not give all of the available processors work at the start of a parallel section, so worker threads incrementally steal work. In some instances, not all of the cores are utilized, with a larger bulk of the work being performed sequentially on only a few cores. When all the processors were utilized, the runtime scheduler occasionally hangs prior to the utilization of the last remaining core, often equivalent to the same amount of time required for a single iteration. It is possible that these runtime issues have been resolved with the newest version of the Intel C++ Compiler; the issue was seen with version 12.0.191.

#### 3.4.3. Tool Availability

There are several tools available for Cilk Plus, both for debugging and for profiling. Specific to Cilk Plus are *cilkscreen* and *cilkview*, which are bundled with the SDK. *CilkScreen* may be used for race detection across the parallel tasks in a program, while *CilkView* generates performance data and calculates performance estimates, which it then uses to visualize the application performance graphically. Intel also provides extensions to Microsoft Visual Studio in its Intel Parallel Debugger for both viewing the execution flow of a Cilk Plus parallelized code and for viewing the Cilk Plus thread stack for further analysis. Finally, the Intel C++ Compiler can turn a Cilk Plus program into its equivalent "C-elision," where all the keywords and parallel constructs are replaced or removed, serializing the code. The resulting executable may then be debugged with any number of compatible debuggers (e.g. gdb) for correctness.

#### 3.4.4. Performance

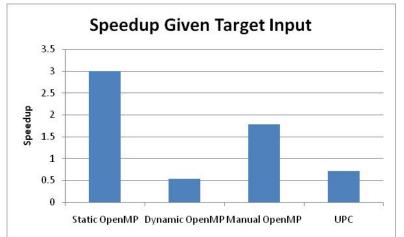

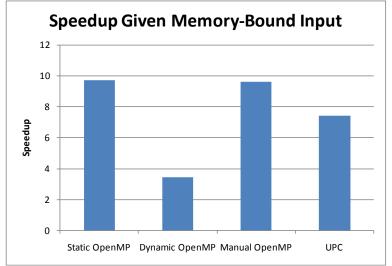

In comparing a port of the ASC Sequoia benchmark, CLOMP, to the original OpenMP implementation, we found that Cilk Plus underperforms in a rather diverse parameter space, even though the best-case implementation (without synchronization) is comparable to that of OpenMP. The exception is the test for synchronization where Cilk Plus, likely due to the local nature of the synchronization, not only outperforms, but also appears to scale better than the standard barrier. In discussions with the Cilk Plus development team, the lack in performance was attributed to the overhead of the work-stealing mechanism, which, in this case, is rather severe. For the "target input" of the CLOMP benchmark, it was found that Cilk Plus experienced slowdowns relative to the serial version. When increasing the amount

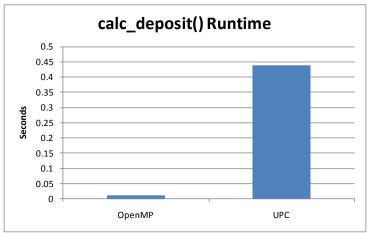

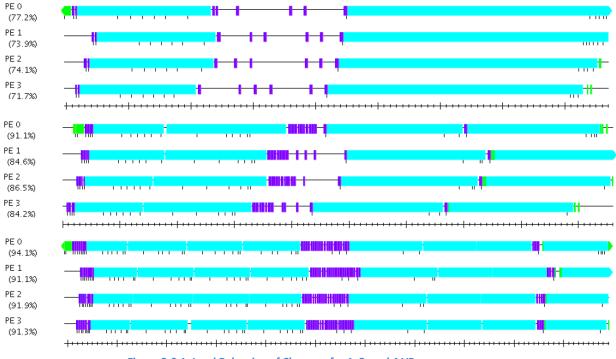

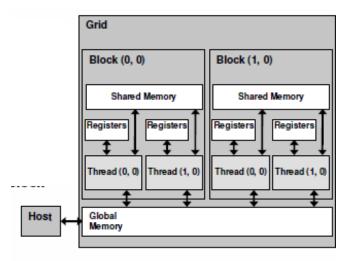

of work per iteration, the ported program performed comparably with OpenMP dynamic scheduling, and although this experienced some moderate speedups, it was still slow. (Hewitt & Ganesh, 2011)