# ANALYSIS AND OPTIMIZATION OF GRAPHENE FET BASED NANOELECTRONIC INTEGRATED CIRCUITS

Shital Joshi

Dissertation Prepared for the Degree of DOCTOR OF PHILOSOPHY

### UNIVERSITY OF NORTH TEXAS

May 2016

APPROVED:

Saraju P. Mohanty, Major Professor Elias Kougianos, Co-Major Professor JungHwan Oh, Committee Member Xiaohui Yuan, Committee Member Barrett Bryant, Chair of the Department of Computer Science and Engineering Costas Tsatsoulis, Dean of the College of Engineering Costas Tsatsoulis, Dean of the Robert B. Toulouse School of Graduate Studies Joshi, Shital. *Analysis and Optimization of Graphene Fet Based Nanoelectronic Integrated Circuits*. Doctor Philosophy (Computer Science and Engineering), May 2016, 141 pp., 12 tables, 54 figures, references, 130 titles.

In summary, the dissertation is to expected to aid the state of the art in following ways: 1) A non-EDA based tool has been used to characterize the device and measure the circuit performance. The results well matches to that obtained from the EDA tools. This tool becomes very handy for new device concepts when the simulation needs to be fast and accuracy can be tradeoff with. 2)Since an analog domain lacks well-design design paradigm, as compared to digital domain, this dissertation considers case study circuits to design the circuits and apply optimization. 3) Performance comparison of GNRFET based SRAM to the conventional silicon based SRAM shows that with maturation of the fabrication technology, graphene can be very useful for digital circuits as well. Copyright 2016 by Shital Joshi

#### ACKNOWLEDGMENTS

This dissertation have been possible due to guidance, support, trust and love of few people. So, I would like to express my sincere gratitude to all of them.

My foremost gratitude goes to my major Professor Dr. Saraju P. Mohanty for his kind guidance and support. I am also grateful my co-major Dr. Elias Kougianos for all his help. I am very grateful to them for their easy access and at the same time very thankful for their countless hours on discussing and refining the ideas. They helped me to grow immensely, both as a person and as a researcher. They taught me the "divide-and-conquer" method in problem solving which helped me to look the problem from different perspective.

I am thankful to Dr. JungHwan Oh and Dr. Xiaohui Yuan for serving on my dissertation and qualifying examination committees. Likewise, I would like to thank the department, including non-academic staffs, for their support and encouragement during this entire period.

Lastly, but not least, words are not enough to express how grateful I am for the endless love, support and sacrifices of my family. I hope this dissertation justifies for their effort.

## TABLE OF CONTENTS

| ACKNOWLEI    | DGMENTS                                           | iii  |

|--------------|---------------------------------------------------|------|

| LIST OF TABI | LES                                               | vii  |

| LIST OF FIGU | JRES                                              | viii |

| CHAPTER 1 I  | NTRODUCTION AND MOTIVATION                        | 1    |

| 1.1.         | Issues for Nanoscale MOSFETs                      | 3    |

| 1.2.         | Challenges for Graphene Based Electronics         | 6    |

| 1.3.         | Graphene as Material                              | 8    |

| 1.4.         | Graphene Based Devices                            | 9    |

| 1.5.         | Graphene Based Circuits                           | 9    |

| 1.6.         | Application of Graphene                           | 10   |

| 1.7.         | Motivation for this Research                      | 14   |

| 1.8.         | Organization of this Dissertation                 | 15   |

| CHAPTER 2 C  | GRAPHENE NANO-ELECTRONICS: AN OVERVIEW            | 17   |

| 2.1.         | Graphene as a Material                            | 17   |

| 2.2.         | Graphene Based Devices                            | 25   |

| 2.3.         | Graphene Based Integrated Circuits                | 34   |

|              | 2.3.1. Low Noise Amplifier (LNA)                  | 37   |

|              | 2.3.2. Ambipolar Electronics                      | 38   |

|              | 2.3.3. Further Options for Graphene Devices       | 41   |

| 2.4.         | Novel Contribution of this Dissertation           | 41   |

| CHAPTER 3    | VERILOG-A BASED MODELING AND ANALYSIS OF GRAPHENE |      |

| C            | CIRCUIT                                           | 43   |

| 3.1.      | Why Verilog-A Model is Necessary                           | 45 |  |

|-----------|------------------------------------------------------------|----|--|

| 3.2.      | Discussion of Device Structure                             |    |  |

| 3.3.      | 3.3. Device Level Modeling and Simulation Results          |    |  |

| 3.4.      | 3.4. Verilog-A Simulation of GFET Based Case Study Circuit |    |  |

| 3.5.      | 3.5. Verilog-A/SPICE Based Modeling and Simulation Flow    |    |  |

| 3.6.      | Experimental Setup of Results                              | 52 |  |

| CHAPTER 4 | SIMSCAPE BASED MODELING AND ANALYSIS OF GRAPHENE           |    |  |

|           | CIRCUIT                                                    | 58 |  |

| 4.1.      | Verilog-A/SPICE Versus Simscape                            | 59 |  |

| 4.2.      | Why Simscape <sup>®</sup> is Necessary                     | 60 |  |

| 4.3.      | Simscape Based Modeling and Simulation Flow                | 61 |  |

| 4.4.      | Experimental Setup of Results                              | 63 |  |

| 4.5.      | Case Study 1: GFET Based Amplifier Circuit                 | 65 |  |

|           | 4.5.1. Theoretical Perspective                             | 65 |  |

|           | 4.5.2. Simscape <sup>®</sup> Modeling of the LNA           | 69 |  |

| 4.6.      | Case Study 2: Graphene Based Oscillator Design             | 69 |  |

|           | 4.6.1. Theoretical Perspective                             | 70 |  |

|           | 4.6.2. Simscape <sup>®</sup> Modeling of the Oscillator    | 75 |  |

| CHAPTER 5 | OPTIMIZATION FOR GRAPHENE BASED CIRCUITS                   | 78 |  |

| 5.1.      | Why Optimization is Necessary                              | 79 |  |

| 5.2.      | Introduction to Optimization                               | 80 |  |

|           | 5.2.1. Swarm Intelligence                                  | 81 |  |

| 5.3.      | Proposed Optimization Design Flow                          | 89 |  |

| 5.4.      | Specific Algorithm                                         | 90 |  |

| 5.5.      | Results                                                    | 92 |  |

| CHAPTER 6 | GRAPHENE BASED DIGITAL CIRCUITS DESIGN                     | 98 |  |

| 6.1.      | Advantages of Graphene Based SRAM                          | 99 |  |

|           |                                                            |    |  |

| 6.2            | Introduction and Working Principle of SRAM               |     |

|----------------|----------------------------------------------------------|-----|

|                | 6.2.1. Design of graphene Based SRAM                     | 100 |

|                | 6.2.2. Working Principle of SRAM                         | 107 |

| 6.3            | . Graphene Nanoribbon Field Effect Transistor (GNRFET)   | 109 |

| 6.4            | . SRAM Design Verification                               | 111 |

|                | 6.4.1. Read Stability and Write ability of the SRAM Cell | 113 |

| 6.5            | . Experimental Results                                   | 122 |

| CHAPTER        | R 7 CONCLUSION AND FUTURE RESEARCH                       | 127 |

| 7.1            | . Summary and Conclusion                                 | 127 |

| 7.2            | . Future Research                                        | 128 |

| BIBLIOGRAPHY 1 |                                                          | 129 |

### LIST OF TABLES

| Table 1.1. | Performance Metric for "End-of-the-roadmap" CMOS 2020 [2]. | 2   |

|------------|------------------------------------------------------------|-----|

| Table 3.1. | GFET Device Parameters [60, 62].                           | 55  |

| Table 3.2. | Characteristization of GFET Based LC-VCO [60, 62].         | 55  |

| Table 4.1. | GFET based Amplifier Figures-of-Merit                      | 70  |

| Table 4.2. | GFET based Oscillator characterization.                    | 76  |

| Table 5.1. | GFET-based LC-VCO Design Variables and Constraints.        | 92  |

| Table 5.2. | Multi-Swarm Optimization Algorithm Parameters.             | 94  |

| Table 5.3. | Characteristics of the Optimal LC-VCO.                     | 97  |

| Table 6.1. | GNRFET device parameters.                                  | 110 |

| Table 6.2. | SRAM Transistor Sizing                                     | 114 |

| Table 6.3. | Cell stability comparison                                  | 121 |

| Table 6.4. | Average Power Consumption Comparison of SRAM.              | 126 |

### LIST OF FIGURES

|              | I                                                                                | Page |

|--------------|----------------------------------------------------------------------------------|------|

| Figure 2.1.  | Various allotropes of carbon. [Source: Wikipedia through Wikimedia               |      |

|              | Commons licence for free to use].                                                | 18   |

| Figure 2.2.  | Electronic Dispersion in Graphene. After [103].                                  | 20   |

| Figure 2.3.  | At low energy, bandstructure as two cones touches at the Dirac point, where      |      |

|              | Fermi level determines the nature of the doping and the transport carrier. After | •    |

|              | [12].                                                                            | 21   |

| Figure 2.4.  | Transfer Curve showing graphene resistance as a function of gate voltage.        |      |

|              | After [ <b>65</b> ].                                                             | 22   |

| Figure 2.5.  | Future Electronic due to graphene                                                | 23   |

| Figure 2.6.  | Graphene based SpinFET. After [3].                                               | 27   |

| Figure 2.7.  | Bilayer pseudo spin field effect transsitor (BiSFET) Structure. After [98].      | 28   |

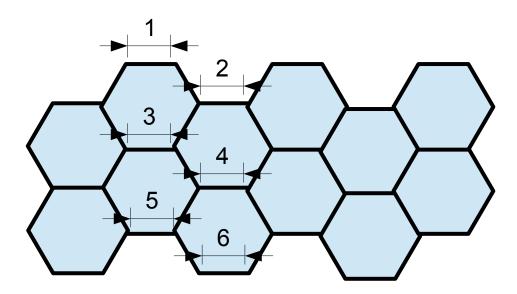

| Figure 2.8.  | Graphene width defined in terms of dimer                                         | 30   |

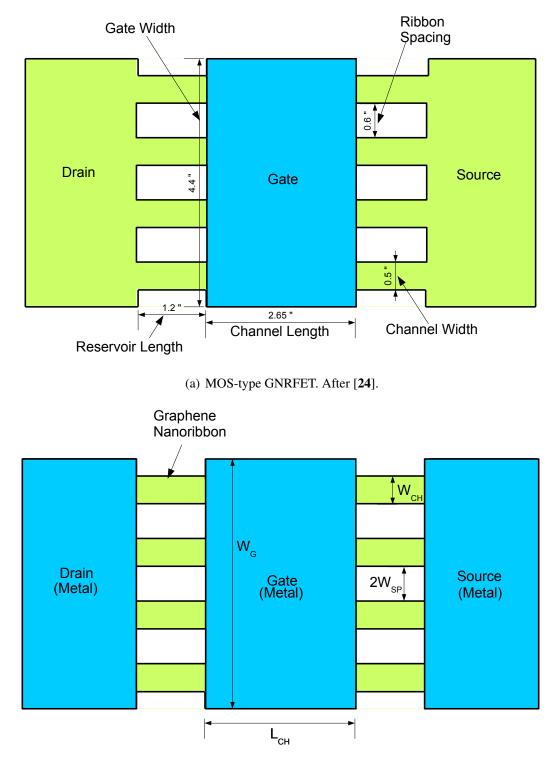

| Figure 2.9.  | GNRFET and its types                                                             | 31   |

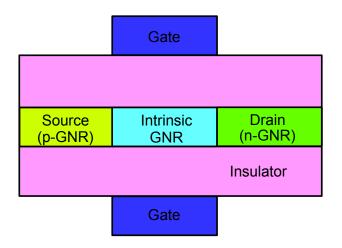

| Figure 2.10. | Double gate GNRTFET. After [124].                                                | 33   |

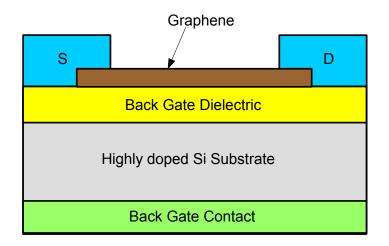

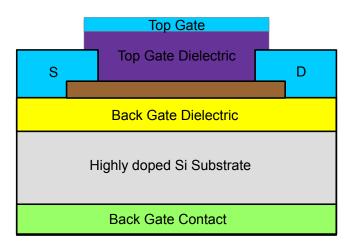

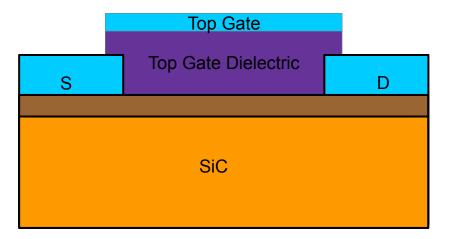

| Figure 2.11. | Different GFET Configuration. After [60, 65, 77].                                | 35   |

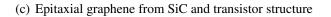

| Figure 2.12. | Transfer curve of GFET. After [130].                                             | 39   |

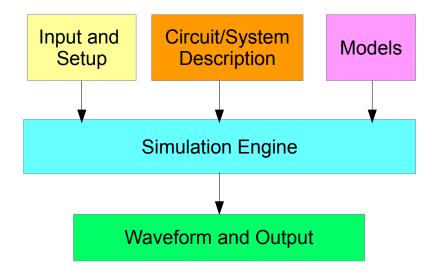

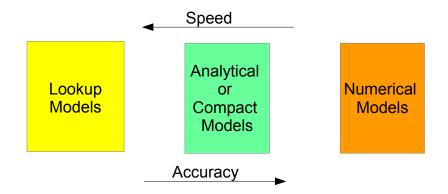

| Figure 3.1.  | Typical IC Prototpye Design Flow. After [77].                                    | 43   |

| Figure 3.2.  | Accuracy Vs Speed Comparison of different types of model [77].                   | 44   |

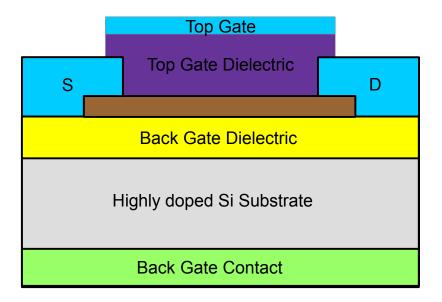

| Figure 3.3.  | Dual gate graphene transistor. After [65].                                       | 46   |

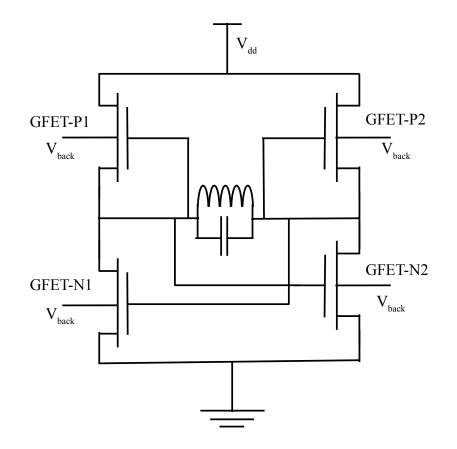

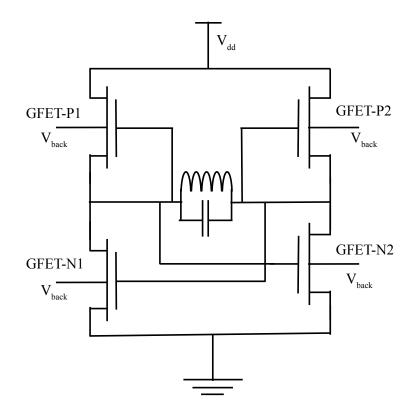

| Figure 3.4.  | GFET based cross coupled version of LC-VCO. After [62,77].                       | 51   |

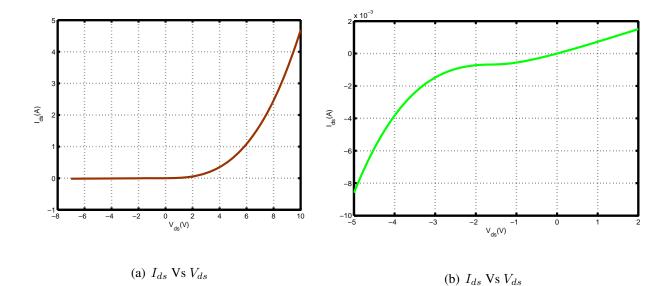

| Figure 3.5.  | (a) $I - V$ curve of NFET around operating region. (b) $I - V$ curve of PFET     |      |

|              | around operating region.                                                         | 56   |

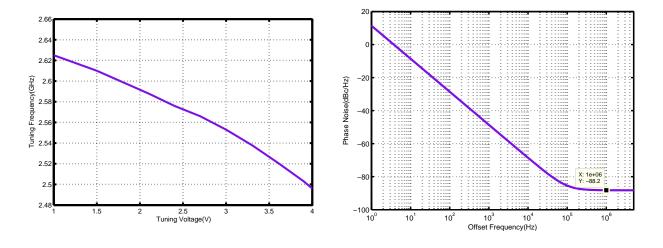

| Figure 3.6.  | (a) Tuning range (b) Phase noise Characteristics of the baseline GFET based      |      |

|              | LC-VCO.                                                                          | 56   |

| Figure 3.7.  | Characteristics of the GFET based LC-VCO.                                         | 57 |

|--------------|-----------------------------------------------------------------------------------|----|

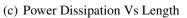

| Figure 4.1.  | SPICE versus Simscape <sup>®</sup> based Design Simulation Flow.                  |    |

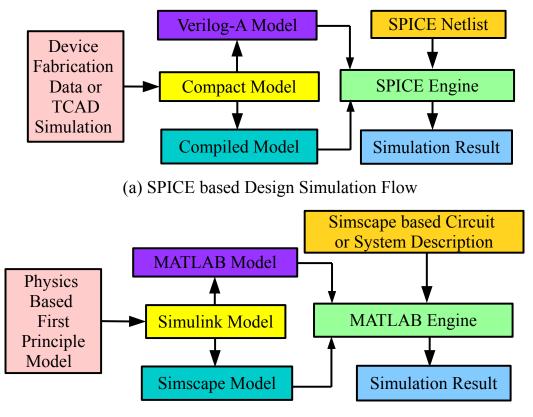

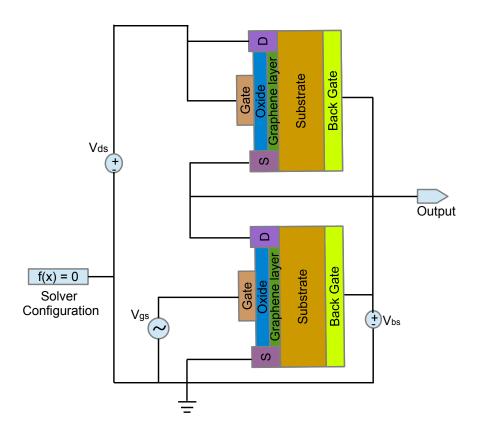

| Figure 4.2.  | Simscape simulation setup for GFET device simulation. After [4].                  |    |

| Figure 4.3.  | Simscape simulation setup for GFET device simulation.                             |    |

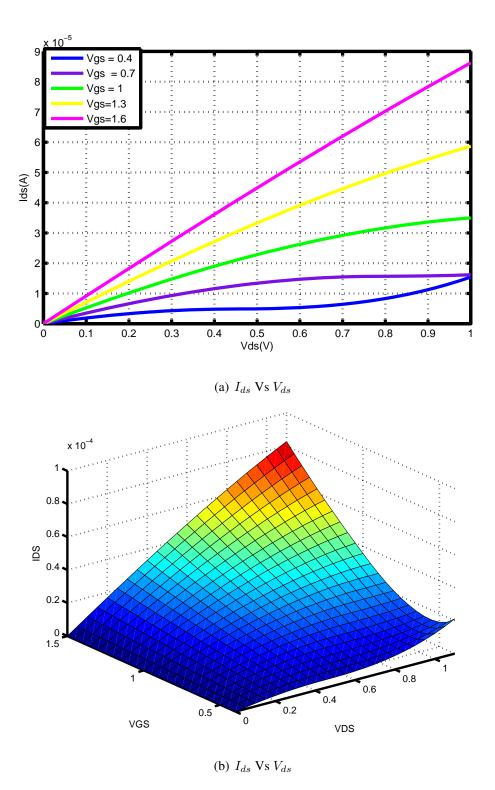

| Figure 4.4.  | $I - V$ characteristics for discrete and continuous values of $V_{gs}$ for N-type |    |

|              | GFET.                                                                             | 66 |

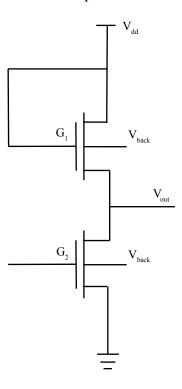

| Figure 4.5.  | Schematic of a GFET based LNA circuit. $G_1$ is the load transistor and $G_2$ is  |    |

|              | the amplifier.                                                                    | 67 |

| Figure 4.6.  | GFET charasteristics (amplifier device $G_2$ in the LNA).                         | 70 |

| Figure 4.7.  | Simscape <sup>®</sup> Experimental Setup for LNA Simulation.                      | 71 |

| Figure 4.8.  | GFET based LNA charasteristics.                                                   | 72 |

| Figure 4.9.  | Schematic of LC oscillator using GFET (Same Circuit presented in the              |    |

|              | previous Chapter.).                                                               | 73 |

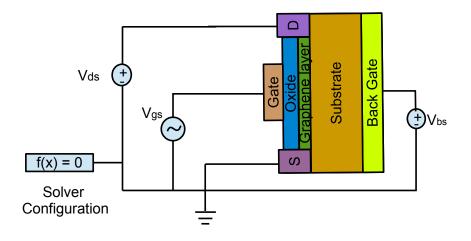

| Figure 4.10. | (a) $I - V$ characteristic of NFET for different top gate voltages. (b) Surface   |    |

|              | plot showing $I - V$ curve for continuous change of the top gate voltage.         | 74 |

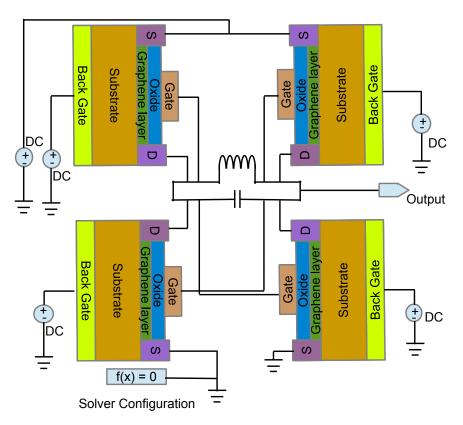

| Figure 4.11. | Simscape <sup>®</sup> Model of Graphene based Oscillator.                         | 75 |

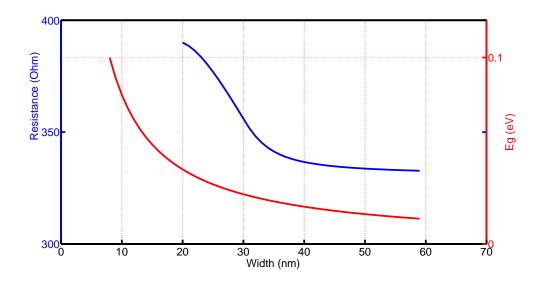

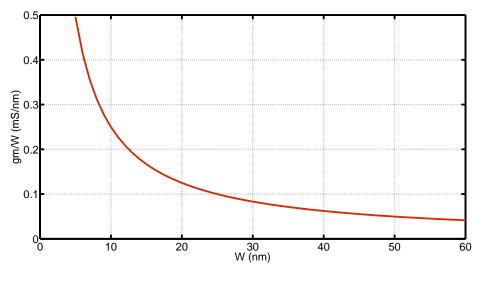

| Figure 4.12. | (a) $I - V$ Characteristic of PFET around operating point. (b) Transconductance   | •  |

|              | of PFET for variation in width. (c) Drain to source conductance of PFET           |    |

|              | encompassing operating point. (d) $I - V$ characteristic of NFET around           |    |

|              | operating point.                                                                  | 77 |

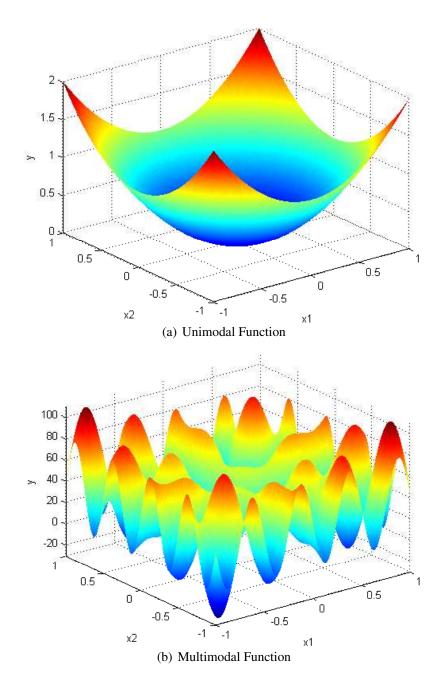

| Figure 5.1.  | Types of fitness function possible to use in this research.                       | 82 |

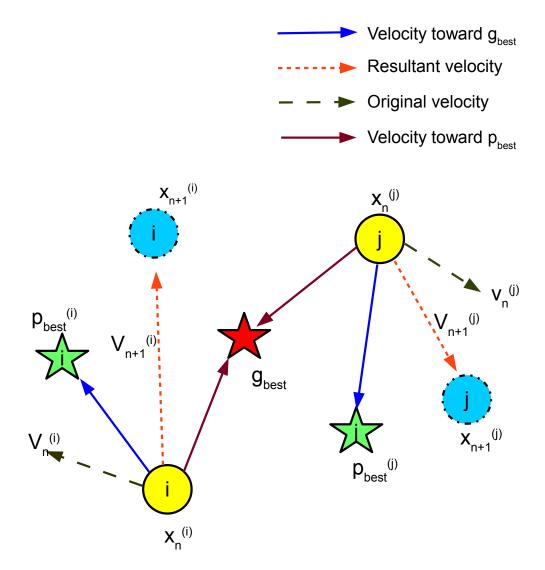

| Figure 5.2.  | Particle velocity updating where particles i and j are accelerated to wards their |    |

|              | best location, $g_{best}$ and $p_{best}$ [66].                                    | 84 |

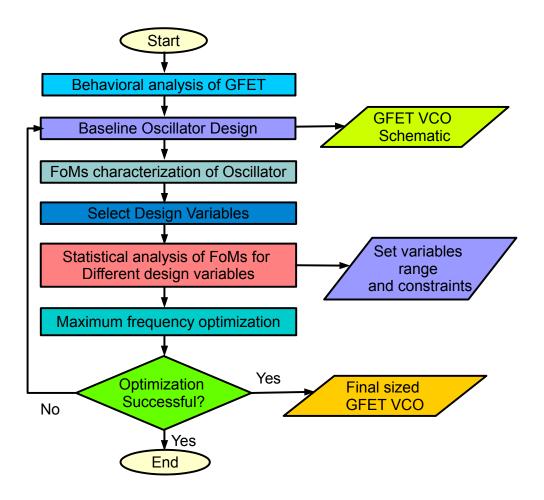

| Figure 5.3.  | Design Flow of GFET based LC-VCO Circuit Optimization [66].                       | 90 |

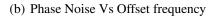

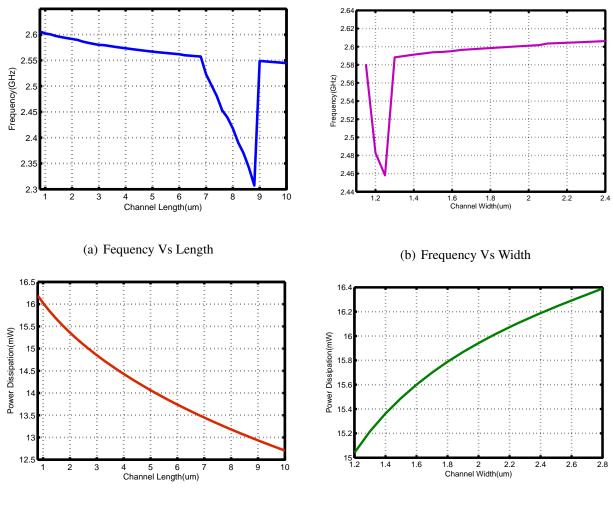

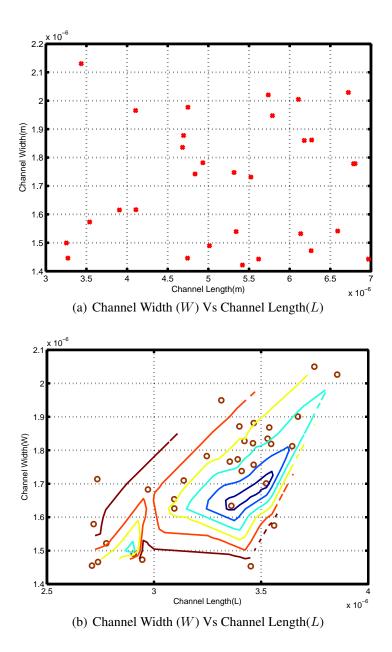

| Figure 5.4.  | GFET based LC-VCO Optimization: (a) Initial particles (x), (b) particles after    |    |

|              | $20^{th}$ iteration (o).                                                          | 95 |

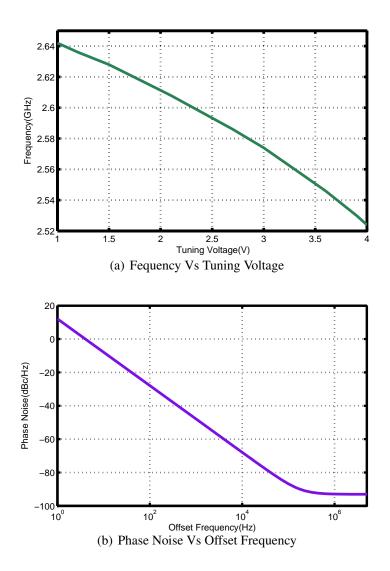

| Figure 5.5.  | (a) Tuning range of optimized LC- VCO (b) Phase noise of Optimized GFET           |    |

|              | based LC-VCO.                                                                     | 96 |

|              |                                                                                   |    |

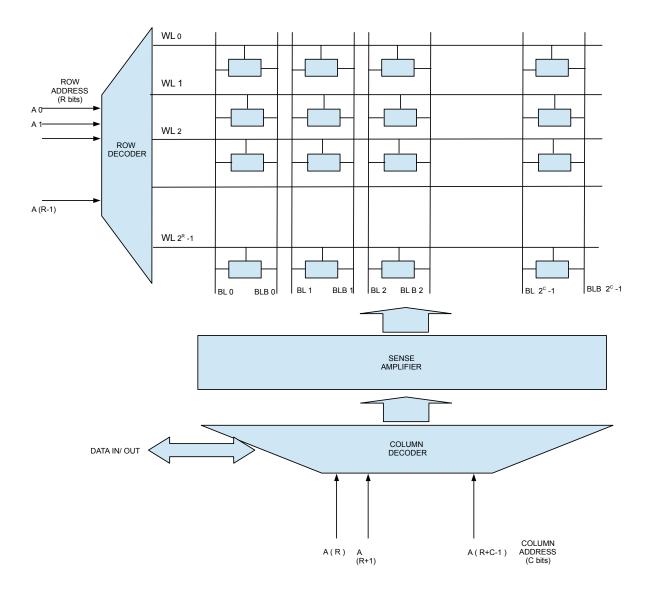

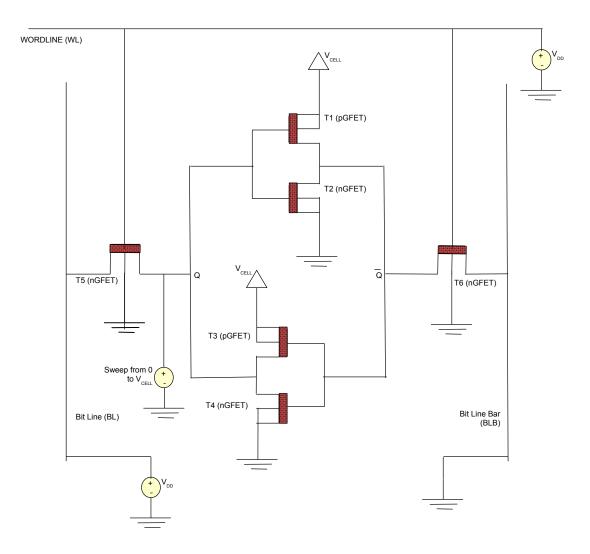

| Figure 6.1.                                                          | Complete Block Diagram of a SRAM array.                               |     |

|----------------------------------------------------------------------|-----------------------------------------------------------------------|-----|

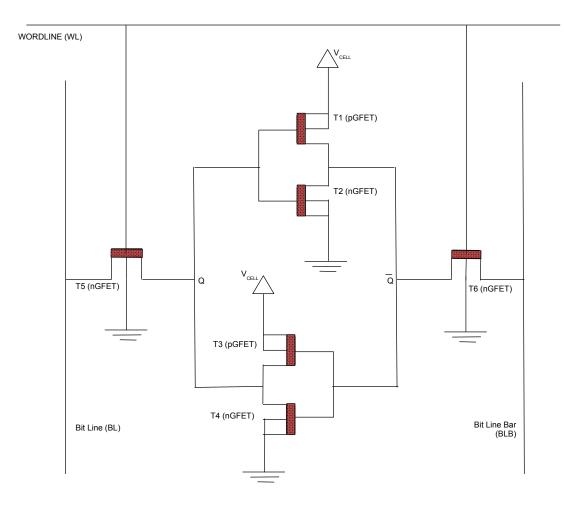

| Figure 6.2.                                                          | A GNRFET based 6T based SRAM Cell.                                    |     |

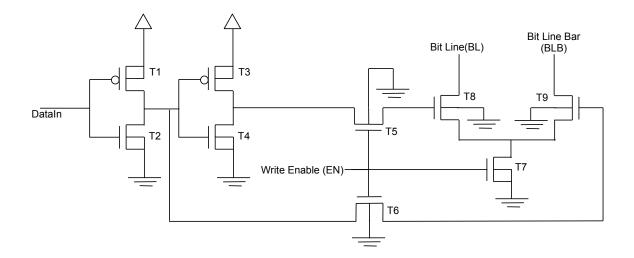

| Figure 6.3.                                                          | Write Driver for SRAM                                                 | 104 |

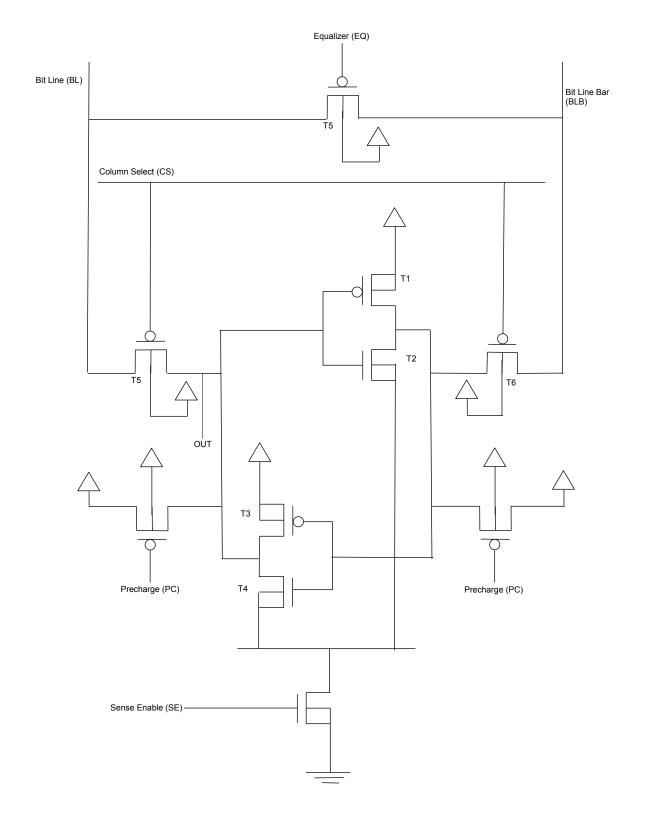

| Figure 6.4.                                                          | igure 6.4. Sense Amplifier for SRAM                                   |     |

| Figure 6.5.                                                          | Figure 6.5. SB-type GNRFET                                            |     |

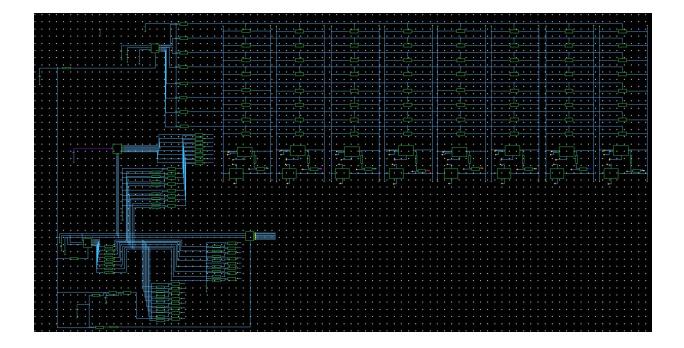

| Figure 6.7.                                                          | Complete Design of SRAM with peripherals                              | 111 |

| Figure 6.6.                                                          | Graphene Based Inverter.                                              | 112 |

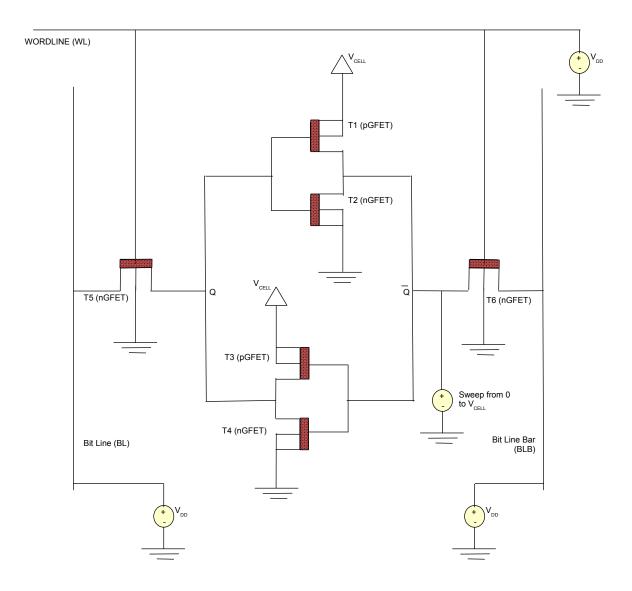

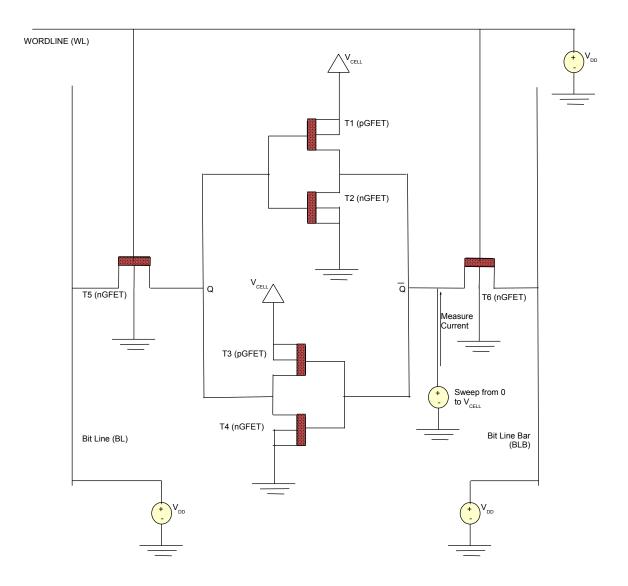

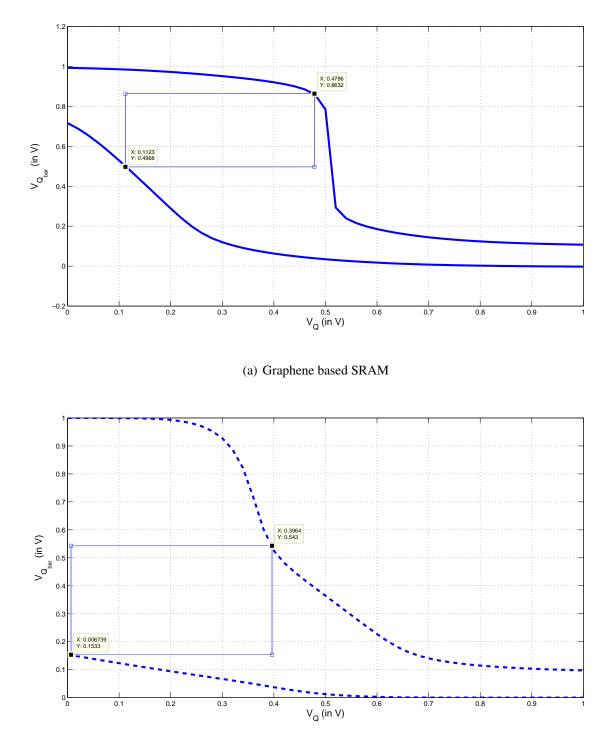

| Figure 6.8.                                                          | Circuit configuration for RSNM Calculation                            | 114 |

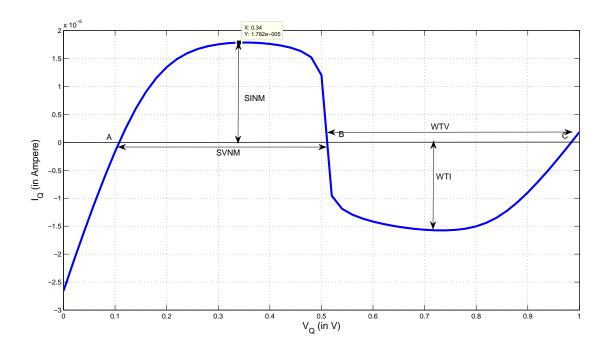

| Figure 6.9.                                                          | Simulated waveform for RSNM calculation for GEFT based SRAM (shown by |     |

|                                                                      | solid line) and Silicon transistor based SRAM (shown by dotted line). | 115 |

| Figure 6.10.                                                         | Circuit configuration for SINM Calculation                            | 116 |

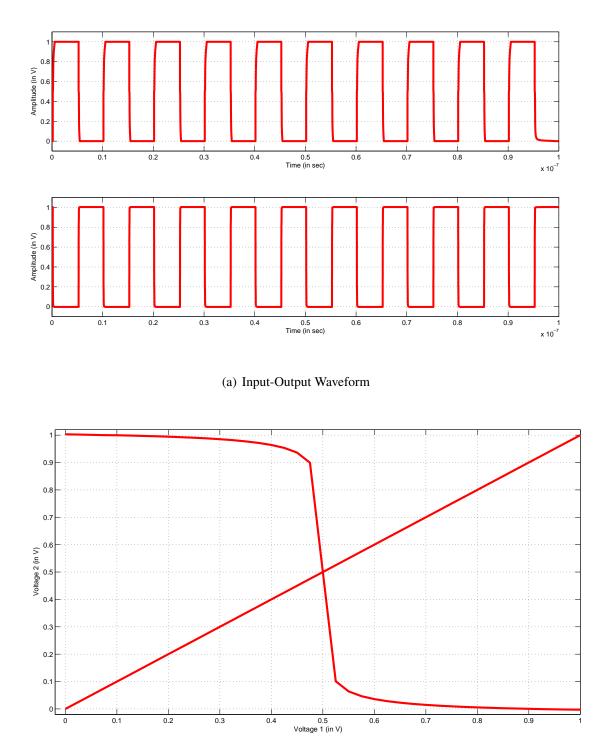

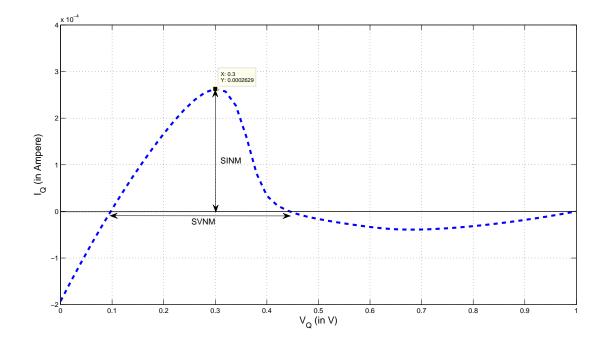

| Figure 6.11. Simulated waveform for SINM calculation                 |                                                                       | 117 |

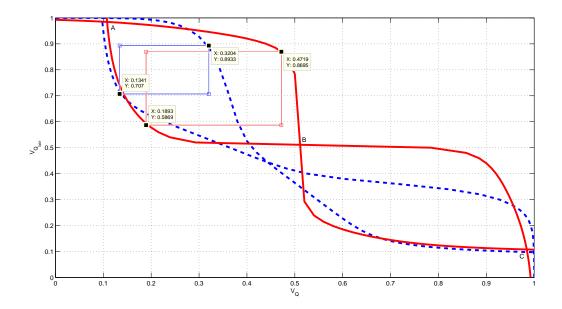

| Figure 6.12. Circuit configuration for WNM Calculation.              |                                                                       | 119 |

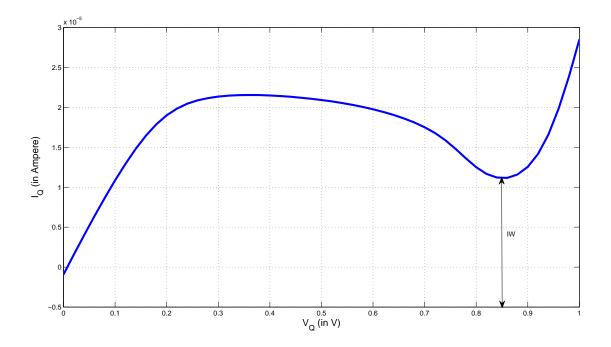

| Figure 6.13. Simulated waveform for WNM calculation                  |                                                                       | 120 |

| Figure 6.14. Simulated waveform for Writeability current calculation |                                                                       | 121 |

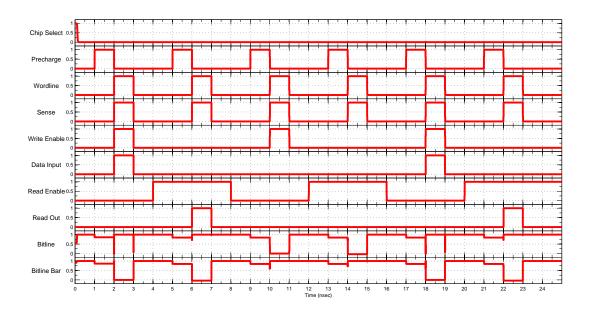

| Figure 6.15.                                                         | Timing Waveform for 1 bit SRAM Cell.                                  | 122 |

| Figure 6.16.                                                         | igure 6.16. Timing Waveform for 8x8 SRAM Array                        |     |

| Figure 6.17.                                                         | Instantaneous Power Consumption of GFET based SRAM.                   | 124 |

| Figure 6.18.                                                         | Instantaneous Power Consumption of Si based SRAM.                     | 125 |

#### CHAPTER 1

#### INTRODUCTION AND MOTIVATION

Silicon technology has undergone an unprecedented advancement in terms of device density, performance, productivity and cost. From the past three decades, the complementary metaloxide-semiconductor (CMOS) has been scaled down by following the "constant field scaling" theory. The constant field scaling theory says that for the electric fields in the new scaled device to remain the same, the scaling has to be done by a factor of  $\alpha$  (where  $\alpha = \sqrt{2}$  for geometric scaling) to the device dimensions  $(W, L, t_{ox})$  and to the device voltages  $(V_{dd} \text{ and } V_{th})$ . Following this simple scaling theory, designers are able to increase the number of transistors per unit area from past few decades. However CMOS technology scaling in nanometer regime is accompanied by many serious problems [77, 79, 80]. Particularly beyond 10 nm, small-geometry effects like increase in the leakage currents, large threshold variations, gate losing control over channel, increase contact resistance are some of the many serious problems. With supply voltage  $V_{DD}$  approaching 1 V, it is difficult to lower the threshold voltage  $(V_{th})$ . As threshold voltage is proportional to the thermal voltage ( $V_t = KT/q$ ), it is not possible to scale down the thermal voltage (K and q being constants) without having adverse effect in the device performance. It is from this point onwards, the scaling of threshold voltage becomes a problem. Also with the reduction in the threshold voltage, the sub-threshold leakage current increases exponentially. This leakage dominates the total leakage current in the future electronics. It is thus necessary to keep enough margin for  $V_{th}$  variation from reaching its minimum possible value so as to control this sub-threshold leakage. Also, for high performance logic technology, it is necessary to maintain the value of  $(V_{DD} - V_{th})$  to a certain level [64]. Clearly, there is a trade off between performance (speed) and efficiency (leakage power) in the future electronics.

In order to reduce the short channel effect, various solutions have been proposed like use of high- $\kappa$  materials to increase the electrostatic control over the channel, employing multi-gate structures to increase drive current for constant drive voltage, adopting high mobility channel materials to improve carrier mobility [18,79,83]. However all of these proposed options possess some other serious challenges like mobility degradation, increment in band-to-band tunneling and gate induced drain leakage and threshold voltage fluctuation due to random dopants. All these factors severely affects reliability, performance, efficiency, yield and cost in CMOS at nanometer regime.

| Device Parameters                | Specific Values                                    |

|----------------------------------|----------------------------------------------------|

| Energy                           | 10 aJ/operation                                    |

| Power                            | $10^7 \mathrm{~W/cm^2}$                            |

| Speed                            | 0.1 ps/op (10 THz, $f_T = 100$ GHz circuit)        |

| Size                             | $L_g = 5 \text{ nm}, \text{Cell} = 100 \text{ nm}$ |

| $I_{DN}$                         | 3 mA/µm                                            |

| Density                          | $10^{10} { m ~cm^{-2}}$                            |

| Cost                             | $10^{-12}$ dollar/gate                             |

| Bit Information Throughput (BIT) | 100 Gbit/ns/cm <sup>2</sup>                        |

TABLE 1.1. Performance Metric for "End-of-the-roadmap" CMOS 2020 [2].

Table 1.1 shows the projected performance metrics for transistor at 10 nm node. Even though some requirements like transistor density and binary information though-put (BIT) can be achieved with multi-gate transistors and high mobility channels, other requirements like clock frequency of 100 GHz, energy requirement of 10 aJ/switching operation and power dissipation of 10<sup>7</sup> W/cm<sup>2</sup> are well beyond the capacity of current CMOS technology. Thus researchers are exploring the possibility of new device material (i.e. beyond silicon) and new device concepts (i.e. beyond CMOS). As an alternative to silicon, various materials like graphene, carbon nanotubes(CNT), memristor, compound semiconductors and free magnetic layers have been the key research in last few years [18, 44, 45, 77, 78, 83]. Similarly, instead of designing devices based on conventional CMOS, researchers are trying to develop both charge based devices like ambipolar MOS devices, tunnel FETs [116], graphene PN junction, CNTFET [11, 121] and non-charge based devices like nano-magnetic logic [94], spin wave [91], spin torque devices [100].

Since the first mechanical exfoliation of graphene, it has been considered as the most promising material beyond CMOS material. Apart from having some unique and excellent properties necessary for future electronics, there are some other advantages of graphene based electronics like: abundant raw materials and thus can produce electronic devices at low cost, no need to go for entirely new fabrication process as they share more or less the same conventional method used in silicon technology. So this dissertation considers graphene as a future replacement for silicon.

#### 1.1. Issues for Nanoscale MOSFETs

The issues for sub nanometer CMOS based electronics are categorized according to their region of problem [64, 77].

(1) Channel:

There are a number of issues in channel for future nanoelectronics like:

(a) Sub-threshold leakage current and threshold voltage variation  $(V_{th})$ :

The sub-threshold leakage current is the diffusion current flowing between source and drain when  $|V_{GS}| < |V_{th}|$  and is given by the relation [64]:

(1)

$$I_{sub-thres} = \mu C_{dep} \left(\frac{W}{L}\right) V_T^2 \left(\exp\left(\frac{V_{GS} - V_{th}}{nV_T}\right)\right) \left(1 - \exp\left(-\frac{V_{DS}}{V_T}\right)\right)$$

where  $\mu$  is the carrier mobility,  $C_{dep}$  is the depletion region capacitance under gate, Wand L are the effective transistor width and length respectively,  $V_{GS}$  is the gate voltage w.r.t source,  $V_{DS}$  is the drain voltage and n is the sub-threshold parameter,  $V_T$  ( $=\frac{KT}{q}$ ) is the thermal voltage. K is Boltzmann constant, T is the operating temperature and q is the electron charge.

In order to keep the dynamic power consumption within a limit, it is necessary to scale down the supply voltage. Similarly, to maintain the drive current capability the threshold voltage also has to be scaled [40]. However with reduction in threshold voltage, the subthreshold leakage current increases exponentially as seen from equ. (1).

The sub-threshold swing (SS), as given by (2) [64], measures how fast the transistor can be turned off with decreasing gate voltage and it is preferred to have this value as small as possible.

(2)

$$SS = \frac{\partial (log_{10}I_{sub-thres})}{\partial V_{GS}}$$

In short channel devices, due to increase in the drain voltage the depletion region advances significantly into the channel. This reduces the threshold voltage and the leakage current become significantly larger. This effect is commonly known as short channel effect (SCE). In order to prevent the depletion region from extending towards source, if higher doping level is used in the substrate then it increases the SS, bandto-band-tunneling and gate-induced drain leakage (GIDL).

Furthermore, at nanoscale MOSFETs, there exist a variation in the channel length among transistors even in the same die. This causes a variation in the  $V_{th}$  among transistors, which in turn affects the device speed and sub-threshold leakage. The transistor with lowest  $V_{th}$  has exponentially high sub-threshold leakage as compared with the transistor having higher  $V_{th}$ . It is therefore very important to maintain sufficient margin for  $V_{th}$  variation so that  $V_{th}$  of any transistor does not become the lowest possible  $V_{th}$ . Similarly, for a high performance logic technology, it is necessary to keep the  $V_{DD} - V_{th}$  within a certain limit in order to maintain the drive current and the performance of the chip. This makes scaling of supply voltage ( $V_{DD}$ ) extremely difficult for future electronics.

(b) Carrier mobility degradation:

The supply voltage has not been able to scale at the rate of device size scaling. This increases the electric field inside the MOSFET. For a low electric field, the drift velocity of the carrier is proportional to the longitudinal electric field across the channel. However at higher electric field, the drift velocity does not increases proportionally. This is known as velocity saturation and is the result of various scattering mechanisms like optical phonon scattering, phonon dispersion, phonon absorption and so on. It increases the transient time for carriers in the channel and also decreases the drain current as predicted by the mobility model.

(c) Hot carrier effects (HCEs):

Due to high electric fields, there are other problems like threshold voltage shifts and transconductance degradation which affect the device reliability. Once the carrier velocity starts saturating, the carrier can attain high kinetic energy. These hot carriers can migrate to unwanted areas like gate dielectric, gate or substrate of a transistor. They can also generate new electron-hole pairs by colliding with the silicon atoms resulting in impact ionization. The impact ionization can significantly increase the substrate current into the gate dielectric. These charges can also get trapped in the gate oxide which causes threshold voltage shift and may turn device unstable or even fail.

(d) Direct source to drain tunneling:

With channel length (or the barrier width) becoming so small in future electronic devices, the electrons can tunnel through the barrier even with a slight increase in the gate voltage. This limits MOSFET to operate as a switch.

(2) Gate:

As the transistor size is decreasing, high-k dielectrics are preferred over conventional  $SiO_2$  in order to increase the gate capacitance and increase the drive current to improve the device performance. The high-k materials allow for equivalent oxide thickness (EOT) scaling. For future electronics, using conventional  $SiO_2$  increases the leakage current due to tunneling effect and thereby increasing power consumption and reducing the reliability. Higher capacitance at the gate enables better control of electrons which speeds up the device as less voltage is needed to charge up the gate. However finding the suitable material is a challenging task. There are certain properties these materials need to possess like:

- (a) Should be crystalline and remain thermodynamically stable even at very high temperature.

- (b) Should have high bandgap and large conduction and valence band offset.

- (c) Should be able to withstand large electric field.

(d) Should have large dielectric constant.

However the proposed high-k materials like  $Al_2O_3$ ,  $HfO_2$ ,  $ZrO_2$ ,  $Y_2O_3$ ,  $TiO_2$  and  $Ta_2O_5$  all have dielectric constant higher than silicon but lower bandgap as well as smaller conduction and valence band offset. This increases the leakage current problem for future electronics. Though the use of polycrystalline silicon as a gate electrode reduces the parasitic capacitance by having a tighter overlap between gate and drain/source region, however it increases the RC time delays and also decreases the driving capability of the transistor.

(3) Drain/source:

The main problem in the drain/source region is due to the parasitic capacitance and resistance. The effect of parasitic resistance during on-current increases as the device gets smaller. In order to suppress short channel effect, shallow source/drain junctions are desired but that in turns increases the sheet resistance as well as band-to-band-tunneling leakage current. Furthermore, with device scaling, the parasitic capacitance increases which limits the performance improvement for future electronics.

(4) Substrate (bulk):

Leakage current like reverse-biased junction leakage current ( $I_{res}$ ) and gate-induced drain leakage current are the main concern for future electronics as the device scales down to nanometer range. Due to reverse biased pn junction, there is a leakage current flowing between the source and substrate, and between drain and substrate. For heavily doped source, drain and substrates, the band-to-band tunneling (BTBT) dominates due to high electric field at nano-scale electronics. This BTBT in turn increases due to shallow source and drain junction in future electronics. Furthermore with high electric field at narrower depletion layer under gate and drain region, a significant amount of surface BTBT current flows from drain to substrate.

1.2. Challenges for Graphene Based Electronics

Though graphene is considered as the most promising candidate to replace silicon in future electronics, it is still in its initial experimental stage. There are few challenges that has to sorted

out before it can be accepted in wide scale for future electronics. Some of these challenges in graphene fabrications are

(1) Substrate selection:

Since carriers are confined in a single layer, the graphene film is highly influenced by the surrounding environment and hence degrades the performance. Though the charge carrier mobility of 100,000 cm<sup>2</sup>/(Vs) is observed for suspended graphene where the substrate is etched way, for graphene with substrate the maximum mobility of 20,000 cm<sup>2</sup>/(Vs) has been demonstrated. Since substrate are necessary for proper heat dissipation, suitable choice of substrate should be wisely selected.

(2) Contact resistance:

Metallization in graphene should be done carefully in order to reduce the contact resistance. All the possible metal combinations like Cr/Au, Ti/Pt and Ti/Pd/Au give contact resistance in the order of  $10^{-4}$  ohm/cm<sup>2</sup> [**90**]. Also since the graphene gets doped by the environment very easily, the metal on graphene can easily dope the underlying graphene. This limits the speed of graphene device by increasing RC time constant.

(3) Gate dielectric deposition:

Finding a suitable gate dielectric material is also very important for graphene processing. This can also possess problem in the speed of the graphene based devices.

(4) Bandgap engineering:

Unlike silicon which has a bandgap of 1.1 eV, graphene is a zero bandgap semi-metal material. This restricts the ON/OFF current to around  $10^{-15}$  and hence limits the application of graphene in digital logic. For graphene to be used in digital logic application, the ratio of ON current to OFF current should be in the range of  $10^4$  to  $10^7$ . Various methods have been proposed to increase this ratio in graphene by creating suitable bandgap in graphene like:

- (a) By using bilayer graphene, few hundred milli-electron volts of bandgap has already been created under the influence of perpendicular electric field [89].

- (b) By quantum confinement (i.e. using graphene nanoribbon (GNR)), it has been pos-

sible to create a bandgap in graphene [**43**]. However the roughness in the edges and width variations significantly affect the electrical properties of GNR [**120**]. Furthermore the fabrication of GNR is also a challenging task at the moment.

(c) By applying different types of strains to a bilayer graphene so as to alter its electronic structure. Some of the strains induced bandgap engineering are by applying perpendicular strain to introduce electron-hole asymmetricity near K-points, applying lateral strain in the case of bilayer graphene to create an indirect bandgap [114].

#### 1.3. Graphene as Material

Since its first discover in 2004, graphene has drawn a lot of attention due to its remarkable properties like super-strong (stronger than diamond) and stiffness, highly transparent, extremely light-weighted, excellent conductor of heat and electricity and some electronic properties that makes them suited for future electronics.

Due to its one atomic thickness, the graphene transistors offer very high packing density and extremely light weight. Also due to its single atom layer, photons can easily penetrate the layer in graphene as compared to other thick materials. This makes graphene highly transparent and is able to transmit about 89-98% of light compared to window glass, which can only transmit around 80-90% light incident on it.

The flat planes of carbon atoms in grahene can very easily bend and stretch (by around 20% of its initial length), without breaking apart the atoms. This gives graphene super-strength and elastic like property. Also the flat hexagonal lattice structure of graphene offers it very little resistance for electron to flow. This in turns allows for quick and easy electron movement across the graphene sheet. Since electrons are responsible for conducting both heat and electricity, low resistance in graphene makes it a better conductor of heat and electricity than copper, silver and diamond.

Electrons travel across graphene sheet with very less noise. This implies that when the electrons travel from one side of the sheet to another (like from source to drain across channel), they travel in a straight line. The carriers in graphene have large value of mean free path even at room temperature, which allows large number of electrons to travel across the sheet. Furthermore,

electrons in graphene travel more like a wave-like particle of light (i.e. phonons) at a speed close to the speed of the light. All these inherent properties in graphene suggest that graphene based devices can operate at small voltage with low heat dissipation.

The carbon atoms in graphene sheet is very closely tied up which can stop other materials like gases, water to get through. This increases the impermeability property in graphene.

#### 1.4. Graphene Based Devices

From the past few years, graphene has been extensively studied both to replace MOS transistor and as a hybrid with conventional MOS transistors. With an aim to enhance future electronics, some of the most popular alternative graphene based technology to conventional CMOS are graphene field effect transistor (GFET), graphene nanoribbon FET (GNRFET), graphene nanoribbon tunnel FET (GNRTFET), graphene based spin FET and bilayer pseudospin FET (BiSFET).

When graphene sheets are rolled at specific and discrete angles (chiral) then a new structure, called carbon nanotube (CNT) is formed. CNTs are also getting lot of attention from both academics and industries due to their extraordinary mechanical, electrical, thermal, optical and chemical properties. However there are more challenges to implement CNT than graphene based FETs.

#### 1.5. Graphene Based Circuits

Some of the unique properties of graphene such as high carrier mobility and saturation velocity, high stability and low noise make graphene a good candidate for high frequency electronic applications. Since the  $I_{on}/I_{off}$  ratio of graphene is very low, its application in digital circuits has been questionable but the results have suggested that using sophisticated technology, these GFETs can also be used for digital circuits. For example, dual-gate and bi-layer GFETs in [122] were measured to have an  $I_{on}/I_{off}$  ratio of 100. These GFETs have been used in all analog, digital as well as RF circuits such as inverters [54, 99, 111], frequency multipliers [97, 117, 119], an RF mixer [118], amplifiers [53, 125], a photo detector [82], and low-noise amplifiers (LNAs) [28, 29]. The concept of wafer scalable analog circuits was verified with an RF mixer example in [72]. Apart from these analogue, digital and RF applications, graphene is also considered crucial in

bioelectronics [**30**, **86**]. Due to its large surface-to-volume ratio, excellent electrical and optical properties, high thermal conductivity, carrier mobility and density, they are extremely useful in biosensors and diagnostics. Recent researches on DNA sensors, gas sensors, PH sensors, strain and pressure sensors, environmental contamination sensors have focused on implementing graphene based nanoelectronic devices.

#### 1.6. Application of Graphene

The success of any new material and device concept depends on how widely it is accepted in different fields. Since silicon has been accepted as a universal fabricating material, its new replacement should also be universal, versatile and should have the ability to change different aspect of life. Graphene, due to its unique properties, has this ability to replace silicon for future electronics and can be used in many different applications from power management including energy storage to hybrid electronics including flexible electronics. Some of the applications of graphene are discussed below:

#### (1) Medicine:

Graphene has been found to be very useful in medical field like tissue engineering, bioimaging and polymerase chain reaction (PCR). Due to its mechanical properties like flexibility and compression ability, it is highly preferred in bone tissue engineering. Due to its non-toxicity at low concentration, they have been used as a drug delivery agent for treating cancerous cells [106]. Due to its high thermal conductivity, it has been used to increase the yield of DNA product in PCR [95].

Similarly, its unique chemical properties (i.e. modifiable chemistry), large optical range (from ultraviolet to near-infrared), electrical properties (i.e. gatable structure and atomic thickness) and electrochemical properties (i.e. ability to transfer electrons between enzyme and electrode surface) makes graphene very much preferable in biosensors. For examples, its high detection sensitivities and its effective fluorescence-quenching ability are preferred in making graphene based DNA detection devices. In [**76**], graphene was successfully fabricated in electronic devices such as microbial detection and diagnosis devices for detection of bacteria, protein, glucose, glutamate, cholesterol, hemoglobin,

DNA and many more. Its ultra-high surface area, excellent carrier mobility and high sensitivities can be explored for electrochemical sensing of glucose, DNA and proteins [73]. Also the graphene has been used as a drug delivery agent [106] and in the detection of diseases by observing the changes in graphene in the presence of certain diseases.

(2) Electronics:

Due to high carrier mobility and low noise, graphene can be used as a suitable channel in field effect transistor. On the application of perpendicular electrical field, graphene can be used as a field effect transistor and can be especially very useful for radiofrequency applications. Further exploiting its high mobility, graphene can be used as detector allowing ultrahigh band frequency selectivity from tera hertz to infra-red range. Graphene can be installed on any materials like plastic or any other substrate and this allows to build flexible and wearable electronic gazeds. Unlike CMOS based electronics which requires both n-type and p-type semiconductors, a single graphene transistors can perform both type of functions. This helps to reduce the device size, power consumption and cost, at the same time improving the device speed. Graphene's high electrical conductivity, mechanical strength and flexibility, and high optical transparency can be used in touch screens, liquid crystal displays (LCDs), organic photo-voltaic cells and organic light emitting diodes (LEDs). Due to its strong interactions with photons, graphene is a promising elements for optoelectronics and nano-photonic devices. By tuning the Fermi level, the optical absorption range of graphene can be changed which in turns gives broad bandwidth for optical modulation. Similarly, it can be used as an infrared detection device due to its response to infrared spectrum producing very little heat, thus minimizing the need of sophisticated cooling mechanisms.

(3) Energy and Storage:

Graphene can also be used in energy related areas like photovoltaic devices as in solar cells, supercapacitors and lithium-ion batteries. The use of graphene in such areas can make these devices very cheap, flexible, lightweight and highly efficient as these are the major issues with present technology in these aspects.

High carrier mobility, optical transparency and excellent electron transport properties of graphene are very advantageous in solar cell. Graphene's high transparency, extremely good conductivity property and an ideal 2D material makes them very suitable to assemble into film electrode in solar cells. Similarly, graphene in conjugated polymers can be used to improve the charge transport properties of the material for photo-voltaic devices. Furthermore, the ability of graphene to generate multiple current driving electrons for each absorbed photon increases the conversion efficiency by compared to the silicon based solar cells. Similarly, its high surface area and ballistic transport properties makes them very suitable to be used catalyst for fuel cells.

Graphene also has the potential to improve the energy storage, charging/discharging life and charging rate in rechargeable lithium ion batteries. This in turn can prolong battery life in electronic devices like cell phone, laptops, cameras and so on and reduces the charging time as well. Similarly, graphene films can be used as a protective layers against corrosion in battery cases.

Due to stable chemical properties, high surface-to-area ratio and high electrical conductivity, graphene is an ideal material for super-capacitor applications. Such supercapacitors can store more energy per unit volume/mass and are particularly useful in applications which requires rapid charge/discharge cycles [21].

(4) Sensors:

Some of the properties like large surface-to-volume ratio, large optical range, high electrical and thermal conductivity, high carrier mobility and density makes graphene as a natural selection for sensor applications. These properties not only makes graphene based sensors to be very fast, smaller, lighter, flexible and transparent but also allows sensors to have high response and recovery time. For example, Bosch's magnetic sensors, based on Hall effect, were found to be 100 times more sensitive than the equivalent silicon based sensors [8]. Furthermore, the small bandgap in graphene makes it very easy to conduct electrons between biomolecules and the electron surface. Similarly, in [19] graphene based wearable sensors were demonstrated in order to monitor human bodily

motion. Sensors for such application needs to be cheap, light weighted, mechanically compatible and should have sensitivity for all types of strains and graphene demonstrates all such properties. Due to its extreme sensitivity, graphene shows change in its electrical conductivity when even a single gas molecule is absorbed on its surface and this property is very useful in gas sensors [55]. As the carrier density in graphene can be very easily modified by applying electric field, this property is very beneficial for electric field sensors [55]. Similarly ambipolar property in graphene can be explored in pH detector. The Dirac point in the GFET moves towards positive direction with the increase in pH value. This can be used to detect pH value exploring the electrical characteristic of GFET [88]. Other type of sensors where graphene are equally applicable are environmental contamination sensors, strain and pressure sensors, humidity sensors, photo-detectors, electric and magnetic field sensors, mechanical sensors and so on .

(5) Environmental Protection and Detection:

High surface area, good absorption capacity, excellent conductivity and optical properties of graphene are very useful for detection, removal and degradation of pollutants in environment. For example, heavy metals like lead, cadmium, chromium, mercury, copper and arsenics are considered to be very harmful for human and environment. Graphene can be employed to remove such heavy metals from soil and water [73]. Graphene and its modified forms can absorb such heavy metal ions and form complexes with metal ions, which can then be recycled. Similarly, graphene can be used to remove radioactive nuclides from water and the graphene based filters have been found to be very effective in desalination by significant margin. Graphene also act as a very good coating in windows to block radio-waves while being transparent to visible light.

(6) Waterproof Coating and coolant:

Graphene can also be used to make either water super-absorbent or super-repellent. This water super-repellent property can be used to make devices waterproof. Similarly, its high thermal conductivity can be used to make graphene as a suitable coolant. For example, copper-graphene or indium-graphene can be better suited to cool down the devices than the pure copper due to their high thermal conductivity. This reduces the cooling devices cost in future electronics as well as increases the reliability of the devices.

#### 1.7. Motivation for this Research

It is expected that by 2026, silicon will reach its fundamental limits and it will not be possible to scale the technology further down. So as an alternative to silicon, in both digital logic circuits and in radio frequency applications, many device concepts like carbon nanotube, graphene, nanowires and so on are continuously been explored by both academics and industries. Recently, carbon nanotubes (CNTs) and graphene has drawn lots of attention due to its extraordinary properties like high carrier mobility, extremely high thermal conductivity, high Fermi velocity, ambipolar property and so on. Though CNTs and graphene shares many similar properties, they have some differences as well. Apart from the fact that CNT is 1D and graphene is 2D structure, it is shown that there is a presence of bandgap in semi-conducting CNT. However the main problem associated with CNT is due to their different chiralities, it is very difficult to have a well defined starting material for CNT based technology. However in graphene, due to their planar geometry, already well established techniques of silicon can be used for graphene technology.

The biggest problem with graphene though is the difficulty to make it. Peeling off a tiny sheet at a time with sticky tape is not really scalable. Though a very thin layer of graphene sheet can be developed by hitting up a sheet of hydrocarbons like methane until the hydrogen get separated and leaving behind the carbon, the quality of graphene will be very low. So, it is difficult to create one atom thick layer and that too with complete purity. For future electronics, both of these requirements need to be met simultaneously. However it does not mean that graphene has no future. The silicon industry faced the same purity problem fifty years back but the problem has been managed eventually with time. So, it is very likely that today's problem for graphene can be easily solved in future with more research and study. Furthermore, when there is a search of a new device concept and technology for future electronics, it is a very right time to focus on the possible implementation of graphene in some of the electronic devices. So this dissertation takes one step towards exploring graphene for future electronics.

#### 1.8. Organization of this Dissertation

The rest of the dissertation is organized as follows.

Chapter 2 reviews some of the peculiar properties of graphene as a material which gives new heights to future electronics. Some of the graphene derivatives device concepts are explored in the same chapter, followed by some of the graphene based circuits that have been studied till far in the literature. Novel contribution of this dissertation is covered at the end of that chapter.

Chapter 3 covers the Verilog-A based modeling and analysis of graphene. The chapter begins with the importance of Verilog-A model for future electronic designs, followed by the device structure of graphene field effect transistor (GFET). Device level modeling of GFET is discussed then. As a case study, cross-coupled version of LC-VCO is considered. Experimental results are given at the end of the chapter.

Chapter 4 covers the non-EDA, i.e. Simscape<sup>®</sup>, based modeling and analysis of graphene circuits. First the importance of Simscape<sup>®</sup> as a simulation tool for new device concept like graphene is discussed, followed by comparison with conventional EDA tools. Simscape<sup>®</sup> based modeling and simulation flow is then discussed. The experimental results obtained from Simscape based GFET model is compared with that obtained from the conventional EDA tools. This is followed by two case study circuits: low noise amplifier (LNA) and cross coupled version of LC oscillator, both modeled in Simscape, are discussed along with the experimental results.

Chapter 5 covers the optimization for Graphene based circuits. The first section highlights the importance of optimization which is then followed by the design flow proposed for the cross coupled version of LC-VCO. As an optimization algorithm, multi swarm optimization (which is an improved version of particle swarm optimization) is discussed. The results of the optimized circuit is then given at the end of the chapter.

Chapter 6 compares the performance of graphene based digital circuit to the silicon transistor based circuit taking static random access memory (SRAM) as a case study. Graphene being a semimetal, it as zero bandgap. This leads to a small ON-OFF current ratio, leading to a very poor performance in terms of power consumption. Thus to meet this key requirement in digital circuits, graphene nanoribbon fied effect transistor (GNRFET) is considered in the chapter. GNRFET have a bandgap and is more suitable to the digital circuit design.

Chapter 7 provides the conclusion and the direction for future research.

#### CHAPTER 2

#### GRAPHENE NANO-ELECTRONICS: AN OVERVIEW

In this 21<sup>st</sup> century, the electronic devices in the form of electronic products such as smart mobile phones, laptops, tablets, and media players have profound effect on the society. Today's world has witnessed an unprecedented and unforeseen changes in the electronic technology. The easiest way of tracking this technological revolution is by measuring the speed, size and cost of the electronic devices. From this perspective, today's electronics devices are "nano" in terms of size and cost; yet very powerful and computationally intensive. Faster, cheaper and smaller electronics are more than a slogan for both electronic driven society and industries. With transistor count already reaching billions in a chip, it is becoming extremely challenging to shrink the transistor further down, particularly at 10 nm and below. Relentless demand for smaller, faster, cheaper and lower power consumption electronic products have forced designers to explore in depth two possible options:

- Combine analogue, digital, mixed-signal, memory, radio frequency (RF) and software components into a single chip, leading to analog mixed signal systems on chip (AMS-SoC) [41,77].

- (2) Search for alternative technologies which can replace silicon to meet future demand.

The former option necessitates a fusion of two design domains, namely analog and digital so that the energy and performance trade-offs can be done [41, 77] while the latter demands alternative material to silicon so as to achieve more flexibility in the design in terms of speed, size.

2.1. Graphene as a Material

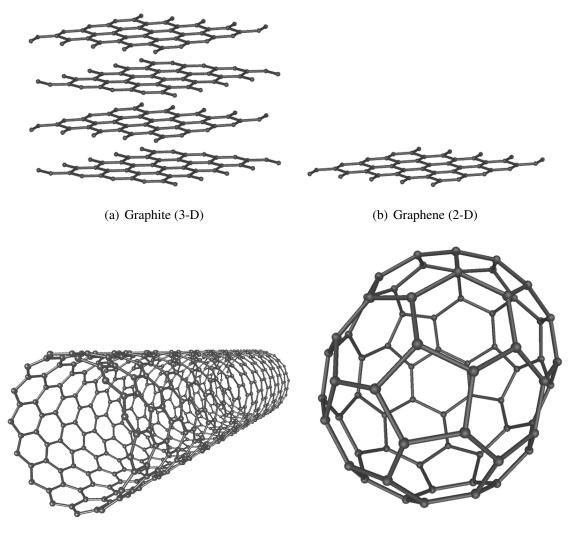

Carbon is a non-metallic elements and the sixth most abundant element in the universe. Some of the most common allotropes of carbon are diamond and graphite (3-D), graphene (2-D), carbon nanotube (1-D) and fullerene (0-D), as shown in Fig. 2.1 [**23**].

Graphite is a crystalline form of carbon in which each atom is only bonded to three other carbon atoms. These atoms form a two-dimensional sheet of hexagons in which each atom has one unpaired electron left over. These electrons fly across the matrix of atoms when an electric current

(c) Carbon nanotube (1-D)

(d) Fullerene (0-D)

FIGURE 2.1. Various allotropes of carbon. [Source: Wikipedia through Wikimedia Commons licence for free to use].

is applied, allowing it to readily conduct electricity. Graphite natural form consists of layers of sheets and if a voltage is applied to it, those free electrons have lot of different directions to go in.

A single layer of graphite is called graphene. Graphene is a repeating hexagonal arrangement of carbon atom. The layer is so thin, just one atom thick, that it is considered as 2-D structure. By taking a single layer of graphite, an electron super highway can be created i.e. a flat matrix of carbon atoms where current can fly across. These sheets of carbon are pretty easy to separate because they are not molecularly bonded to each other. Instead they are held together by Van Der Waals bonds (a kind of weak, electrostatic bond) which makes graphite so soft. A graphene layer of one atomic layer thick can be extracted from a slab of graphite by sticky tape. Because of its extremely good conductive properties, it has a very high probability of replacing silicon in microchips. Not only electrons move faster across graphene but they are also subjected to less noise which implies that the electrons can move from one side of the sheet to the other in a straight line without detouring around the whole lot of atomic potholes.

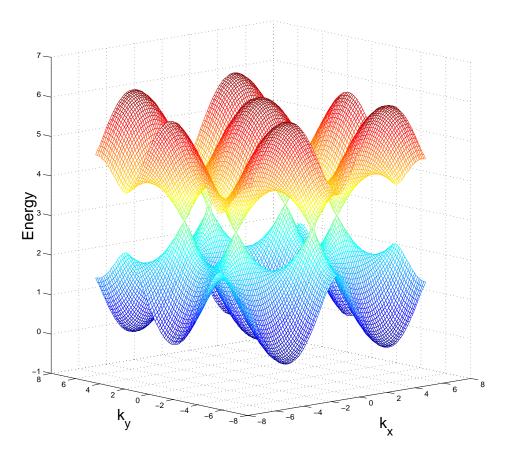

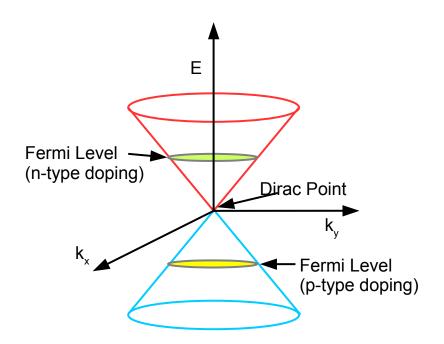

The Fig. (2.2) shows the full band graphene structure [**103**]. The two bands (i.e. valence band and conduction band) in graphene touch each other at 2 points (k and k'). These points are called Dirac points or neutrality points where the effective carrier density is zero and are independent of each other. Since the bands touch at Dirac points, graphene has zero bandgap. As the band structures are symmetric around these Dirac points, the electrons and holes have same properties in pure graphene. The nature of the doping (i.e. either p-type or n-type) and transport carrier (i.e. either electrons are the major carrier or holes are the major carrier) are determined by the position of Fermi level in graphene as shown in Fig. (2.3) [**12**].

At low energies, the bands in graphene have a linear energy dispersion instead of quadratic energy dispersion in semiconductors. This implies that the speed of the electrons is constant and independent of the momentum and the electrons in graphene behave as zero effective mass. Unlike other 2D systems with parabolic dispersion, the density of state (DOS) in graphene increase linearly with the energy and it vanishes at Fermi energy. Therefore, graphene is also termed as zero-gap semiconductor with vanishing DOS at the Fermi energy [92].

The carrier mobility in graphene shows an inverse relation with the carrier density i.e. as the carrier density increases, the mobility decreases. The mobility of carrier also depends on the supporting material and the defects in the graphene itself. In suspended graphene where there is no interaction with the substrate the mobilities as high as around 200,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> has been observed [**90**]. Graphene on insulators like SiO<sub>2</sub> shows much decrease in the mobility and is found to be around 1,000 - 10,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> depending on the nature and purity of the underlying insulator substrate. Epitaxial and chemical vapor deposition (CVD) grown graphene shows the carrier mobility in the order of 1,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [**12**].

FIGURE 2.2. Electronic Dispersion in Graphene. After [103].

The transport of carrier in the graphene channel is controlled by the gate. When the negative gate voltage is applied, the Fermi level raises up and for positively biased gate voltage, the Fermi level falls down. When the gate voltage  $V_g$  is less than  $V_{Dirac}$  then the transport in graphene is due to holes while for  $V_g$  greater than  $V_{Dirac}$ , the transport in graphene is due to electrons. Thus the gate voltage changes with Fermi energy, DOS and the carrier density. However even when the DOS =0 at Dirac energy ( $E_{Dirac}$ ), the graphene is not turned off completely.

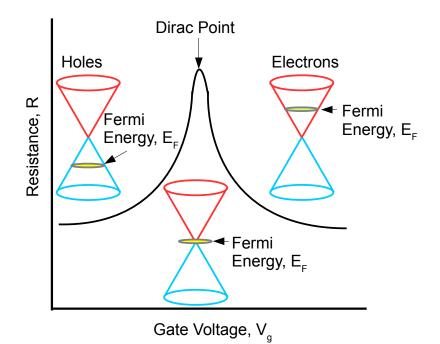

The sheet resistivity of graphene is maximum at the Dirac point and thereafter decays on both sides with change in the gate voltage as shown in the fig. (2.4) [65]. The location of the Dirac point depends on the work function difference between the gate electrode and the graphene, doping and the underlying substrate where the graphene is formed. For the pure graphene, this Dirac point is located near zero gate voltage. Similarly the symmetricity of the curve also depends on the charge impurities and the graphene-electrode contacts. The asymmetric curve leads to different in

FIGURE 2.3. At low energy, bandstructure as two cones touches at the Dirac point, where Fermi level determines the nature of the doping and the transport carrier. After [12].

electrons and holes mobility [103].

Similarly as a channel material, graphene displays self-doping property. This implies that it does not require any impurity to conduct electricity. Self-doping implies the electric field effect and it allows the charge carrier type and concentration to be controlled by external electric field or by the gate voltage. This eliminates the need for doping in graphene and hence eliminates the problem of variation that is introduced during doping.

The ambipolar property in graphene allows graphene transistor to operate with either ptype carrier (i.e. holes) or n-type carrier (i.e. electrons) or both simultaneously. Thus simply by changing the Fermi level, the conduction can shift from electrons to holes.

Some of the properties of graphene that makes them suitable material for future electronics are as follows:

(1) Mechanical Property:

Due to the strong bonds between carbon atoms, it is extremely difficult to break through the sheet of graphene and even the patches of graphene stitched together remains

FIGURE 2.4. Transfer Curve showing graphene resistance as a function of gate voltage. After [65].

very strong. Furthermore, the bonds are very flexible which enables them to be twisted, pulled and curved to a large extend without breaking. These property enable graphene to be used as wearable devices. Graphene shows extraordinary stiffness. For a few layer of graphene with thickness less than 8 nm, a spring constant of 1-5 N/m and a Youngs modulus of 0.5 TPa was observed in [**93**]. For a monolayer graphene, the second and third order elastic stiffness was found to be 340 and 690 N/m respectively, with a breaking strength of 42 N/m. This corresponds to the Youngs modulus of 1.0 TPa and the intrinsic strength of 130 GPa. These figures suggest that the suspended graphene can support significant extra load like copper nano-particles and can protect the device from accidental shock and mishandling.

(2) Electronic Property:

All few layers of graphene (like mono layer, bilayer and tri-layer) are good conductors [115]. Beyond three layers of graphene, the properties resembles the graphite. However upon applied by perpendicular electric field, these few layers of graphene show different nature of electronic band structure [102]. For example, in monolayer graphene the gate

(a) Strength

(e) Wearable

FIGURE 2.5. Future Electronic due to graphene

voltage modulates the current but it cannot be switched off due to the absence of bandgap. In the case of bilayer graphene, the bandgap can be created by an application of external perpendicular electric field and it is the only gate tunable graphene semiconductor. In the case of trilayer graphene, with the application of external gate , the conduction band and the valence band overlap each other thereby acting as a semi-metal [102].

Furthermore, by using the dual gate configuration, it is possible to independently tune the electronic bandgap and carrier doping concentration in graphene. A monolayer graphene is a zero bandgap semiconductor which shows the linear band structure around the Fermi energy. The bilayer graphene is a semi-metal like material which shows parabolic band structure around the Fermi energy and a band overlap of 0.16 meV, while the graphite also shows semi-metal like behavior but with a band overlap of 41 meV [**115**].

(3) Optical Property:

In [85], it has been shown that the opacity of suspended graphene depends only on the fine structure constant,  $\alpha = e^2/(hc) = 1/137$ , which describes the coupling between the light and relativistic electrons. It has been shown that the light opacity values for monolayer and bilayer graphene is around 2.3% and 4.6% respectively in the visible light range of 450 nm -750 nm [115]. With increase in the number of layers, up to five layers, the opacity value increase linearly. This very low opacity value for graphene is due to the relativistic massless Dirac Fermion behavior of electrons and holes in graphene.

(4) Thermal Property:

In [13], the thermal conductivity of suspended monolayer graphene near room temperature was recorded to be 5300 W/(mk) with a mean free path of 750 nm for phonon. With the increase in the number of layers, the value decreases down. This observed value is higher than the CNT ( $\sim$  3000 W/(mk) for multi-walled CNTs and  $\sim$  3500 W/(mk) for single walled CNTs) and diamond ( $\sim$  1000 - 2200 W/(mk)) [115]. This high value of thermal conductivity of graphene can make it extremely good material in thermal management and also allows graphene to integrate with Silicon CMOS technology. For future electronics devices where size will play very crucial role, it allows the necessity of so-phisticated cooling mechanism and enhance the device life span.

- (5) Other exciting properties of graphene are as follows:

- (a) Excellent carrier mobility,

- (b) High carrier saturation velocity,

- (c) High Fermi velocity,

- (d) High current density,

- (e) Extremely thin due to one atomic thick,

- (f) Highly stable and less noisy,

- (g) High carrier mean free path (about 400 nm @ room temperature)

- 2.2. Graphene Based Devices

There are many possible alternative transistors that can be designed using graphene for future electronics. All of these novel concepts have drawn attention due to their individual advantages and at this time it is very difficult to predict which one will win the race.

(1) Graphene Spin FET:

Spintronics is the study of intrinsic spin of the electrons. The magnetic moment of the electrons can be used to represent, compute and transmit information in more efficient way than the electron charge [84]. The electronic circuits build on spintronic concepts are advantageous due to their higher storage capacity, higher processing power and lower heat dissipation as compared to those circuits build on classical electronics concepts. For example, by adding more states for logic bits, it is possible to increase the storage capacities and processing power in computers and other data processing applications. Similarly, the new compounds (like graphene) used in such devices enable electrons to flow without energy loss which in turn reduces heat dissipation.

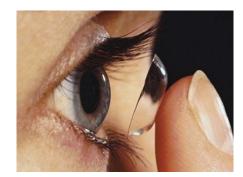

The structure of spinFET as proposed by [**31**] is similar to metal oxide semiconductor field effect transistor (MOSFET) with a major difference of source and drain being ferromagnetic metals. The magnetization in these metals are aligned parallel to each other. The spin-polarized carriers are injected from the source and are collected at the drain side. When traveling from source to the drain side, these carriers precess due to Rashba Effect and reach the drain side with different polarization state. The polarization angle ( $\phi$ ) of the carriers with respect to drain depends on the number of factors like length of the channel, rate of the precession and transverse electric field in the channel, which can be controlled by the gate voltage. Due to this difference in polarization angle of the carriers with respect to the drain, there is a difference in the net current, which can be modulated by the gate voltage.

As shown in the Fig. (2.6-a), when  $V_g$  is greater than zero, then the precession of the electrons is controlled by the electric field which makes it possible to reach the drain side with the same polarization hence the net current is increased. When  $V_g$  is made zero, as shown in the Fig. (2.6-b), then the electrons injected into the channel start precessing and then they reach the drain side its orientation is different to that at the drain side thereby decreasing the net current. Thus gate acts as a switch to control the flow of current in the channel just like in conventional MOSFET. In spintronics, the spins are manipulated by both magnetic and electrical fields.

However, the spin-based devices need to satisfy some parameters like the follow [84]:

- (a) A need for proper spin carrier injection and detection mechanism in order to have low read and write current,

- (b) A need of proper spin modulation mechanism, and

- (c) A need for very high spin transit time (or de-coherence time) so that the spin polarized electron can travel a long distance without any loss in encoded information. Graphene is an attractive material for spin based electronics due to the following rea-

sons:

- (a) Large spin coherence length,

- (b) Zero nuclear spin,

- (c) Reduced spin scattering, and

- (d) Better spin tunnel junction contacts thus providing a path for high spin polarization injection

Since it is difficult to modulate spin information in graphene due to weak spin orbit interaction, it is still possible to enable spin modulation through spin-splitting of bands and gate modulation [84]. In graphene based spin FET, graphene (either single layer or multi-layer) is used as a channel between two ferromagnetic contact.

(2) Bilayer pseudo spin field effect transistor (BiSFET):

(b) Spin Precessing when  $V_g = 0$

FIGURE 2.6. Graphene based SpinFET. After [3].

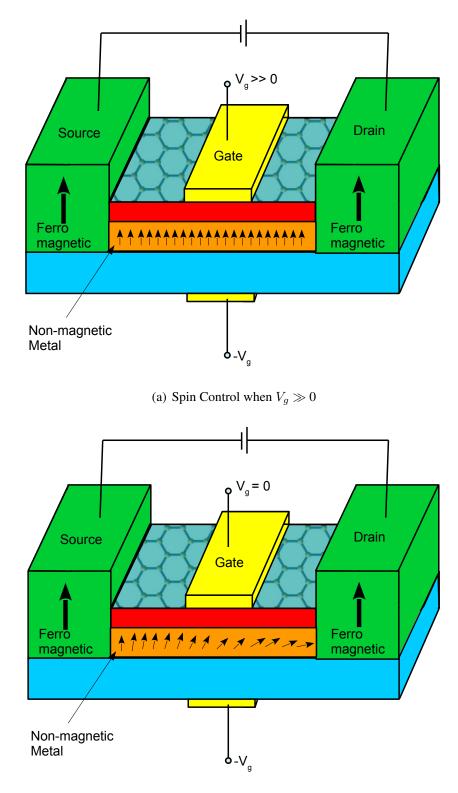

Bilayer pseudo spin field effect transsitor (BiSFET) has the potential to be ultra-low power replacement of metal oxide semiconductor field effect transistor (MOSFET) [14]. The switching energy per device with BiSFET can be on the scale of 10 zJ (i.e.  $10^{-21}$  J), which is two order of magnitude below CMOS transistors [98].

FIGURE 2.7. Bilayer pseudo spin field effect transsitor (BiSFET) Structure. After [98].

As shown in the fig. (2.7), BiSFET consists of two layers of graphene, one n-type and another p-type, which are separated by a thin insulating dielectric. The device concept is based on the possibility of super-fluid condensation of excitons (i.e. bounded electronhole) in two graphene layers above room temperature and thus enhancing the interlayer tunneling [98]. Under certain condition, electrons from one layer can form a pair with holes from opposite layer and this will create a bounded electronhole pair, known as excitons. When these excitons condensate, they effectively shorts the two layers, which in turns reduces the tunnel resistance [15]. There is a debate whether or not such superfluid condensation can exist at the room temperature. However if it exists then it can take future electronics to a new height.

Such interlayer superfluid condensation has been seen in high magnetic field at low

temperature for group III-V elements systems but it is suggested that in graphene such condition can exist even at the room temperature, due to its properties like [98]:

- (a) Due to one atomic layer thickness, graphene can be placed very close to maximize interlayer Coulomb interaction.

- (b) Symmetric electron-hole band structure over energy range of interest,

- (c) Zero bandgap such that all interlayer electrostatic potential difference can induce electron hole pair,

- (d) Low density of states which gives high Fermi energy at Dirac points for relatively low carrier density.

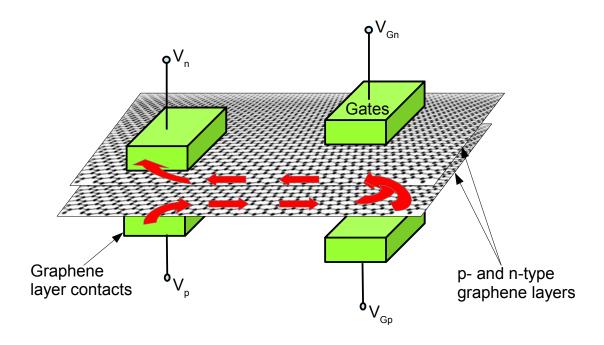

The gate voltages  $V_{Gn}$  and  $V_{Gp}$  are used to create super-fluid between gates and allow imbalance of charge distribution to weaken the superfluidity. The interlayer voltages  $V_n$  and  $V_p$  are used to control the tunneling conductance, which becomes large at small interlayer bias  $(V_n - V_p)$  and vice versa [15].

(3) Graphene Nanoribbon Field Effect Transistor (GNRFET):

Graphene based circuits can achieve lower energy-delay product (EDP) as compared to silicon based CMOS which results them to be used as low power future electronics as these transistors work with  $V_{DD} = 0.5$  V as compared to 0.7 V or 0.9 V in Si CMOS. Since 2-D graphene is a zero-band gap material, it makes them excellent conductor rather than semiconductor. To open bandgap and make them behave as a semiconductor, so as to use in digital logic application, 2-D graphene structure can be converted into 1-D narrow strips of graphene ribbons known as graphene nanoribbons (GNRs) [25]. Since the bandgap in GNR is inversely proportional to the nanoribbon width, for nanoribbon width less than 2 nm, GNR shows excellent semiconductor properties and GNRFET shows high  $I_{on}/I_{off}$ ratio and low subthreshold swing [38]. However, the performance of these novel devices is greatly affected by the variation of the ribbon width, edge roughness of the ribbon and missing atoms in the edges. The width of the ribbon is generally defined as the number of dimer lines as shown in the Fig. (2.8).

Due to ballistic transport in GNRFET as compared to drift-diffusion transport in Si,

FIGURE 2.8. Graphene width defined in terms of dimer

the mean free path is much larger in GNRFET than in Si. In GNRFET, the current flow through a narrow ribbon as compared to large surface area. This, on one hand, reduces the load capacitance in GNRFET which thereby reduces the dynamic power and in the other hand due to ballistic transport more current are injected through GNRFET. Based on the edge geometry, GNRs are classified into mainly two types: armchair-GNR and zigzag-GNR. Armchair GNRs are predominantly semiconducting whereas zigzag GNR demonstrate metallic properties [24]. However bandgap can be created in zigzag with either rough edge or by passivating the edges with hydrogen atoms. There are mainly two types of GNRFETs: Metal-Oxide Semiconductor-(MOS-)type GNRFETs (MOS-GNRFETs) and Schottky-Barrier-type GNRFETs (SB-GNRFETs).

(a) Metal-Oxide Semiconductor-(MOS-)type GNRFETs (MOS-GNRFETs) [24]

As shown in the fig. (2.9-a), MOS-type GNRFET is constructed with metal gate, GNR based drain, source and channel. In MOS-type GNRFET, reservoirs (source and drain) are the portions of GNR not covered by the gate and are heavily doped GNRs. By choosing the type of dopants in these reservoirs, the MOS-type GNRFETs are either made n-type or p-type. Since either n-i-n or p-i-p doping profile can be

FIGURE 2.9. GNRFET and its types

formed, the current conduction is mostly based on thermionic conduction. In order to connect source and drain to the outside world, metal layers are needed which and they are connected with these graphene layers (drain and source) by vias. This introduces graphene-metal junction and significantly increases contact resistance. This severely limits the circuit performance. Due to monotonic I-V curve, it gives higher  $I_{on}/I_{off}$  ratio than SB-GNRFET. Thus they are more preferred in digital logic applications and low power applications. However the contact resistance limits their performance. Further, its performance is limited by the process variation that occurs inside the reservoir while doping. However these reserviors in MOS-GNRFET observes the minority carriers during the off conduction state and hence results in very small  $I_{off}$  current.

(b) Schottky-Barrier-type GNRFETs (SB-GNRFETs) [25,47]

As shown in the fig. (2.9-b), in SB-type GNRFET, gate, drain and source are metal and the channel is constructed with graphene nanoribbon passing between drain and source under gate. Since SB-GNRFETs exhibit ambipolar I-V curve, they are neither n-type nor p-type. It is possible to design logic circuits using such ambipolar characteristics. In order to implement CMOS based logic circuits using SB-GNRFET, the corresponding I-V curve need to be shifted accordingly as as to make them either p-type or n-type [**25**]. The current conduction in SB-GNRFET is based on Schottky barrier tunneling due to metal-graphene junction. Since drain and source are made of metal, hence this structure does not introduce any contact resistance.

The ambipolar characteristic of SB-GNRFET makes it difficult to completely turn off even at zero gate voltage. Thus the leakage current increase and thereby increases the power consumption. However due to its low EDP and low delay, it is mostly suitable for high performance and, high energy efficient application where power consumption is not an issue. It has higher  $I_{off}$  due to the absence of doped reservoir to observe minority carrier as in MOS-GNRFET.

(4) Graphene Nanoribbon Tunnel Field Effect Transistor (GNRTFET):

The subthreshold swing (SS), which is the voltage required to change the current, in Si CMOS is limited by thermionic emission to 60 mv/dec. This results in the increase of static power dissipation when Si CMOS is scaled down. Thus in order to obtain SS less than 60 mv/dec, graphene has been preferred due to its symmetric band structure, light effective mass and direct band gap which assist tunneling phenomenon. Graphene nanoribbon tunneling field effect transistor (GNRTFET) is another graphene based transistor which has drawn attention from past few years due to its low subthreshold swing, high  $I_{on}/I_{off}$  ratio and these contribute high speed, low dynamic power, low off-state power dissipation, superior gate control and a reduction of traversal energy component in 1-D tunneling transport [127]. To enhance the IN-state tunneling it is preferred to use a narrow bandgap materials with smaller effective masses.

FIGURE 2.10. Double gate GNRTFET. After [124].

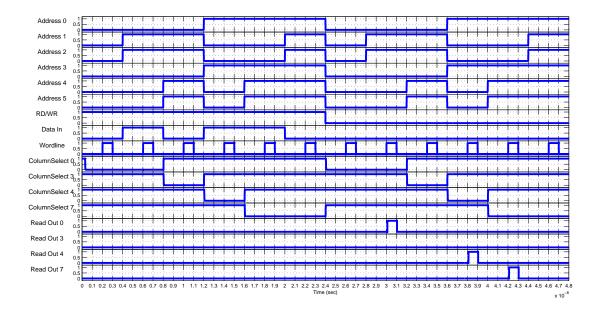

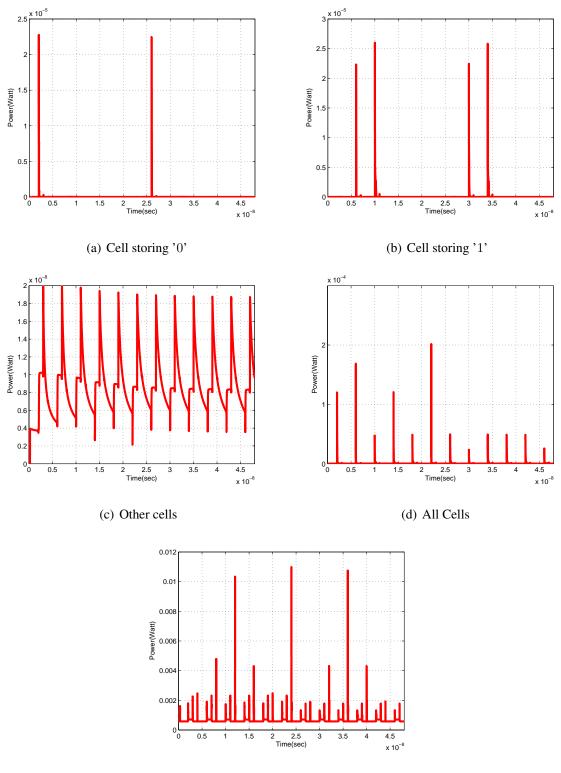

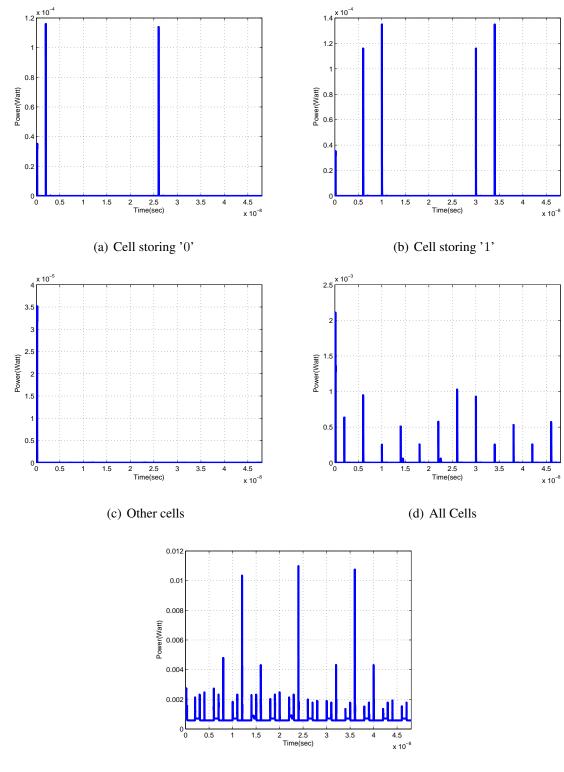

As shown in the fig. (2.10), the graphene nanoribbon based TFET consists of p-type GNR source, n-type GNR drain with intrinsic GNR as a channel.  $HfO_2$  is used as a gate insulator whose dielectric constant is 16. Since the source is p-type and drain is n-type, the thermionic current is negligible in GNRTFET. The current flow is due to band to band tunneling phenomenon which is more sensitive to terminal bias than thermionic current and thus leads to a very low SS like 0.19 mV/dec [**127**]. When the gate voltage is zero and the drain voltage is applied, the conduction band in the channel becomes