# Hardware Demonstration of High-Speed Networks for Satellite Applications

Jonathon W. Donaldson and David S. Lee

Prepared by Sandia National Laboratories Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy's National Nuclear Security Administration under Contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831

| Telephone:       | (865) 576-8401             |

|------------------|----------------------------|

| Facsimile:       | (865) 576-5728             |

| E-Mail:          | reports@adonis.osti.gov    |

| Online ordering: | http://www.osti.gov/bridge |

Available to the public from U.S. Department of Commerce National Technical Information Service 5285 Port Royal Rd. Springfield, VA 22161

| Telephone:    | (800) 553-6847                                             |

|---------------|------------------------------------------------------------|

| Facsimile:    | (703) 605-6900                                             |

| E-Mail:       | orders@ntis.fedworld.gov                                   |

| Online order: | http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online |

SAND2008-5874 Unlimited Release Printed September 2008

# Hardware Demonstration of High-Speed Networks for Satellite Applications

Version 1.02 Last update: September 1, 2008

Jonathon W. Donaldson and David S. Lee Wireless and Event Sensing Applications, 2664 Sandia National Laboratories P.O. Box 5800 Albuquerque, New Mexico 87185-0986

### ABSTRACT

This report documents the implementation results of a hardware demonstration utilizing the Serial RapidIO<sup>™</sup> and SpaceWire protocols that was funded by Sandia National Laboratories' (SNL's) Laboratory Directed Research and Development (LDRD) office. This demonstration was one of the activities in the Modeling and Design of High-Speed Networks for Satellite Applications LDRD. This effort has demonstrated the transport of application layer packets across both RapidIO and SpaceWire networks to a common downlink destination using small topologies comprised of commercial-off-the-shelf and custom devices. The RapidFET and NEX-SRIO debug and verification tools were instrumental in the successful implementation of the RapidIO hardware demonstration. The SpaceWire hardware demonstration successfully demonstrated the transfer and routing of application data packets between multiple nodes and also was able reprogram remote nodes using configuration bitfiles transmitted over the network, a key feature proposed in node-based architectures (NBAs). Although a much larger network (at least 18 to 27 nodes) would be required to fully verify the design for use in a real-world application, this demonstration has shown that both RapidIO and SpaceWire are capable of routing application packets across a network to a common downlink node, illustrating their potential use in real-world NBAs.

### TABLE OF CONTENTS

| EXECU   | UTIVE SUMMARY                                                           | 11 |

|---------|-------------------------------------------------------------------------|----|

| 1. INTI | RODUCTION                                                               | 13 |

| 2. HAR  | RDWARE DEMONSTRATION OVERVIEW                                           | 15 |

| 2.1     | Demonstration Components                                                |    |

| 2.2     | Hardware Implementation                                                 |    |

| 2.3     | Additional Topics: Remote Reconfiguration                               |    |

|         | -                                                                       |    |

| -       | dIO DEMONSTRATION                                                       |    |

| 3.1     | RapidIO Test Network Topology                                           |    |

|         | 3.1.1 Node Types                                                        |    |

| 2.2     | 3.1.2 Traffic Flow Overview                                             |    |

| 3.2     | Source Node Design                                                      |    |

|         | 3.2.1 User Interface                                                    |    |

|         | 3.2.2 Software API                                                      |    |

|         | 3.2.3 Hardware Interface                                                |    |

|         | 3.2.4 CCSDS Packet Encapsulation Pipeline                               |    |

|         | 3.2.5 Maintenance Frame Generation Pipeline                             |    |

|         | 3.2.6 Transaction ID Block RAM (tid_bram.v)                             |    |

|         | 3.2.7 Scratch-Pad Memory Module (target_user.v)                         |    |

|         | 3.2.8 Initiator Response Handler (iresp_handler.vhd)                    |    |

|         | 3.2.9 RapidIO Design Environment (rio_wrapper.v)                        |    |

| 3.3     | Destination Node Design                                                 |    |

|         | 3.3.1 RapidIO Dword Breaker Module (srio_dwrd_brkr.vhd)                 |    |

|         | 3.3.2 CCSDS Downlink Framer Flow Controller (ccsds_dlf_flow_ctrl.vhd)   |    |

|         | 3.3.3 CCSDS Downlink Framer Module                                      |    |

| 3.4     | CCSDS Over SRIO Self-Verifying Test Bench                               |    |

|         | 3.4.1 Test Bench Top-Level (cos_to_clink_tb.v)                          |    |

|         | 3.4.2 Test Bench Task Functions                                         |    |

|         | 3.4.3 Signal Monitors and Signal Spys (signal_ <mons spys="">.v)</mons> | 46 |

| 3.5     | Image Generation Module                                                 | 46 |

|         | 3.5.1 Theory of Operation                                               | 46 |

|         | 3.5.2 Fetching the Original Image Data (bmpParse.c, Gen_LCD_Image.java) |    |

|         | 3.5.3 Image Generation Hardware (image_gen_bram.vhd)                    | 47 |

| 3.6     | Debug and Analysis with RapidFET <sup>™</sup>                           |    |

| 3.7     | Debug and Analysis with the NEX-SRIO                                    | 49 |

| 3.8     | Debug and Analysis Setup with STx SRDP                                  |    |

| 3.9     | Future Work with RapidIO                                                |    |

| 4 SPA   | CEWIRE DEMONSTRATION                                                    | 57 |

| 4.1     | SpaceWire IP and Hardware Selection                                     |    |

| 4.1     | SpaceWire Implementation                                                |    |

| 4.2     | Remote Configuration over SpaceWire                                     |    |

|         |                                                                         |    |

|         | RDWARE DEMONSTRATION CONCLUSIONS                                        |    |

| 6. REF  | ERENCES                                                                 | 71 |

### LIST OF FIGURES

| Figure 1. Basic block diagram of hardware demonstration.                              | 15 |

|---------------------------------------------------------------------------------------|----|

| Figure 2. Detailed block diagram of hardware demonstration.                           | 17 |

| Figure 3. Progression of image data as each color source node is added to the network | 18 |

| Figure 4. Test network topology                                                       | 19 |

| Figure 5. Block diagram of source node design.                                        |    |

| Figure 6. Textual user interface.                                                     |    |

| Figure 7. Example software-level debug output.                                        |    |

| Figure 8. Software/hardware architecture.                                             | 27 |

| Figure 9. Software layers                                                             |    |

| Figure 10. Block diagram of Serial RapidIO Core design                                | 34 |

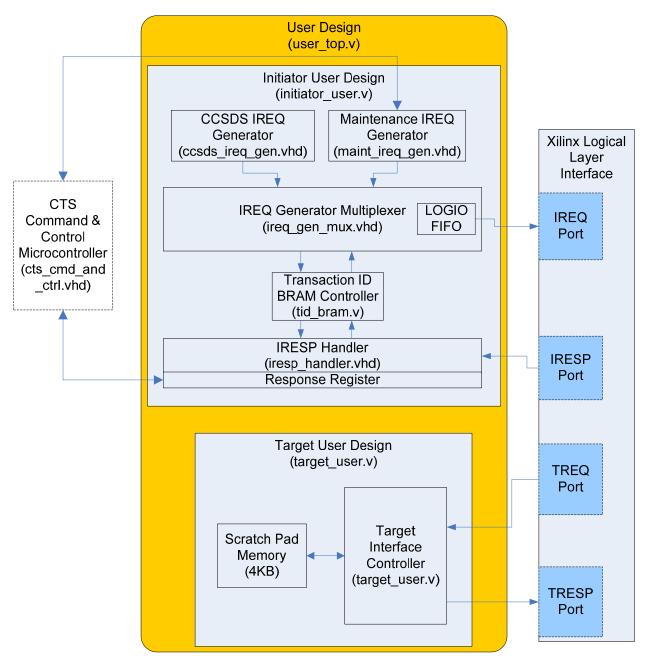

| Figure 11. User design internal components                                            | 35 |

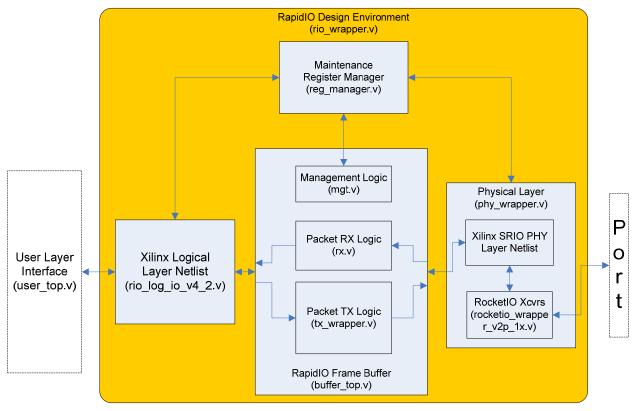

| Figure 12. RapidIO Design Environment.                                                | 39 |

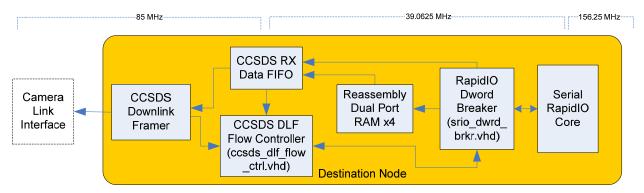

| Figure 13. Destination node architecture.                                             |    |

| Figure 14. Example flow for incoming RapidIO frames.                                  | 40 |

| Figure 15. Statistics output from GEN_CCSDS_SEQ_STAT function.                        | 45 |

| Figure 16. Statistics output from GEN_MAINT_SEQ_STAT function.                        | 46 |

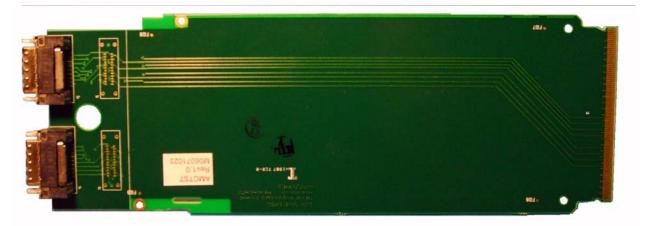

| Figure 17. CX4-AMC Adapter Card                                                       |    |

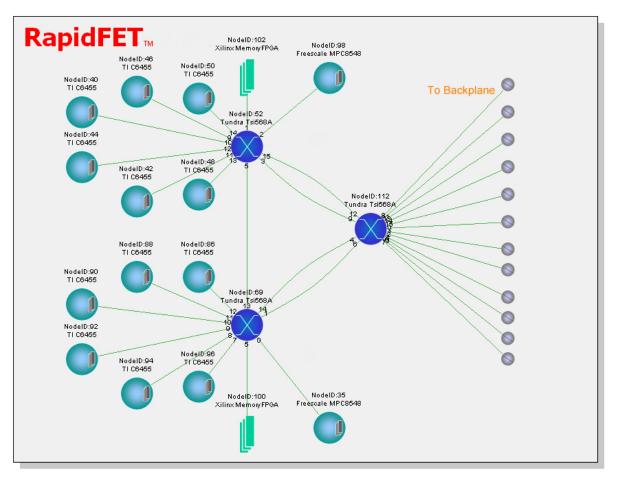

| Figure 18. RapidFET Professional and Probe in large RapidIO network                   | 49 |

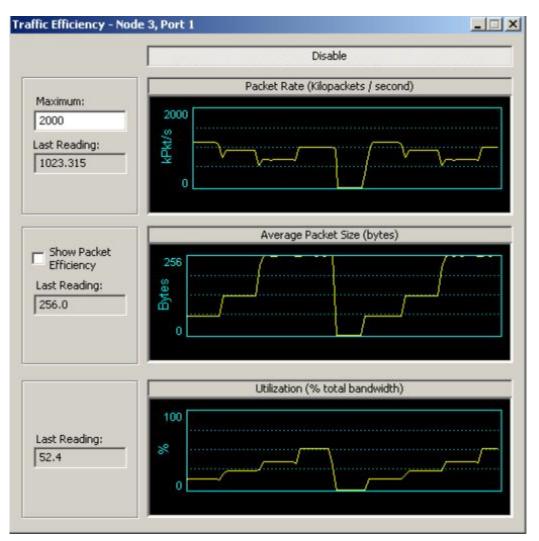

| Figure 19. RapidFET Utilization Graphs                                                | 50 |

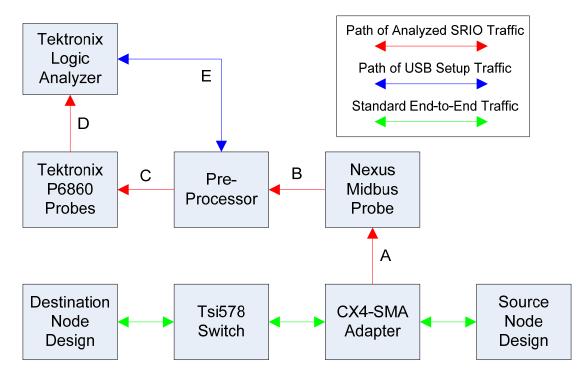

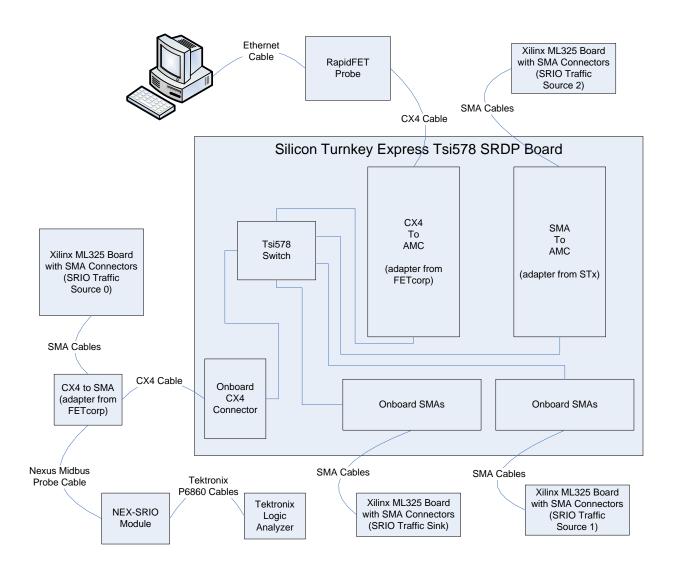

| Figure 20. Nexus SRIO Protocol Analyzer connection topology                           | 51 |

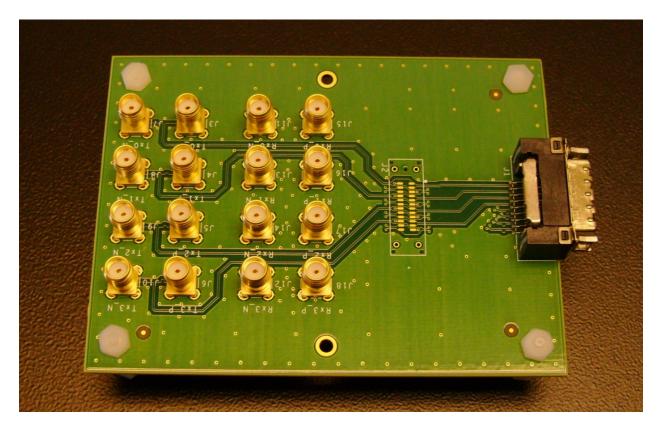

| Figure 21. CX4-SMA adapter board                                                      | 51 |

| Figure 22. NEX-SRIO packet disassembly software                                       |    |

| Figure 23. Debug and analysis system setup.                                           | 53 |

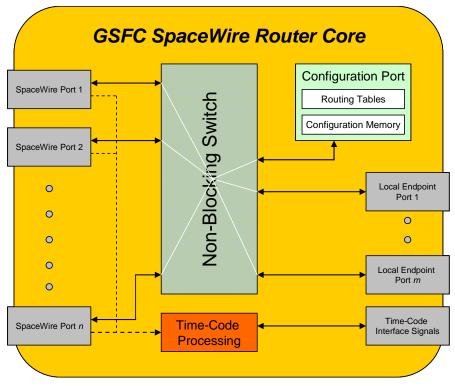

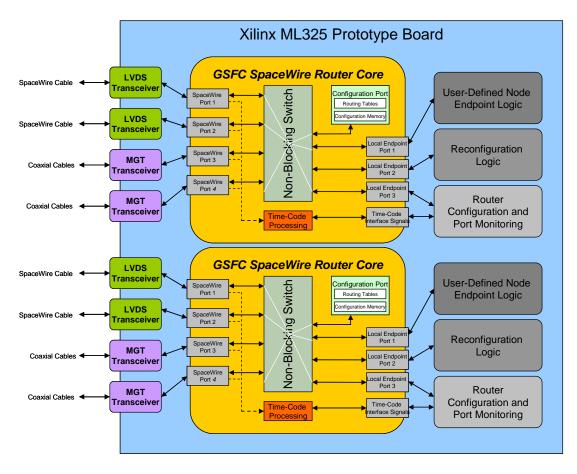

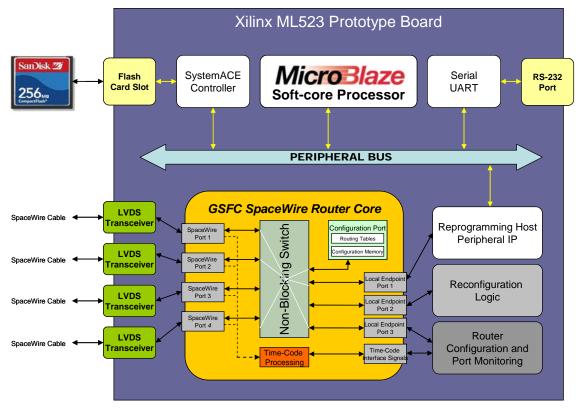

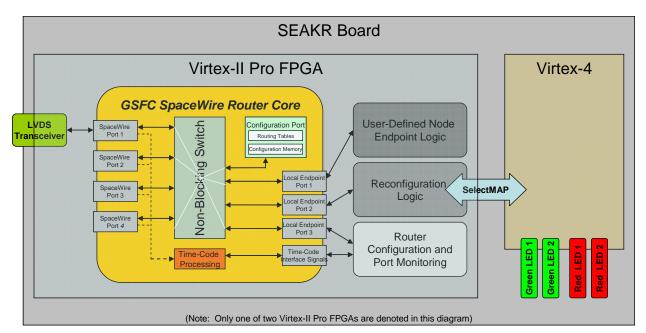

| Figure 24. GSFC SpaceWire router IP core block diagram                                | 59 |

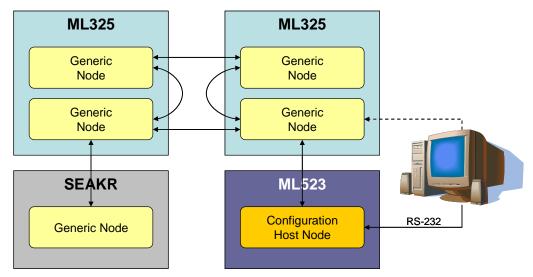

| Figure 25. Two independent node instantiations on one ML325 board.                    | 61 |

| Figure 26. SpaceWire hardware demonstration layout                                    | 64 |

| Figure 27. Configuration host (ML523) block diagram.                                  | 66 |

| Figure 28. Configuration target (SEAKR) block diagram.                                |    |

| Figure 29. System block diagram for reconfiguration demonstration.                    | 67 |

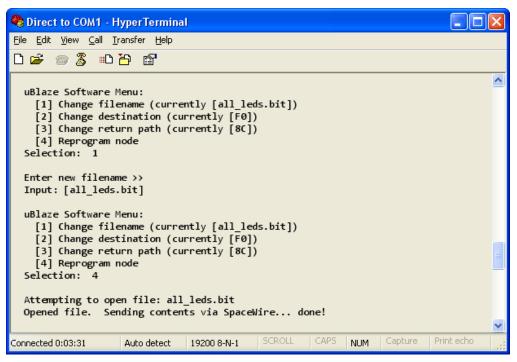

| Figure 30. Remote configuration over SpaceWire control interface.                     | 68 |

### LIST OF TABLES

| Table 1. Device Utilization Statistics for Serial RapidIO Source Node Design      |    |

|-----------------------------------------------------------------------------------|----|

| on Virtex-II Pro 70.                                                              |    |

| Table 2. Device Utilization Statistics for Serial RapidIO Destination Node Design |    |

| on Virtex-II Pro 70. <sup>3</sup>                                                 |    |

| Table 3. Device Utilization Estimates for Serial RapidIO Source Node Design       |    |

| on Virtex-5 FX130T.                                                               | 22 |

| Table 4. Device Utilization Estimates for Serial RapidIO Destination Node Design  |    |

| on Virtex-5 FX130T. <sup>4</sup>                                                  | 22 |

| Table 5. Serial RapidIO 4x/1x Latency Numbers Under No Congestion                 |    |

| Table 6. Device Utilization Statistics for SpaceWire Single Node Sensor Interface |    |

| (source node) Design on Virtex-II Pro 70                                          |    |

| Table 7. Device Utilization Statistics for SpaceWire Single Node Downlink         |    |

| (destination node) Design on Virtex-II Pro 70.                                    | 63 |

| Table 8. Device Utilization Statistics for SpaceWire Single Node Design           |    |

| on Virtex-5 LX110T.                                                               |    |

| Table 9. Device Utilization Statistics for SpaceWire Single Node Design           |    |

| on Virtex-5 FX130T.                                                               | 65 |

|                                                                                   |    |

### ACRONYMS

| API   | Application Programming Interface             |

|-------|-----------------------------------------------|

| BRAM  | Block RAM                                     |

| BMP   | bitmap                                        |

| CAR   | Capability Register                           |

| CCC   | Command and Control                           |

| CCSDS | Consultative Committee for Space Data Systems |

| CF    | CompactFlash                                  |

| COE   | coefficient                                   |

| COTS  | commercial off-the-shelf                      |

| CRC   | cyclic redundancy check                       |

| CRF   | Critical Request Flow                         |

| CSR   | Command and Status Register                   |

| CTS   | CCSDS to SRIO                                 |

| CTSS  | CCSDS to SRIO Solution                        |

| DAR   | Device Access Routine                         |

| DCM   | Digital Clock Manager                         |

| DLF   | Downlink Framer                               |

| EDK   | Embedded Development Kit                      |

| FF    | Flip-Flop                                     |

| FIFO  | first in, first out                           |

| FPA   | Focal Plane Array                             |

| FPGA  | Field Programmable Gate Array                 |

| GSFC  | Goddard Space Flight Center                   |

| GCLK  | global clocking                               |

| HAL   | Hardware Abstraction Layer                    |

| HDL   | Hardware Description Language                 |

| IP    | Intellectual Property                         |

| IRESP | Initiator Response                            |

| IREQ  | Initiator Request                             |

| ISA   | Instruction Set Architecture                  |

| ISF   | internal switching fabric                     |

| ISO   | International Standards Organization          |

| LDRD  | Laboratory Directed Research and Development  |

| LFSR  | linear feedback shift reporter                |

| LUT   | Lookup Table                                  |

| LVDS  | low-voltage differential signaling            |

| MGT                                      | multi-gigabit transceiver                                                                                                                                  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NBA                                      | Node-Based Architecture                                                                                                                                    |

| OPB                                      | On-chip Peripheral Bus                                                                                                                                     |

| PCB<br>PCI<br>PLB<br>PPC                 | printed circuit board<br>peripheral component interconnect<br>Processor Local Bus<br>PowerPC                                                               |

| QoS                                      | Quality of Service                                                                                                                                         |

| RAM<br>RCO<br>RCD<br>RCPM<br>ROM<br>RREG | random access memory<br>Receive Command Opcode<br>Receive Command Data<br>Route Configuration and Port Monitoring<br>read-only memory<br>response register |

| SAR<br>SNL<br>SRIO                       | Segmentation and Reassembly<br>Sandia National Laboratories<br>Serial RapidIO                                                                              |

| TID<br>TREQ<br>TUI                       | Transaction ID<br>Target Request<br>Textual User Interface                                                                                                 |

| UART                                     | Universal Asynchronous Receiver/Transmitter                                                                                                                |

# EXECUTIVE SUMMARY

This report documents the implementation results of a hardware demonstration utilizing the Serial RapidIO<sup>™</sup> and SpaceWire protocols that was funded by Sandia National Laboratories' (SNL's) Laboratory Directed Research and Development (LDRD) office. This demonstration was one of the activities in the Modeling and Design of High-Speed Networks for Satellite Applications LDRD [1].

The purpose of the research and development presented in this document was to demonstrate transport of application-layer packets across a network to a common downlink destination. In this demonstration the RapidIO and SpaceWire protocols were used as a conveyance for Consultative Committee for Space Data Systems (CCSDS) packets across a small network topology. The Serial RapidIO<sup>™</sup> and SpaceWire protocols were chosen as possible candidates for network communications in node-based architectures (NBAs) for satellite systems in the Survey of Communication Protocols for Satellite Payloads [2]. The CCSDS protocol was chosen because SNL has a working history with the protocol, there was a previously written Hardware Description Language-based packet generator to leverage from, and it is a likely candidate for the application protocol used in future satellite architectures.

RapidIO is a commercial protocol that follows the standard Open Systems Interconnect networking model. The specification for RapidIO defines strict implementation directives for components spanning from the *physical* layer to the *transport* layer. A standard Application Programming Interface and function definitions are also provided for *application* layer designs interfacing to RapidIO hardware. RapidIO was chosen because its protocol specification allows for network scalability, guaranteed delivery, and ultra-high bandwidth. RapidIO is available in both serial and parallel physical layer implementations. The serial version of the physical RapidIO connectivity specification was chosen for this study because it requires the fewest connecting wires between nodes, consumes less power, allows for higher data rates, and results in less clock skew than its parallel counterpart.

SpaceWire is a bi-directional, full-duplex serial protocol developed primarily by the European Space Agency. SpaceWire is currently in use in a number of flight systems to provide a high-speed data infrastructure between sensors, processing elements, memory units, telemetry subsystems, and other space instruments [3]. As SpaceWire is already utilized in many space projects today, its feasibility for flight systems has already been established, making it a promising candidate for integration into networks for NBAs.

To adequately model real-world scenarios, the hardware demonstration assembled a representative model of real flight hardware using commercial-off-the-shelf development hardware. In typical flight systems, sensors would act as data generators and downlink modules as data sinks. The custom designs created for the hardware demonstration include a traffic generator node and a traffic sink node. The traffic generator nodes are responsible for encapsulating CCSDS packets in RapidIO frames or SpaceWire packets before transmitting them across the network. The traffic sink design consumes the RapidIO-encapsulated or SpaceWire CCSDS packets and reconstructs them for transfer to a CCSDS downlink framer. Integrating

these elements into the demonstration platform resulted in a successful demonstration of communication between nodes in a multi-node routed network.

One key desire in an NBA is the ability to dynamically reprogram endpoint logic in flight to provide different node functions within the network. This provides a number of advantages, including a failover capability to mitigate in-flight failures by reprogramming spare nodes to replace failed functionality. This node-based hardware demonstration was expanded to demonstrate the capability of reading a configuration bitfile from flash, transmit the bitfile over the network, and successfully reprogram remote nodes.

Although a much larger network (at least 18 to 27 nodes) would be required to fully verify the design for use in a real-world application, this demonstration has shown that both RapidIO and SpaceWire are capable of routing application packets across a network to a common downlink node, illustrating their potential use in real-world NBAs.

# 1. INTRODUCTION

The purpose of this study was to create a hardware design that demonstrated the ability to transfer application-layer packets from multiple source nodes across both RapidIO and SpaceWire network infrastructure to a common downlink destination node. The test network used in the demonstration was designed to use a small number of nodes based on commercial-off-the-shelf (COTS) development hardware as a proof-of-concept for a larger network topology.

From previous studies performed for this Laboratory Directed Research and Development (LDRD) [2], both Serial RapidIO<sup>™</sup> and SpaceWire protocols emerged as potential candidates for use in NBAs. Since both protocols performed well in software simulation [4], the next step was to implement both Serial RapidIO and SpaceWire into hardware. To achieve this goal, a hardware demonstration built a representative model of the data flow that would be present in a real-world flight system. An additional goal of this demonstration was to characterize and validate the assessments performed in [2] of key protocol features. These observations and results are discussed throughout this document and cover features that include but are not limited to:

- Supported Bandwidths

- Overhead

- Latency

- Quality of Service (QoS)

- Fault Detection

- Reliability

- Error Correction

- Scalability

# 2. HARDWARE DEMONSTRATION OVERVIEW

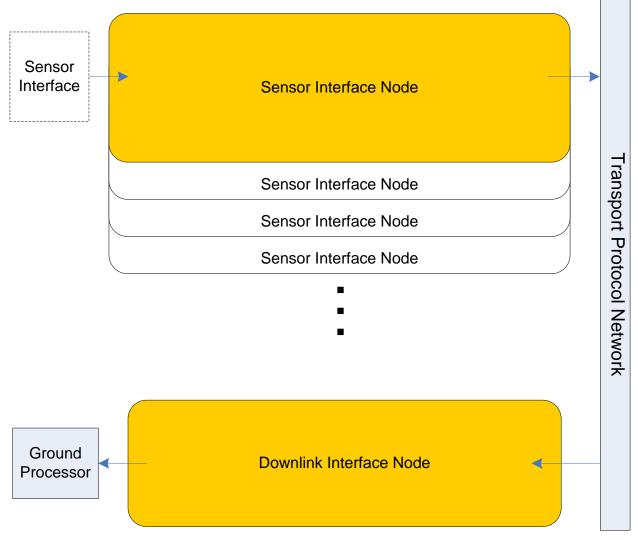

Data flow in current architectures typically begins at sensor interface hardware. This hardware is responsible for collection of data from attached sensors that may generate large amounts of data. This data is shipped to data processor hardware, which may provide some level of in-flight data pre-processing and reduction. Finally, the processed data is sent to downlink channels for transmission to ground systems. Figure 1 portrays a high-level diagram of this concept.

To properly demonstrate the concept of a NBA, the components mentioned above were subdivided into distinct functions and separated into different node types. The approach to this demonstration was to provide enough hardware and development resources to demonstrate many functions of a real-world model.

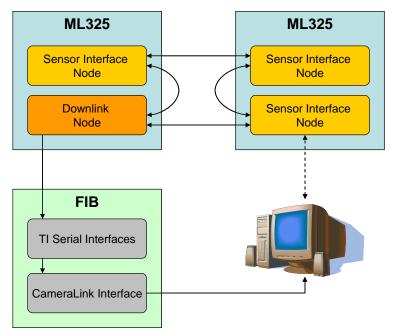

Figure 1. Basic block diagram of hardware demonstration.

### 2.1 Demonstration Components

The representative components in this hardware demonstration include a sensor interface node, a downlink or spacecraft communication node, a spacecraft interface, and a ground station. The sensor interface node is responsible for the generation of application data packets and transmits these data packets to the downlink node. The downlink node packages the data packets from all sensor node sources into frames and transmits these frames to the ground station, which can then analyze, display, or post-process the data.

Next, these representative flight component functions were mapped onto available COTS hardware. Where possible, COTS software or readily available Intellectual Property (IP) cores were used in place of any custom development efforts.

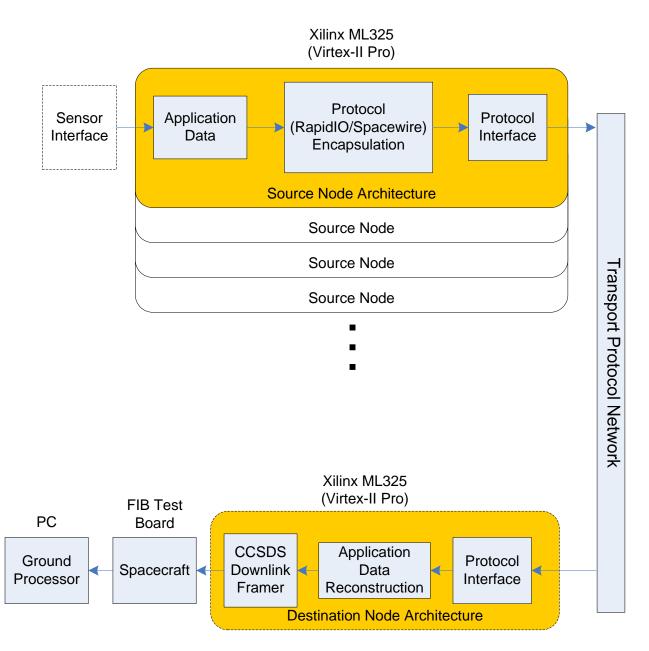

Development of sensor interface nodes includes three primary components. An application data component provides the source data to act as incoming sensor data. A data encapsulation component then packages the data into Consultative Committee for Space Data Systems (CCSDS) packets. The protocol interface component utilizes the appropriate network protocol (Serial RapidIO or SpaceWire) to transmit the information onto the network. The hardware utilized for these node types was typically a Xilinx ML325 prototype board [5].

The downlink node is also comprised of three components, also typically implemented on a Xilinx ML325 prototype board. The network protocol component receives network packets from the network. Data reconstruction strips off any network protocol specific information to isolate the source CCSDS packet. The downlink framer component takes these CCSDS packets and injects them into fixed-length CCSDS frames. These frames are then sent to the ground station. The CCSDS framer is a necessary component to communicate properly with the ground station, providing frame synchronization information and encapsulated packet information.

The final piece of the hardware demonstration is the ground station, which is provided by a PC equipped with a commercially available PCI-X CameraLink interface card. In order to get very high-speed data transfer (5.44 Gbps) of CCSDS frames into the PC, a custom interface board (hereafter referred to as the "FIB" test board) was leveraged from another SNL program. This FIB test board, developed by Ray Byrne and Joe Lyle at SNL, is able to receive four high-speed serial channels. The data received from these channels is bonded together to form one logical high-speed data channel. The FIB test board takes the logically bonded channel data and outputs this data via CameraLink. It should be noted that CameraLink requires a fixed-length data field and that can be accommodated by CCSDS frames fixed in size at 2044 bytes, whereas CCSDS packets in this demonstration were variable length. The entire architecture flow is shown in Figure 2.

Figure 2. Detailed block diagram of hardware demonstration.

### 2.2 Hardware Implementation

The hardware demonstration incorporated a total of four nodes: three sensor interface nodes and one downlink node, which was connected to the ground station.

To introduce a visual component to the hardware implementation, a color image was taken and divided into its three constituent colors (red, green, and blue). Each sensor node was configured with one of the colors to serve as its sensor or "application data." The goal was to have each sensor node transmit its color component information through the downlink node to the ground station, where the image can be reassembled into a full-color image. If one of the nodes should

fail or if data transfer is interrupted for any reason, part or all of one color component will be missing and the image will be visually distorted. See Figure 3 for an example.

Figure 3. Progression of image data as each color source node is added to the network.

### 2.3 Additional Topics: Remote Reconfiguration

In addition to the demonstration of data exchange between nodes, another goal is to illustrate some of the other advanced features of NBAs. The ability to reprogram endpoint logic in flight to perform different node functions provides a number of advantages. Most notably, the ability to reprogram spare nodes with the functionality of failed nodes provides a failover mechanism that dramatically increases the reliability of the system. Thus, another objective of this hardware implementation is to demonstrate the ability to program nodes over the network.

# 3. RapidIO DEMONSTRATION

The discussion of the RapidIO demonstration begins with an overview of the test topology and is then broken down into two main sections: the source node design and the destination node design. The source nodes are responsible for generating the application layer packets while the destination node consumes them. The following sections provide a detailed overview of each component, both COTS and custom, which was utilized to implement the final solution. In addition, some useful design verification and debug tools are discussed that will aid in creating larger and more complex demonstrations in the future.

### 3.1 RapidIO Test Network Topology

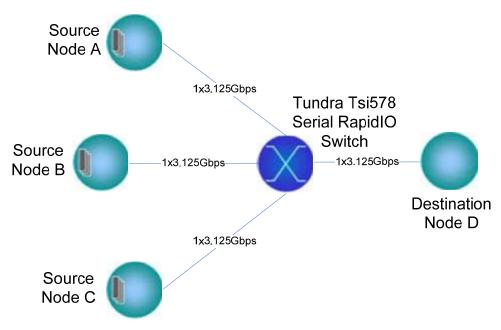

The test network setup is shown in Figure 4. The system consists of four RapidIO endpoints connected via SMA cables to a centralized Tundra Tsi578 RapidIO switch. This topology was chosen not only because it simplifies the testing and debug process, but also because the flexibility of the RapidIO protocol allowed for verification of most traffic scenarios with a single switch. This flexibility is very advantageous because it allows for the development of a RapidIO system without requiring the development of switching IP that would be integrated into each individual node. In this case, the single switch was implemented using a COTS development board.

Figure 4. Test network topology.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> The current revision of our design supports up to four source nodes; however, only three are shown here to simplify the diagram.

Unlike the SpaceWire demonstration (discussed in Section 4), there is presently no commercially available RapidIO switch IP that can be integrated into each source/destination node without developing a custom printed circuit board. Therefore, this demonstration was limited to the use of a fixed-Application-Specific Integrated Circuit switch development board that contained a Tsi578 Serial RapidIO switch from Tundra Semiconductor. This demonstrates a centralized switching topology rather than a distributed switching topology as discussed in Section 4. In order to scale a centralized switch topology, any Tsi578 switch can be directly attached to the port of another Tsi578 switch in order to increase the port count. The switches can be chained together indefinitely so long as the final endpoint node count does not exceed the RapidIO maximum network size set forth by the "Transport Type" field of each interacting node. The *transport type* field identifies whether a given endpoint supports either 8-bit or 16-bit device IDs.

The three nodes on the left are traffic sources and the node on the right is a traffic sink. Each node is attached to a different switch port using a 1x3.125 Gbps link. Factoring in the required 8B/10B data encoding used by RapidIO, this link speed allows for a theoretical maximum throughput of 2.5 Gbps. The RapidIO Version 1.3 physical layer specification allows links up to 4x3.125 Gbps for a total maximum throughput of 10 Gbps. It is also worth noting that the RapidIO switch will automatically detect the link rate (i.e., 1x/4x) of any node that is attached to it and synchronize the physical layers without any manual user intervention.

The Xilinx physical layer IP core does support the maximum allowable link rate; however, the purpose of this study was not to test the bandwidth capabilities of RapidIO. Therefore, a 1x link was chosen to simplify the design, reduce Field Programmable Gate Array (FPGA) resource usage, reduce implementation time, and reduce the number of physical cables needed in the system.

Though the RapidIO protocol does not specify a standard connection interface, the two cable types used in this system were CX4 (Infiniband) and coaxial with SMA connectors. Maximum cable lengths depend on the devices themselves and the data rate. Some devices have preemphasis on transmitters and equalization on receivers that extend their transmission lengths well beyond RapidIO specs of 22-inch backplanes. Moreover, the slower the data rate the longer the cable allowed. Certain vendors have demonstrated 4x 3.125 Gbps throughput across 10 meters of CX4 cable; however, typical applications implement CX4 lengths up to one meter and SMA coax lengths up to 28 inches.

### 3.1.1 Node Types

Each of the endpoints (A, B, C, D) utilize version 4.4 of the Xilinx Serial RapidIO Physical Layer Interface Core (part number: DO-DI-RIO-PHY) and the Xilinx RapidIO Logical and Transport Layer Interface core (part number: DO-DI-RIO-LOG)<sup>2</sup>. These two Xilinx cores are currently compliant with Version 1.3 of the official RapidIO specification.

The Xilinx RapidIO IP cores themselves are merely used as a conduit to interface and communicate with the physical Serial RapidIO network and by no means constitute the entire design on any of the endpoints, which would consist of application-specific activities. The

<sup>&</sup>lt;sup>2</sup> At the time of this writing, neither of the Xilinx RapidIO IP cores is RIOLAB [6] certified.

remaining design will be discussed in later sections. The source and destination nodes were developed on a Xilinx ML325 development board fitted with a Virtex-II Pro XC2VP70.

At present, a single source endpoint (including the operating system and software interface) consumes approximately 15% of the V2Pro's internal logic resources, 20% of internal BlockRAM (BRAM),<sup>3</sup> and one of the two internal PowerPC 405 cores. The hard PowerPC core in the Xilinx was used in this design; however, a soft-core processor is another option. A processor is the preferred method of initializing and executing the mandatory RapidIO Application Programming Interface (API) functions discussed in Section 3.2.2 when the board is powered on. The processor is also used for the custom user interface discussed in Section 3.2.1.

The destination node consumes only 11% of the FPGA's logic resources and only 14% of the Block RAM space. The device utilization summaries from the Xilinx Place and Route tool are shown in Tables 1 and 2 for the source and destination nodes, respectively.

| Digital Clock Managers | 2 out of 8         | 25% |

|------------------------|--------------------|-----|

| Gigabit Transceivers   | 1 out of 20        | 5%  |

| PPC405s                | 1 out of 2         | 50% |

| Block RAMs             | 67 out of 328      | 20% |

| Flip-Flops             | 9426 out of 66176  | 14% |

| 4-input LUTs           | 11132 out of 66176 | 16% |

Table 1. Device Utilization Statistics for Serial RapidIOSource Node Design on Virtex-II Pro 70.4

| Table 2. Device Utilization Statistics for Serial RapidIO |

|-----------------------------------------------------------|

| Destination Node Design on Virtex-II Pro 70.4             |

| Digital Clock Managers | 1 out of 8        | 12% |

|------------------------|-------------------|-----|

| Gigabit Transceivers   | 5 out of 20       | 25% |

| Block RAMs             | 48 out of 328     | 14% |

| Flip-Flops             | 7128 out of 66176 | 10% |

| 4-input LUTs           | 8472 out of 66176 | 12% |

<sup>&</sup>lt;sup>3</sup> RAM – random access memory.

<sup>&</sup>lt;sup>4</sup> These statistics reference the node implemented with the optional target scratch-pad memory (see Section 3.2.7).

Since the target device in the current processing architecture development is a Xilinx Virtex-5 FX130T, we can speculate as to the resource usage on a Virtex-5 FX130T for both the source and destination nodes from the Virtex-II Pro utilization reports. These estimations are shown in Tables 3 and 4, respectively. Furthermore, if the Xilinx physical layer Serial RapidIO (SRIO) core were re-generated to use 4x RapidIO links (instead of the present 1x configuration) it would consume approximately 4% more Lookup Tables (LUTs) and Flip-Flops (FFs) on either the V2Pro or the Virtex-5 architectures. A 4x configuration would also require an additional three sets of gigabit transceiver ports.

| DCMs                 | 2 out of 12        | 16% |

|----------------------|--------------------|-----|

| Gigabit Transceivers | 1 out of 20        | 5%  |

| PPC405s              | 1 out of 2         | 50% |

| Block RAMs           | 67 out of 596      | 11% |

| Flip-Flops           | 9426 out of 81920  | 12% |

| 6-input LUTs         | 11132 out of 81920 | 13% |

Table 3. Device Utilization Estimates for Serial RapidIO Source Node Design on Virtex-5 FX130T.<sup>5</sup>

| Table 4. Device Utilization Estimates for Serial RapidIO |

|----------------------------------------------------------|

| Destination Node Design on Virtex-5 FX130T. <sup>5</sup> |

| DCMs                 | 1 out of 12       | 8%  |

|----------------------|-------------------|-----|

| Gigabit Transceivers | 5 out of 20       | 25% |

| Block RAMs           | 48 out of 596     | 14% |

| Flip-Flops           | 7128 out of 81920 | 9%  |

| 6-input LUTs         | 8472 out of 81920 | 10% |

The Tundra Tsi578 Serial RapidIO switch is built on to a development board from Silicon Turnkey Express [7]. The switch can be configured for a total of sixteen 1x link rate ports or eight 4x link rate ports. The board provides SMA, Infiniband, AMC, and various other High Speed Serial Interface (HSSI) connections for attaching to the Tundra switch ports. The switch development board requires a 20-pin ATX power supply; however, the board itself is not ATX form factor, which means that the board and power supply cannot be mounted inside a standard ATX chassis.

#### 3.1.2 Traffic Flow Overview

Disregarding minor RapidIO handshaking frames, we can view nodes A, B, and C as the primary traffic sources and node D as the traffic sink. The three source nodes generate CCSDS packets

<sup>&</sup>lt;sup>5</sup> These device utilizations are only estimates and are based solely upon the additional hardware resources available as per the Virtex-5 FX130T datasheet.

and RapidIO maintenance request/response frames when requested to do so by the user. While RapidIO maintenance transactions may occur between any two nodes, CCSDS packets are only sent to node D.

The RapidIO maintenance frames are needed to configure the endpoint and switch nodes subsequent to power on. Moreover, if any real-time changes need to be made to the switch's LUTs, or any interrupt/error status flags within any of the nodes need to be cleared, maintenance frames will be required. The power-on configuration steps include setting the endpoint/switch device IDs, setting the endpoint host lock ID, determining endpoint/switch state-of-health, configuring the switch LUTs, and initializing the switch's physical layer ports.

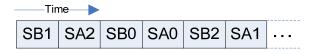

The CCSDS packets are first encapsulated into SRIO frames using the Message class (FType 11) before being dispatched from the source node. The Message class was chosen because it utilizes sequence ID numbers for each RapidIO frame sent. This allows RapidIO frames to be received in any order on the destination node while still allowing the full CCSDS packet to be properly reconstructed. This process is referred to as Segmentation and Reassembly (SAR).

The Message class also allows response frames to be sent back to the originating source node, thus creating an application-layer packet flow control mechanism. Aside from the built-in flow control of the RapidIO protocol, an additional CCSDS packet handshaking function was implemented that allows no more than one CCSDS packet to be in transit between all source/destination pairs at any time (see Section 3.3.1 for more information).

Each CCSDS packet is variable length with a maximum of 8188 bytes and constitutes one or more RapidIO frames. Each RapidIO frame has a maximum payload size of 256 bytes. Moreover, each RapidIO Message class frame requires an additional 8 bytes of protocol overhead. These 8 bytes consist of information specific to the physical, logical, and transport layers of the frame, which includes a 16-bit cyclic redundancy check (CRC) for error checking purposes (see Reference 8 for more information regarding these fields). This additional information results in a  $\sim$ 3% overhead for every CCSDS packet sent.<sup>6</sup>

In addition to overhead, packet transmission is also susceptible to the inherent latency within the switch. Tundra defines latency "as the time interval between the first bit of the Start-of-Packet arriving at the ingress of the Tsi578 and that same bit leaving the device" [9]. The cross-switch latency for each possible serial RapidIO link-rate is shown in Table 5.

<sup>&</sup>lt;sup>6</sup> Note that this overhead calculation does not account for the necessary application-layer handshaking mechanism between the source/destination pair.

| Reference Clock | Ingress and Egress<br>Port Width | Ingress and Egress<br>Baud Rate | Minimum Latency (ns) <sup>a</sup> |

|-----------------|----------------------------------|---------------------------------|-----------------------------------|

| 156.25MHz       | 4x mode                          | 3.125                           | 112                               |

|                 |                                  | 2.5                             | 128.8                             |

|                 |                                  | 1.25                            | 212.8                             |

|                 | 1x mode                          | 3.125                           | 137.6                             |

|                 |                                  | 2.5                             | 160.8                             |

|                 |                                  | 1.25                            | 276.8                             |

Table 5. Serial RapidIO 4x/1x Latency Numbers Under No Congestion (courtesy of [9]).

a. Due to the asynchronous ability of the clock frequencies within the device, the latency numbers can vary as much by two clock periods of 3.2ns.

Upon receipt of a CCSDS packet, the destination node will forward the packet on to the CCSDS Downlink Framer (DLF) module. The DLF encapsulates one or more CCSDS packets into a CCSDS Frame, which can store 2024 bytes worth of CCSDS packets. The final CCSDS frame data is then reformatted and sent off-chip to another board, which transfers the data over a CameraLink interface to a desktop computer. The frame data and statistics can then be viewed by the user via custom software.

The Tsi578's internal switching fabric (ISF) is non-blocking to all traffic provided the total ingress data flow to any single egress port does not exceed the egress port's outbound bandwidth. Clearly, in the topology shown in Figure 4, there is a bottleneck for traffic approaching the destination node D if any more than one of the source nodes is enabled and the sum of their traffic exceeds 2.5 Gbps. If this occurs, the switch will send "Packet Retry" control symbols back to the physical layer core of the source nodes. Any source node that receives one of these symbols will continue to retransmit the packet from its physical layer output packet buffer until the switch replies with a "Packet Accepted" control symbol.

Note that the Tsi578 also has full support for RapidIO priority-based quality of service (QoS) frame scheduling; however, all RapidIO frames sent by the source and destination nodes in the current version of this demonstration have their priority field set to zero. This was done only to simplify the design and debug process. Please see Section 3.9 for more information on this topic.

In part, this study was used to test RapidIO's "guaranteed delivery" mechanism to ensure that all packets sent across the network would reliably reach the intended destination. The only way to truly test this capability was to design a bottleneck into the network that would cause the switch to block packets. Not only does the bottleneck exercise the RapidIO protocol itself, but it also

aids in verifying proper switch and endpoint functionality when subjected to high levels of switch port congestion.

### 3.2 Source Node Design

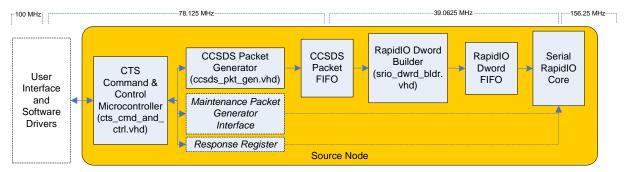

The source node consists of both software and hardware components with the responsibility of encapsulating CCSDS packets in the RapidIO frame format for subsequent transmission across the switched RapidIO network. The following section discusses each component within the design, along with its specific purpose, in a top-down hierarchical fashion. A high-level block diagram of the source node design is shown in Figure 5. Also shown in this figure are the different clock domains that were required to execute this demonstration.

Figure 5. Block diagram of source node design.

### 3.2.1 User Interface

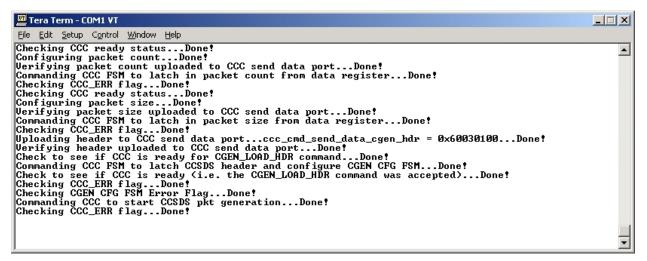

At the highest level of the design the user can interface to the Serial RapidIO hardware through a menu-driven textual user interface (TUI) over an RS-232 serial port. Presently, the menu options allow the user to send any number or size of CCSDS packets to the DLF node, read/write maintenance registers on any node, monitor switch state of health (e.g., congestion and interrupt registers), or populate the switch LUTs for the fixed topology described above. An example of the TUI is shown in Figure 6.

This small operating system is written in ANSI C and boots from internal Block RAM memory within the FPGA on power-up. The boot sequence is executed by the PowerPC, which initializes the hardware and creates a software-based instance of the device in main memory. The instance itself is a structure that contains information regarding the state of the hardware (e.g., base memory address, state of health, library initialization flags, etc.). After the boot sequence has completed, the RapidIO API library is then ready for input from the user.

Various debug options and output verbosity level parameters are also available. This debug information is very useful in diagnosing issues at the software/hardware layer interface. An example of this debug output is shown in Figure 7.

| 💹 Tera Term - COM1 ¥T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <u>File Edit Setup Control Window Help</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| <pre>What do you want to do?<br/>1 - Send continuous packets of maximum size.<br/>2 - Send continuous packets of minimum size.<br/>3 - Send continuous packets with each packet of random size.<br/>4 - Send (Inf-1) packets of maximum size.<br/>5 - Send (Inf-1) packets of minimum size.<br/>6 - Send (Inf-1) packets with each packet of random size.<br/>7 - Send packets of incrementing size from 1 to C_CGEN_UTIL_MAX_USR_WRDS<br/>8 - Send a custom packet sequence.<br/>9 - Send previous sequence again.<br/>10 - Run self test.<br/>11 - Run Demo Topology Setup.<br/>12 - Check switch congestion and interrupt registers.<br/>13 - Send a custom maintenance packet.<br/>14 - Send image.<br/>15 - Exit Menu.<br/>Choice:</pre> |  |

Figure 6. Textual user interface.

Figure 7. Example software-level debug output.

Each of the source nodes may contain up to two endpoints inside the single Virtex-II Pro FPGA on the ML325 development board. If two endpoints exist they are both physically and logically separate from one another – no "inter-node" communication is performed. The sole limitation when running two endpoints simultaneously on the ML325 board is that there is only a single Universal Asynchronous Receiver/Transmitter (UART) interface. To work around this problem, a UART multiplexer module was written that switches between the two endpoint STDIN/STDOUT interfaces depending on the state of an on-board Dual In-line Package switch.

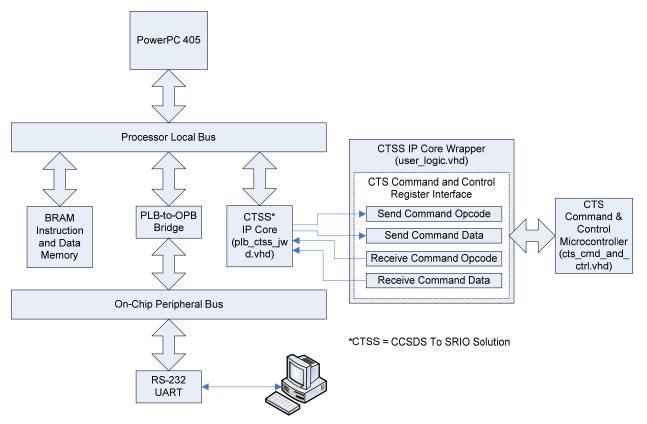

An overview of the architecture used to interconnect the software and hardware components of a single endpoint is shown in Figure 8. All communications to and from the PowerPC are performed via the Processor Local Bus (PLB). The instruction and data memory are stored in the same Block RAM space with a single bus attachment because the PPC405 only has a five-stage pipeline and does not support out-of-order execution. The UART module is significantly slower than any other component in the system; therefore it is attached to the low-speed On-Chip Peripheral Bus (OPB) in order to simplify bus arbitration and reduce the number of wait states.

The CCSDS to SRIO Solution (CTSS) IP core that was designed for this study is directly attached to the high-speed PLB. This core, which includes all software and hardware components for the entire source node design, has been packaged into a complete Xilinx Embedded Development Kit (EDK) IP core that can be installed on any desktop PC and be viewed from the EDK IP Catalog library. The IP is packaged with Tcl [10] scripts that will automatically generate the required C-source code files that allow the core to be accessed in any custom design. This was done to make the core portable and easy to use by future designers. The interface to the core is discussed in detail in the following sections.

Figure 8. Software/hardware architecture.

#### 3.2.2 Software API

When the user selects from one of the provided menu interface options, a series of API function calls are executed by the PowerPC in the background to generate the type of CCSDS packet or RapidIO Maintenance frame requested. The API used for the generation of RapidIO Maintenance frames is standard and is specified in "Annex 1: Software/System Bring Up Specification" of the official RapidIO specification. The API used for the generation of CCSDS packets is non-standard and was designed specifically for this study; however, it follows a similar function layout as the standard RapidIO API library structure.

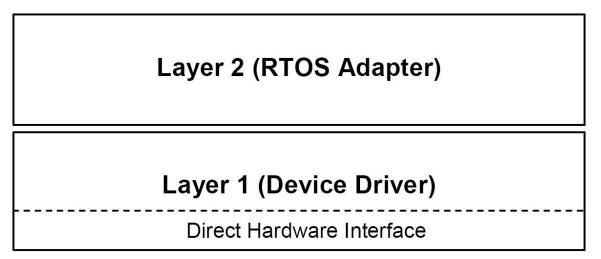

In general, the API device drivers follow a layered architecture as shown in Figure 9. The "RTOS Adapter" functions are callable directly by the user whereas the "Device Driver" functions are meant to be accessed through the adapter functions only. The "Direct Hardware Interface" layer is accessed through the use of the IBM CoreConnect PLB and a Xilinx IP Interface module that allows for software accessible read/write registers within the FPGA's user-programmable logic space.

The RapidIO Maintenance frame generation API drivers consist of four distinct function sets: Hardware Abstraction Layer (HAL), Standard Bring Up, Routing-Table Manipulation, and Device Access Routine (DAR) Interface functions. The HAL functions can be considered Layer 1 functions while the other function sets are part of Layer 2.

Figure 9. Software layers (courtesy Xilinx, Inc.).

There are only two substantial functions within the HAL set – one performs a maintenance read and the other performs a maintenance write. The other three function sets build on top of these two low-level driver functions and allow the user to configure endpoints/switches, monitor state of health, and configure the network topology by populating switch LUTs. At the time of this writing all function sets except for the DAR functions have been fully implemented.

The CCSDS Packet Generation API drivers control the hardware-based CCSDS packet generator module and allow the user to generate fixed or random size CCSDS packets, infinite/finite packet streams, and anything in between. The API functions include error checking, which will ensure that the user only generates CCSDS packets that are within the bounds of the official CCSDS specification.

In a real flight system, the CCSDS API functions would likely not be required, as a hardware interface to a sensor would be used to feed data directly into the CCSDS packet generator module. This would also eliminate the need for the UART and the TUI; however, the PowerPC (or equivalent soft-core processor) would still be required in order to run the aforementioned RapidIO maintenance configuration transactions (please see Section 3.2.5.2 for more information regarding processor requirements).

### 3.2.3 Hardware Interface

Immediately hanging off of the PLB are four software-accessible, 32-bit hardware registers. These registers allow the software to interface to a custom microcontroller that accepts opcodes and parameters. Opcodes sent from the software tell the microcontroller whether it should upload configuration data to the CCSDS packet generator module or the Maintenance frame generator module.

### 3.2.3.1 Send Command Opcode/Data Registers

Opcodes received from the microcontroller by the software inform the user if there is a RapidIO Maintenance response frame waiting to be read. The block diagram shown in Figure 8 refers to this module as the CCSDS to SRIO (CTS) Command and Control (CCC) microcontroller. The microcontroller's Instruction Set Architecture (ISA) presently consists of eight opcodes:

### 3.2.3.1.1 Opcodes for CCSDS Packet Generator

- **C\_CGEN\_LOAD\_HDR** This opcode is used to tell the microcontroller to latch the value in the "Send Command Data" register and set certain option flags and parameters within the CCSDS packet generator. These flags determine the packet generator's use of automatic coarse/fine time generation, the random/fixed packet size, the RapidIO frame priority to use, the RapidIO destination ID, and the RapidIO hop count to the specified destination. Note that the RapidIO parameters are stored in the CCSDS packet's Application Process Identifier field and used by another hardware module later in the packet pipeline.

- **C\_CGEN\_LOAD\_PKTS** This opcode is used to tell the microcontroller to latch the value in the "Send Command Data" register and upload it to the CCSDS packet generator's internal packet count register.

- **C\_CGEN\_LOAD\_WRDS** This opcode is used to tell the microcontroller to latch the value in the "Send Command Data" register and upload it to the CCSDS packet generator's internal packet size register.

• **C\_CGEN\_GO** – This opcode is used to tell the CCSDS packet generator to commence packet generation with the current input configuration. Note that the CCSDS packet generator module must have a valid configuration loaded at least once after power-up before any CCSDS packets can be generated.

#### 3.2.3.1.2 Opcodes for RapidIO Maintenance Frame Generator

- **C\_MGEN\_LOAD\_HDR** This opcode is used to tell the microcontroller to latch the value in the "Send Command Data" register and set certain option flags and parameters within the Maintenance frame generator. These flags determine if the maintenance request is local/remote, the priority level, transaction type, destination ID, and hop count.

- **C\_MGEN\_LOAD\_ADDR** This opcode is used to tell the microcontroller to latch the value in the "Send Command Data" register and upload it to the Maintenance frame generator's internal offset register. The offset determines which RapidIO Capability Register (CAR) or Command and Status Register (CSR) will be read/written.

- **C\_MGEN\_LOAD\_DATA** This opcode is used to tell the microcontroller to latch the value in the "Send Command Data" register and upload it to the Maintenance frame generator's internal data register. This instruction needs to be executed only if the user is performing a maintenance write.

- **C\_MGEN\_GO** This opcode is used to tell the maintenance frame generator to commence frame generation with the current input configuration. Note that the generator module must have a valid configuration loaded at least once after power-up before any frames can be generated.

#### 3.2.3.2 Receive Command Opcode/Data Registers

When performing maintenance reads/writes the CCC module will also provide the maintenance response frame back to the software layer. Each time a maintenance request is generated by the user the software will poll the CCC module until the Receive Command Opcode (RCO) register contains the "Response Register Valid" instruction. If the response register (RREG) is valid, then the endpoint has received the corresponding maintenance response frame.

If the original request was a maintenance write, then the user need only read the "Receive Command Data" (RCD) register once to determine the status of the transaction (e.g., "Done" or "Error"). However, if the original request was a maintenance read, the user must first determine the status of the transaction and then read the RCD register a second time to fetch the maintenance response data.

In addition to informing the software layer of the receipt of a maintenance response frame, the RCO register also has instructions that inform the software of errors within various blocks along the packet/frame generation pipeline. The error opcodes are as follows:

- **C\_CCC\_ERR** A recoverable error has occurred within the CCC module itself. This could be caused by an invalid instruction being sent to the CCC module by the user or due to an error in communication with the packet/frame generator modules.

- **C\_CGEN\_ERR\_0** An invalid packet sequence configuration has been uploaded to the CCSDS Packet Generator module. The user can recover from this error by uploading a valid configuration.

- **C\_CGEN\_ERR\_1** The CCSDS packet storage first in, first out (FIFO) has overflowed and data has been lost. This is an unrecoverable error for debugging purposes.<sup>7</sup>

- **C\_MGEN\_ERR** An invalid frame configuration has been uploaded to the RapidIO Maintenance frame generation module. The user can recover from this error by uploading a valid configuration.

- **C\_SRIO\_BLDR\_ERR\_0** The CCSDS packet storage FIFO has under-flowed and data has been lost. This is an unrecoverable error for debugging purposes.<sup>7</sup>

- C\_SRIO\_BLDR\_ERR\_1 The RapidIO Dword Builder module has received a CCSDS packet with an invalid format. This is an unrecoverable error for debugging purposes but will never be encountered by a standard user since the CCSDS packet generator module only allows the user to generate valid packets.

- **C\_SRIO\_BLDR\_ERR\_2** The RapidIO Dword storage FIFO has overflowed and data has been lost. This is an unrecoverable error for debugging purposes.<sup>8</sup>

- **C\_IGEN\_ERR\_0** The RapidIO Dword storage FIFO has under-flowed and data has been lost. This is an unrecoverable error for debugging purposes.<sup>9</sup>

- **C\_IGEN\_ERR\_1** The Logical Layer RapidIO frame storage FIFO has overflowed and data has been lost. This is an unrecoverable error for debugging purposes.<sup>10</sup>

- C\_IGEN\_MUX\_ERR\_0 The maximum number of outstanding transactions (i.e., number of RapidIO response frames yet to be received) has been exceeded by the Initiator Request (IREQ) Multiplexer module. This is an unrecoverable error for debugging purposes and may be alleviated by increasing the maximum allowed number of outstanding transactions.<sup>11</sup>

<sup>&</sup>lt;sup>7</sup> This error will never occur provided the source node IP created for this demonstration is used.

<sup>&</sup>lt;sup>8</sup> Ibid.

<sup>&</sup>lt;sup>9</sup> Ibid.

<sup>&</sup>lt;sup>10</sup> Ibid.

<sup>&</sup>lt;sup>11</sup> Ibid.

- **C\_IGEN\_MUX\_ERR\_1** A sent RapidIO frame never received its required response. This is an unrecoverable error for debugging purposes.<sup>12</sup> The problem is likely with the original destination node of the original RapidIO request frame.

- **C\_IHAND\_ERR** The Initiator Response (IRESP) Handler module has experienced an unrecoverable error. This error will occur if the IRESP Handler receives an unexpected response frame or an unexpected response frame format type. This error is only for debugging purposes.<sup>13</sup>

The RCO register also contains bits which can be used by the software to determine the empty/non-empty state of the TX and RX FIFOs in the packet/frame generation pipeline or the Xilinx core initialization status. The bit values are as follows:

- **C\_RX\_FIFO\_STAT** A value of 1 means the RapidIO Frame Receive FIFO is empty. A value of 0 means the RX FIFO is non-empty.

- **C\_CGEN\_FIFO\_STAT** Similar to C\_RX\_FIFO\_STAT except for the CCSDS Packet Storage FIFO.

- **C\_SRIO\_FIFO\_STAT** Status of the RapidIO Dword storage FIFO.

- **C\_LOGIO\_FIFO\_STAT** Status of the RapidIO logical layer frame storage FIFO.

- **C\_TX\_FIFO\_STAT** Status of the transmit buffer FIFO, which sits between the Xilinx Logical and Physical Layer Serial RapidIO cores.

- **C\_SRIO\_CORE\_STAT** Status of the Xilinx Physical and Logical Layer cores (4 bits):

- [3] High if the physical layer has experienced no port errors. Low otherwise.

- [2] High if the physical layer has been properly initialized. Low otherwise.

- [1] High if the physical layer receive module is ready to accept data.

- [0] High if the physical layer transmit module is ready to accept data.

#### 3.2.4 CCSDS Packet Encapsulation Pipeline

The CCSDS packet encapsulation pipeline consists of all VHSIC/Verilog Hardware Description Language (HDL) modules extending from the generation of the original CCSDS packet through to the emission of the actual SRIO frame from the Xilinx physical layer core.

<sup>&</sup>lt;sup>12</sup> Ibid.

<sup>&</sup>lt;sup>13</sup> Ibid.

### 3.2.4.1 CCSDS Packet Generator Module (ccsds\_pkt\_gen.vhd)

The CCSDS packet generator module can be configured by the user (through the CTS Command and Control module) to generate any number of CCSDS packets of any size. The configuration state machine within the module will also check to ensure that the user is only loading configurations that will produce valid CCSDS packet formats. If an invalid configuration is loaded, the module will assert an error back to the software layer to notify the user.

The module also has a built-in pseudo-random number generator that can be used to create packets of random size. The random numbers are created using a standard linear feedback shift register (LFSR). The user can choose whether or not to use random-sized packets by sending the C\_CGEN\_LOAD\_HDR opcode to the CTS Command and Control module.

The coarse/fine time generation can also be adjusted to either insert coarse/fine time values from an external data port or to automatically generate a simple incrementing count which will reset at beginning of each new packet sequence. The automated time generation is very useful in debugging the packet transfer pipeline and for debugging received packets on the destination node.

Additionally, the user data within each CCSDS packet can be pulled in from an external data port (see Section 3.5 for an example) or can be automatically generated with a simple incrementing 16-bit count value. When using the automatic user data generation feature the count value will be reset for each new packet. The automated user data feature is very useful in debugging packet flows on both the source and destination nodes.

The CCSDS packet generator module also has a custom 32-bit RapidIO maintenance register (read-only) that can be accessed by the user through RapidIO maintenance read requests from any endpoint in the system. This register allows the user to ascertain the status of the packet generator module by providing information regarding the current state of all internal state machines, the number of user data words yet to be generated for the current CCSDS packet, and the number of packets yet to be sent for the current CCSDS packet sequence. This register is very useful in debugging the packet generator module.

#### 3.2.4.2 RapidIO Dword Builder Module (srio\_dwrd\_bldr.vhd)

The RapidIO Dword Builder module converts 16-bit CCSDS packet words into 64-bit RapidIO dwords. The module pulls 16-bit CCSDS words from the CCSDS packet storage FIFO, packs them into 64-bit RapidIO dwords, and finally writes the dwords to the RapidIO dword storage FIFO. Any CCSDS packet that is not a multiple of 64-bits will have the unused 16-bit chunks within each dword "zeroed out" before being written to the dword storage FIFO.

The RapidIO Dword Builder module also has a custom 32-bit RapidIO maintenance register (read-only) that can be accessed by the user through RapidIO maintenance read requests from any endpoint in the system. The register allows the user to ascertain the status of the Dword Builder module by providing information regarding the current state of all internal state machines and the number of user data words yet to be converted for the CCSDS packet currently being processed.

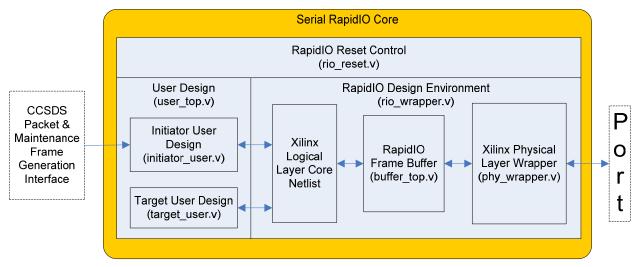

The frame data from the Dword Builder module is stored in a FIFO, where it is eventually read out by lower level blocks in the Serial RapidIO Core design. A high-level block diagram of this core is shown in Figure 10. The components in this core are discussed in the following sections.

Figure 10. Block diagram of Serial RapidIO Core design.

### 3.2.4.3 CCSDS Initiator Request Generator Module (ccsds\_ireq\_gen.vhd)

The CCSDS Initiator Request (IREQ) generator is embedded inside the Initiator User Design block shown in Figure 10. A lower-level block diagram of the components within this module and the interconnections to the Xilinx Logical Layer core are shown in Figure 11. The CCSDS IREQ generator consumes the RapidIO dwords stored in the RapidIO Dword FIFO, encapsulates them into RapidIO Message class frames (i.e., FType 11), and finally forwards each frame onto the logical layer interface frame storage FIFO. Each RapidIO frame, except for (possibly) the very last frame, is the maximum allowed frame size of 256 bytes or 32 64-bit dwords.

RapidIO frame parameters such as the Critical Request Flow (CRF) bit, the frame priority, the destination ID, and hopcount are pulled from the CCSDS packet's API field during frame generation. Additionally, the RapidIO message length (msg\_len) and message segment (msg\_seg) identifier fields are automatically generated by an internal state machine.

It is important to note that the RapidIO Message class has a flow/sequence size limit of 4096 bytes due to the 4-bit msg\_seg/msg\_len fields. SNL's implemented CCSDS specification allows for packets up to 8188 bytes in size (including PHDR, SHDR, and CRC). This size difference poses a problem since it is not possible to encapsulate any CCSDS packet over 4096 bytes in size within a single RapidIO Message flow. In order to resolve this issue, an optional 2-bit field, referred to as the Mailbox bits, within the RapidIO Message frame type were used to add two more bits of resolution to each Message flow, thus allowing a maximum CCSDS packet size of 16384 bytes.

Figure 11. User design internal components.

Similar to the previous modules, the CCSDS IREQ generator module contains a custom 32-bit RapidIO maintenance register (read-only) that can be accessed by the user through RapidIO maintenance read requests from any endpoint in the system. The register allows the user to ascertain the status of the IREQ generator by providing information regarding the current state of all internal state machines, the number of RapidIO dwords yet to be sent to the LOGIO FIFO for the current CCSDS packet being processed, and the number of dwords yet to be sent to the LOGIO FIFO for the current RapidIO frame being processed.

### 3.2.4.4 Initiator Request Multiplexer Module (ireq\_gen\_mux.vhd)

The IREQ Multiplexer component (also shown in Figure 11) accepts requests from the CCSDS IREQ Generator module and the Maintenance Frame Generator for access to the LOGIO FIFO. Access to the LOGIO FIFO is based on a multi-channel "Request"/"Grant" handshaking mechanism. This module is necessary because there is only one IREQ port on the Xilinx Logical Layer core but two modules required access to the logical layer in order to send frames over the network. Therefore, it was necessary to design a module that would arbitrate access between the two transmitters.

In addition to controlling IREQ port access, the IREQ Multiplexer module also updates the transaction ID field for each RapidIO maintenance frame that is sent. Note that the Transaction ID (TID) is not incremented when sending RapidIO frames for CCSDS packets since the RapidIO Message class uses the "msg\_seg" field for identification purposes.

For any sent RapidIO frames requiring a response, this module is also responsible for validating those frames inside the TID Block RAM. This module will also flag an error if the TID Block RAM module exceeds the maximum allowed number of outstanding frames. Additionally, this module ensures that all required responses are received for any frames sent. If either of these errors occurs they are reported back to the software layer.

#### 3.2.5 Maintenance Frame Generation Pipeline

The RapidIO maintenance frame generator pipeline consists of all VHSIC/Verilog HDL modules extending from the generation of the original RapidIO maintenance frame through to the emission of the actual SRIO frame from the Xilinx physical layer core. A block diagram of the components in the pipeline and its interface to the CTS Command & Control Microcontroller is shown in Figure 11.

#### 3.2.5.1 Maintenance Initiator Request Generator (maint\_ireq\_gen.vhd)

The Maintenance IREQ Generator component shown in Figure 11 generates RapidIO maintenance class (i.e., FType 8) read/write requests to offsets specified by the user through software layer functions. This module's configuration interface is almost identical to that of the CCSDS IREQ Generator module. The user may read/write any 32-bit maintenance register on any node attached to the network. Double-word (i.e., 64-bit) transactions or transactions less than 32-bit are not supported.

Since it is impossible for RapidIO to send anything less than 64-bit data chunks within a single frame, the IREQ Generator Multiplexer module will store the original offset address used for the maintenance request inside the TID Block RAM. This offset can then later be used when a corresponding read response is received to determine which half of the double-word quantity was requested by the user.

The Xilinx RapidIO cores support 34-bit addressing; however, the current version of the maintenance frame generator only supports 32-bit addresses. The upper two bits represent the

Extended Address Most Significant Bits field, which is noted in the official RapidIO specification.

## 3.2.5.2 Maintenance Request Generation Without Processor

A processor is the preferred method of generating maintenance transactions; however, if no processor option is available it would be possible to generate a finite set of maintenance commands to various nodes upon startup using an HDL-only implementation. This could be accomplished by storing a pre-defined list of configuration opcodes inside a read-only memory (ROM) that would be read by the CTS microcontroller (see Section 3.2.3) upon boot and sent to the maintenance frame generator module.

An implementation such as this works fairly well for static systems where the topology is fixed and known before power-on; however, it is very limited and can become extremely complex when considering real-time generation of dynamically configured maintenance frames. For example, RapidIO endpoints and switch cores contain numerous status registers, some of which are interrupt/error flags. Some of these flags must be cleared (using maintenance transactions) whenever they are set for continued proper operation of the node.<sup>14</sup>

## 3.2.6 Transaction ID Block RAM (tid\_bram.v)

The TID Block RAM module shown in Figure 11 stores a valid/invalid history of all RapidIO frames sent from the source node that are expected to receive a corresponding RapidIO response frame. The only two frame types the source node sends that require a response are Message class frames (for CCSDS packets) and Maintenance class frames.

The Block RAM is logically separated into two distinct but equal memory spaces. One half of the memory is used for Message class frames and the other half is used for Maintenance frames. This is necessary since the Message and Maintenance classes use different fields for frame identifiers (i.e., the msg\_seg field or the TID field).

On power-up this module will also invalidate (i.e., clear) all TID Block RAM locations before allowing any RapidIO frames to be sent. This prevents possible corruption of the TID memory space.

## 3.2.7 Scratch-Pad Memory Module (target\_user.v)

The source node can be synthesized to either ignore or accept Target Requests (TREQs) from another device on the network. If the source is implemented to accept TREQ frames then frame types 2 (NREAD), 5 (NWRITE), or 6 (SWRITE) may be used to target the source node to test memory reads/writes across the RapidIO network. This module was provided by Xilinx in the reference design included with the core when it was purchased. The scratch-pad memory area is 4 Kbytes in size and is stored in the FPGA's Block RAM.

<sup>&</sup>lt;sup>14</sup> An HDL-only implementation for maintenance transactions was not considered for this demonstration and is beyond the scope of this document.

It is important to note that if the source node is implemented to ignore TREQs then it will appear as if it is unresponsive, since no RapidIO response frames will be sent. The location and interface to the Target User Design module is shown in Figure 11.

#### 3.2.8 Initiator Response Handler (iresp\_handler.vhd)

The IRESP handler module accepts response frames to previously sent message or maintenance class request frames and invalidates the entry for that frame within the transaction ID Block RAM module. Please reference Figure 11 for a block diagram of this module, which includes its interconnections to the Xilinx core and its interface back to the software layer.

When all message class frames for a CCSDS packet have been received, the IRESP handler will report the event to the CCSDS IREQ Generator core, which will allow it to transmit another CCSDS packet.

For maintenance response frames the IRESP handler will extract the appropriate information from the frame and place it in the Response Register so that it may be read by the software layer through the CTS Command & Control module.

#### 3.2.9 RapidIO Design Environment (rio\_wrapper.v)

The RapidIO Design Environment shown in Figure 12 is a Verilog wrapper originally provided by Xilinx when the core is purchased. The wrapper encapsulates both the LOG and PHY layers and also incorporates a store and forward frame buffer design. Xilinx does not require the use of its frame buffer in order to properly operate the Xilinx cores; however, if a custom frame buffer is used it must be of the "store-and-forward" type, as the Xilinx Logical Layer core does not support source side stalls from the PHY.