# Design Specifications for Manufacturability of MCM-C Multichip Modules

Kansas City Division

Chris Allen, Roy Blazek, Jay Desch, Jerry Elarton, David Kautz, Dick Markley, Howard Morgenstern, Ron Stewart, and Larry Warner

## KCP-613-5430

Published June 1995

Approved for public release; distribution is unlimited.

Prepared Under Contract Number DE-ACO4-76-DP00613 for the **United States Department of Energy**

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

#### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade names, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

Printed in the United States of America.

This report has been reproduced from the best available copy.

Available to DOE and DOE contractors from the Office of Scientific and Technical Information, P. O. Box 62, Oak Ridge, Tennessee 37831; prices available from (615) 576-8401, FTS 626-8401.

Available to the public from the National Technical Information Service, U. S. Department of Commerce, 5285 Port Royal Rd., Springfield, Virginia 22161.

Copyright © 1995 by AlliedSignal Inc. The Government is granted for itself and others acting on its behalf a paid-up, nonexclusive, irrevocable worldwide license in this data to reproduce, prepare derivative works, and perform publicly and display publicly.

A prime contractor with the United States Department of Energy under Contract Number DE-ACO4-76-DP00613. AlliedSignal Inc. Kansas City Division P. O. Box 419159 Kansas City, Missouri 64141-6159

## DISCLAIMER

Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.

KCP-613-5430 Distribution Category UC-706

Approved for public release; distribution is unlimited.

## DESIGN SPECIFICATIONS FOR MANUFACTURABILITY OF MCM-C MULTICHIP MODULES

Chris Allen Roy Blazek Jay Desch Jerry Elarton David Kautz Dick Markley Howard Morgenstern Ron Stewart Larry Warner

Published June 1995

© Copyright AlliedSignal Inc., 1995

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

## TABLE OF CONTENTS

| LIST OF FIGURESvi                   |

|-------------------------------------|

| LIST OF TABLESvii                   |

| 1.0 GENERAL                         |

| 1.1 Scope1                          |

| 1.2 Definitions1                    |

| 1.3 References2                     |

| 1.3.1 Documents2                    |

| 1.3.2 Personnel2                    |

| 2.0 PREREQUISITES2                  |

| 2.1 Electrical Requirements2        |

| 2.1.1 Functionality2                |

| 2.1.2 Block Diagram2                |

| 2.1.3 Draft Schematic2              |

| 2.1.4 Electrical Interface          |

| 2.2 Mechanical Requirements3        |

| 2.2.1 Space and Size                |

| 2.2.2 Heat Transfer                 |

| 2.2.3 Mechanical Interface          |

| 2.3 Environmental Requirements      |

| 2.3.1 Radiation                     |

| 2.3.2 Thermal3                      |

| 2.3.3 Hermetic                      |

| 2.3.4 Atmosphere                    |

| 2.3.5 Storage and Transportation    |

| 2.4 Testing Requirements3           |

| 2.4.1 Electrical3                   |

| 2.4.2 Temperature                   |

| 2.4.3 Burn-in                       |

| 2.4.4 Shock and Vibration           |

| 2.4.5 Special4                      |

| 2.4.6 Data Type, Format and Medium4 |

| 2.5 Documentation Requirements4     |

بالمستقدمين الأراب المستقدة بتدوينها والمنافع المنافع المنافع المنافع والمنافع المتحدين والمنافع المحادي والمنافع

-----

-----

.

· · · ·

| 2.5.            | 1 Reports                              | 4 |

|-----------------|----------------------------------------|---|

| 2.5.2           | 2 Analyses                             | 4 |

| 2.5.3           | 3 Drawings                             | 4 |

| 2.6 Other R     | Requirements                           | 4 |

| 2.6.            | 1 Schedule                             | 4 |

| 2.6.            | 2 Quantity                             | 4 |

| 2.6.3           | 3 Cost                                 | 4 |

| 2.6.4           | 4 Classification                       | 4 |

| 2.6.            | 5 Quality Level                        | 4 |

| 3.0 DESIGN CONS | IDERATIONS                             | 4 |

| 3.1 Electric    | cal Design                             | 4 |

| 3.1.            | 1 Schematic Definition                 | 4 |

| 3.1.            | 1.1 New Schematic Symbols              | 5 |

| 3.1.            | 1.2 Schematic Capture                  | 5 |

| 3.1.            | 2 Simulation                           | 5 |

| 3.1.            | 3 Analysis                             | 5 |

|                 | 4 Breadboard                           |   |

| · 3.2 Packag    | ing Design                             | 5 |

| 3.2.            | 1 Electrical Considerations            | 5 |

| 3.2.            | 1.1 Voltages                           | 5 |

| 3.2.            | 1.2 Currents                           | 5 |

| 3.2.            | 1.3 Grounding                          | 6 |

| 3.2.            | 1.4 Isolation (shielding and guarding) | 6 |

| 3.2.            | 1.5 Controlled-Impedance Interconnects | 6 |

| 3.2.            | 1.6 Dielectric Properties              | 6 |

| 3.2.            | 1.7 Propagation Delay                  | 6 |

| 3.2.            | 1.8 Method and Locations of I/O Launch | 6 |

| 3.2.            | 2 Special Considerations               | 6 |

| 3.2.            | 2.1 Radiation                          | 6 |

| 3.2.            | 2.2 Thermal and Hermetic               | 7 |

| 3.2.            | 2.3 Shock and Vibration                | 7 |

| 3.2.            | 3 Component Definition                 | 7 |

| 3.2.            | 3.1 Size (L x W x T)                   | 7 |

| 3.2.            | 3.2 Bond Pad Pitch, Size and Material  | 7 |

| 3.2.            | 3.3 Die Bond Pad Layout (vendor map)   | 7 |

3.3

¥ · · · \*

| 3.2.3.4 Die Technology (GaAs, CMOS, etc.)                                                                                                                                                                                                                                                                                                                                                                                      | 7                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 3.2.3.5 Backside Metallization and Potential                                                                                                                                                                                                                                                                                                                                                                                   | 7                                                                                            |

| 3.2.4 Thermal Analysis                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                            |

| 3.2.4.1 Materials                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                            |

| 3.2.4.2 Semiconductor Devices                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                            |

| 3.2.4.3 Die Attach Technology                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                            |

| 3.2.4.4 Passive Devices                                                                                                                                                                                                                                                                                                                                                                                                        | 8                                                                                            |

| 3.2.4.5 Substrate Configuration                                                                                                                                                                                                                                                                                                                                                                                                | 8                                                                                            |

| 3.2.4.6 Heat Spreader                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                                                                            |

| 3.2.5 Substrate Definition                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                            |

| 3.2.5.1 Thickness and Contour                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                            |

| 3.2.5.2 Layer Allocation                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                                                            |

| 3.2.5.3 Cavity Definition                                                                                                                                                                                                                                                                                                                                                                                                      | 9                                                                                            |

| 3.2.5.4 Power and Ground Planes                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                            |

| 3.2.5.5 Signal Layers                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                                                            |

| 3.2.5.6 Traces and Vias                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                                                            |

| 3.2.5.7 Component Placement                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                                            |

| 3.2.5.8 Bond Pads and Wires                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 3.2.5.9 Test Pads                                                                                                                                                                                                                                                                                                                                                                                                              | 10                                                                                           |

| 3.2.5.9 Test Pads<br>3.2.5.10 Printed Resistors                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                           |

| 3.2.5.10 Printed Resistors                                                                                                                                                                                                                                                                                                                                                                                                     | 10<br>10                                                                                     |

| 3.2.5.10 Printed Resistors                                                                                                                                                                                                                                                                                                                                                                                                     | 10<br>10<br>10                                                                               |

| 3.2.5.10 Printed Resistors         3.2.5.11 Surface Mount Components         3.2.5.12 Pins and Leads                                                                                                                                                                                                                                                                                                                           | 10<br>10<br>10<br>11                                                                         |

| <ul> <li>3.2.5.10 Printed Resistors</li> <li>3.2.5.11 Surface Mount Components</li> <li>3.2.5.12 Pins and Leads</li> <li>3.2.5.13 Soldering Considerations</li> </ul>                                                                                                                                                                                                                                                          | 10<br>10<br>10<br>11<br>11                                                                   |

| <ul> <li>3.2.5.10 Printed Resistors</li> <li>3.2.5.11 Surface Mount Components</li> <li>3.2.5.12 Pins and Leads</li> <li>3.2.5.13 Soldering Considerations</li> <li>3.2.5.14 Brazing Considerations</li> </ul>                                                                                                                                                                                                                 | 10<br>10<br>10<br>11<br>11<br>11                                                             |

| <ul> <li>3.2.5.10 Printed Resistors</li> <li>3.2.5.11 Surface Mount Components</li> <li>3.2.5.12 Pins and Leads</li> <li>3.2.5.13 Soldering Considerations</li> <li>3.2.5.14 Brazing Considerations</li> <li>3.2.5.15 Hermetic Seal</li> </ul>                                                                                                                                                                                 | 10<br>10<br>10<br>11<br>11<br>11<br>11                                                       |

| <ul> <li>3.2.5.10 Printed Resistors</li> <li>3.2.5.11 Surface Mount Components</li> <li>3.2.5.12 Pins and Leads</li> <li>3.2.5.13 Soldering Considerations</li> <li>3.2.5.14 Brazing Considerations</li> <li>3.2.5.15 Hermetic Seal</li> <li>3.2.5.16 Substrate and MCM Marking Requirements</li> </ul>                                                                                                                        | 10<br>10<br>10<br>11<br>11<br>11<br>11<br>                                                   |

| <ul> <li>3.2.5.10 Printed Resistors</li> <li>3.2.5.11 Surface Mount Components</li> <li>3.2.5.12 Pins and Leads</li> <li>3.2.5.13 Soldering Considerations</li> <li>3.2.5.14 Brazing Considerations</li> <li>3.2.5.15 Hermetic Seal</li> <li>3.2.5.16 Substrate and MCM Marking Requirements</li> <li>3.2.5.17 Additional Printing Considerations</li> </ul>                                                                   | 10<br>10<br>10<br>11<br>11<br>11<br>11<br>11                                                 |

| <ul> <li>3.2.5.10 Printed Resistors</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| <ul> <li>3.2.5.10 Printed Resistors</li> <li>3.2.5.11 Surface Mount Components</li> <li>3.2.5.12 Pins and Leads</li> <li>3.2.5.13 Soldering Considerations</li> <li>3.2.5.14 Brazing Considerations</li> <li>3.2.5.15 Hermetic Seal</li> <li>3.2.5.16 Substrate and MCM Marking Requirements</li> <li>3.2.5.17 Additional Printing Considerations</li> <li>3.2.6 Component Summary</li> <li>3.2.7 Substrate Summary</li> </ul> |                                                                                              |

| <ul> <li>3.2.5.10 Printed Resistors</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| <ul> <li>3.2.5.10 Printed Resistors</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| <ul> <li>3.2.5.10 Printed Resistors</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  | 10<br>10<br>10<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>12<br>12<br>12<br>12<br>12<br>12 |

| <ul> <li>3.2.5.10 Printed Resistors</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  | 10<br>10<br>10<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>12<br>12<br>12<br>12<br>12<br>12 |

| 3.3.2 New Component Cells13                |  |

|--------------------------------------------|--|

| 3.3.3 Netlist13                            |  |

| 3.3.4 Physical Features13                  |  |

| 3.3.5 Fiducials13                          |  |

| 3.3.5.1 Wire Bonding and Wire Pull13       |  |

| 3.3.5.2 Component Pick and Place13         |  |

| 3.3.5.3 Test Alignment (both sides)13      |  |

| 3.3.6 Verification and Routing13           |  |

| 3.3.7 Manufacturing Aids14                 |  |

| 3.3.8 MCM and Piecepart Drawings14         |  |

| 3.3.9 Manufacturing and Testing Files14    |  |

| 3.4 MCM Producibility14                    |  |

| 3.4.1 Component Availability and Quality14 |  |

| 3.4.2 Manufacturing15                      |  |

| 3.4.3 Testing15                            |  |

| 3.5 Cost and Delivery Evaluation15         |  |

| 4.0 DELIVERABLES                           |  |

| 4.1 Drawings                               |  |

| 4.1.1 MCM Definition15                     |  |

| 4.1.2 Substrate Definition16               |  |

| 4.1.3 Electrical Component Definitions16   |  |

| 4.1.3.1 Devices                            |  |

| 4.1.3.2 Pins and Leads16                   |  |

| 4.1.4 Mechanical Component Definitions16   |  |

| 4.1.4.1 Seal Ring and Lid16                |  |

| 4.1.4.2 Heat Spreader16                    |  |

| 4.2 Documentation16                        |  |

| 4.2.1 Summaries16                          |  |

| 4.2.1.1 Components17                       |  |

| 4.2.1.2 Substrates                         |  |

| 4.2.2 Analyses17                           |  |

| 4.2.3 Test Plans                           |  |

| 4.2.4 Test Data17                          |  |

| 4.2.5 Cost and Delivery Schedule17         |  |

| 4.2.5 Cost and Delivery Schedule           |  |

| 4.3 | CAD File | S                             | 18 |

|-----|----------|-------------------------------|----|

|     | 4.3.1    | Definition Data (DD) Files    | 18 |

|     | 4.3.2    | Via Drill Coordinates         | 18 |

|     | 4.3.3    | Cavity Cutout Coordinates     | 18 |

|     | 4.3.4    | TKN Resistor Trim Coordinates | 18 |

|     | 4.3.5    | Substrate Test Coordinates    | 18 |

#### APPENDICES

| Appendix A | Material Properties                             | A.1 |

|------------|-------------------------------------------------|-----|

| Appendix B | MCM-C CAD Checklists                            | B.1 |

| Appendix C | Substrate Information and Constraints on Design | C.1 |

| Appendix D | Assembly Information and Constraints on Design  | D.1 |

| Appendix E | Testing Constraints on Design                   | E.1 |

| Appendix F | MCM-C Component Procurement and Engineering     | F.1 |

| Appendix G | MCM-C Design Examples                           | G.1 |

## LIST OF FIGURES

| Figu | Ire                                                     | Page |

|------|---------------------------------------------------------|------|

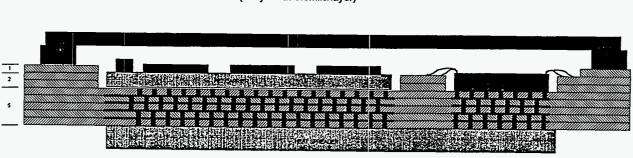

| C.1  | Conceptual Substrate Cross-Section and Layer Allocation | C.2  |

| C.2  | Seal Ring, Braze Pad and Lid Definition                 | C.5  |

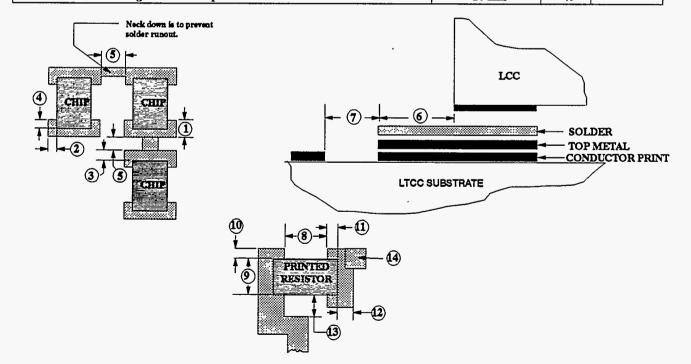

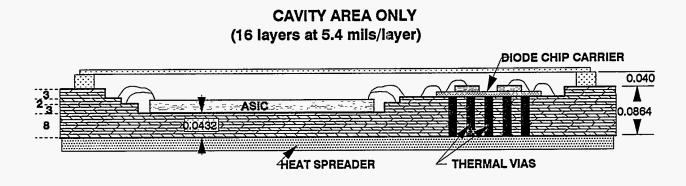

| G.1  | DWS - Packaging Cross-Sectional View                    | G.2  |

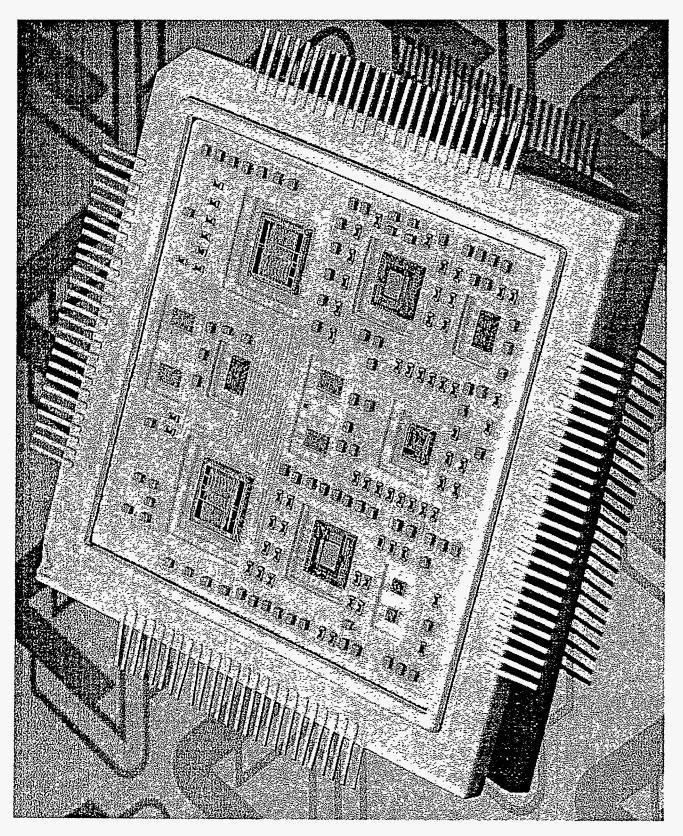

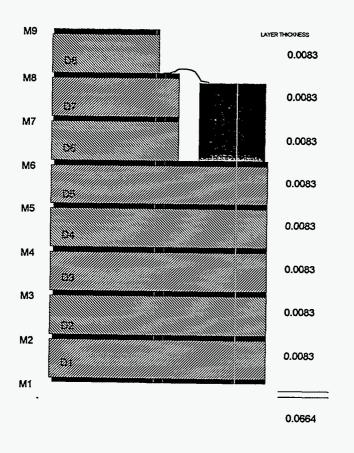

| G.2  | DWS - Photograph with Open Cavity                       | G.3  |

| G.3  | PM - Package Cross-Sectional View                       | G.4  |

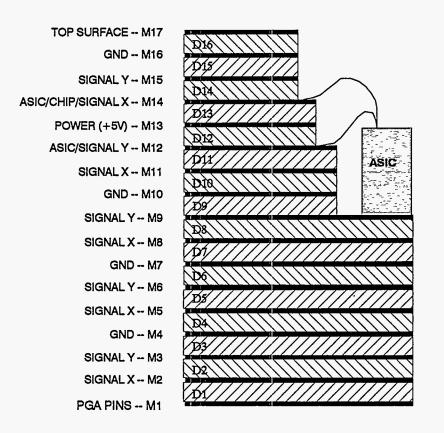

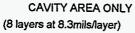

| G.4  | PM - Substrate Layer Allocation                         | G.4  |

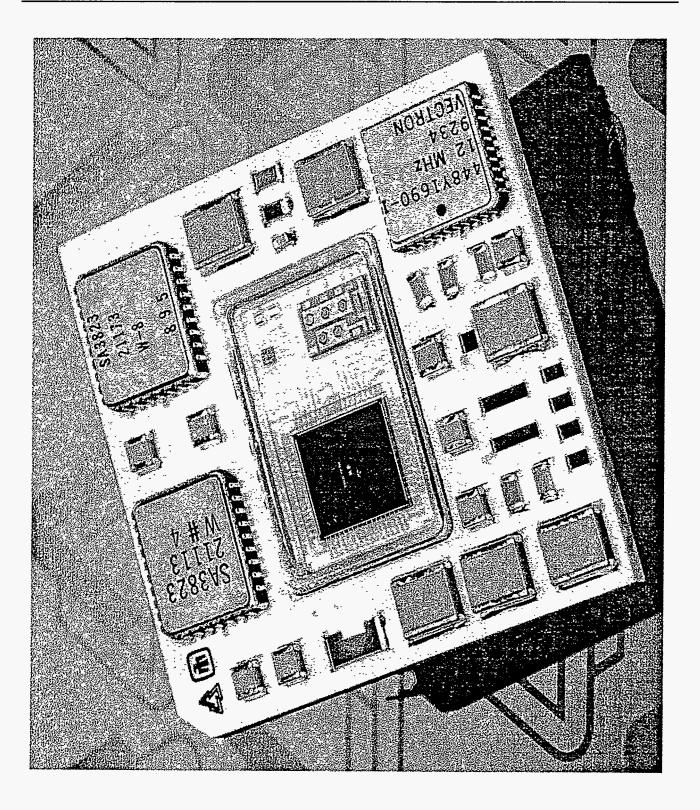

| G.5  | PM - Photograph with Open Cavity                        | G.5  |

| G.6  | IOM - Package Cross-Sectional View                      | G.6  |

| G.7  | IOM - Substrate Layer Allocation                        | G.6  |

| G.8  | IOM - Photograph with Open Cavity                       | G.7  |

.

## LIST OF TABLES

## Table

## Page

|     |                                                                                                      | -       |

|-----|------------------------------------------------------------------------------------------------------|---------|

| A.1 | Properties of Pure Metals                                                                            | A.2     |

| A.2 | Properties of Alloys                                                                                 | A.2     |

| A.3 | Properties of Substrate Materials                                                                    | A.3-4   |

| A.4 | Properties of Adhesive Materials                                                                     | A.5-6   |

| A.5 | Properties of Semiconductor Materials                                                                | A.7     |

| A.6 | Properties of Solder Materials                                                                       | A.8     |

| B.1 | Substrate Pre-Routing Checklist                                                                      | B.2     |

| B.2 | Substrate Post-Routing Checklist                                                                     | B.3     |

| C.1 | LTCC Substrate Dimensional and Parametric Information and Constraints<br>for Typical Dielectric Tape | C.3     |

| C.2 | Typical Paste Properties                                                                             | C.4     |

| C.3 | MCM Substrate Summary                                                                                | C.6     |

| D.1 | MCM-C Assembly Drawing Checklist                                                                     | D.2-4   |

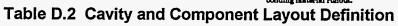

| D.2 | Cavity and Component Layout Definition                                                               | D.5-6   |

| D.3 | Surface Mount Layout Definition                                                                      | D.7-8   |

| D.4 | Substrate Pin, Lead and Seal Ring Attachment                                                         | D.9     |

| D.5 | Die Attachment                                                                                       | D.10-11 |

| D.6 | Wire Bonding                                                                                         | D.12-13 |

| D.7 | Gold Ribbon Bonding                                                                                  | D.14    |

| D.8 | Sealing and Leak Testing                                                                             | D.15    |

| D.9 | Surface Mount Assembly                                                                               | D.16    |

| E.1 | Test Plan Checklist                                                                                  | E.2     |

| F.1 | General Component Considerations                                                                     | F.2     |

| F.2 | MCM Die Component/Assembly Summary                                                                   | F.3     |

| F.3 | MCM Surface Mount Component/Assembly Summary                                                         | F.4     |

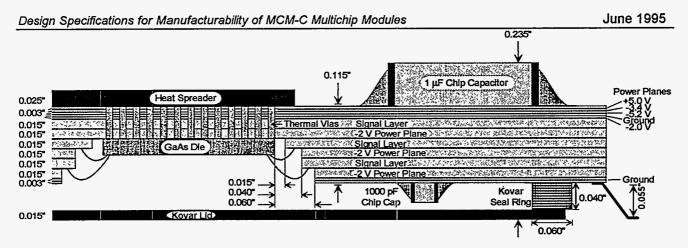

| G.1 | DWS - Substrate Layer Allocation                                                                     | G.2     |

|     |                                                                                                      |         |

.

## 1.0 General

## 1.1 Scope

The scope of this document is to establish design guidelines for electronic circuitry packaged as multichip modules of the ceramic substrate variety, although many of these guidelines are applicable to other types of multichip modules. The guidelines begin with prerequisite information which must be developed between customer and designer of the multichip module. The core of the guidelines focuses on the many considerations that must be addressed during the multichip module design. The guidelines conclude with the resulting deliverables from the design which satisfy customer requirements and/or support the multichip module fabrication and testing processes. Finally. considerable supporting information, checklists, and design constraints are captured in specific appendices and used as reference information in the main body text. The final appendix, Appendix G, presents some real examples of multichip module design.

## **1.2 Definitions**

This document may utilize any of the following acronyms, symbols, units and KCD drawing prefixes.

#### ACRONYMS

- ASCII American Standard Code for Information Interchange

- ASIC application-specific integrated circuit

- BIST built-in self test

- CAD computer-aided design

- CMOS complementary metal-oxide semiconductor

- CVD chemical vapor deposition

- DOE U.S. Department of Energy

- EDMA Electronic Design and Manufacturing Automation

- **ES&H** Environment, Safety and Health organization

- IR infrared

- KCD the Kansas City Division

- KCP the Kansas City Plant

- LCC leadless chip carrier

- LTCC low-temperature cofired ceramic

- MCM multichip module

- MCM-C MCM based on a multilayer ceramic substrate having thick film networks and vias

- MCM-D MCM based on a multilayer substrate developed by depositing each dielectric and metal layer

- MCM-L MCM based on a multilayer laminated substrate similar to a printed wiring board

- MIL-STD Military Standard

- MTBF mean time between failures

- MWCU Modular Weapon Control Unit

- NC numeric control

- PGA pin grid array

- QC quality control

- QCD quality, cost and delivery

- SM surface mount or surface mount device (SMD)

- SPICE Simulation Program with Integrated Circuit Emphasis

- TCE thermal coefficient of expansion

- TFN thin film network

- TKN thick film network

- VHDL Very High Speed Integrated Circuit Hardware Description Language

- WR war reserve

#### SYMBOLS

- Ag silver

- Al aluminum

- AIN aluminum nitride

- Al<sub>2</sub>O<sub>3</sub> alumina

- Au gold

- Be beryllium

- BeO beryllia

- C carbon

- Co cobalt

- Cu copper

- Fe iron

- GaAs gallium arsenide

- Mo molybdenum

- Ni nickel

- Pb lead

- Si silicon

- SiC silicon carbide

- Sn tin

- W tungsten

#### UNITS

- °C degrees Celsius (sometimes just C)

- °F degrees Fahrenheit (sometimes just F)

- °K degrees Kelvin (sometimes just K)

- F frequency (measured in Hz format)

- g gram

- Hz Hertz (kHz =  $10^3$  Hz; MHz =  $10^6$  Hz; GHz =  $10^9$  Hz)

- I current (measured in amps format)

- J joule

- **m** meter (**cm** =  $10^{-2}$  m; **mm** =  $10^{-3}$  m;  $\mu$ m =  $10^{-6}$  m)

- mil 1/1000 of an inch (0.001 inches)

- $\Omega$  resistance (measured in ohms format)

- Pa pascal (MPa =  $10^6$  Pa; GPa =  $10^9$  Pa)

- ppm parts per million (also PPM)

- V voltage (measured in volts format)

- W wattage (measured in watts format)

- Z impedance

#### **KCD DRAWING PREFIXES**

- AC inspection document (substrate and device test)

- AY assembly drawing (MCM and substrate)

- **CK** schematic drawing (MCM only)

- DD definition data (trace and via master patterns)

- (ML) material list (MCM and assembled pieceparts)

- NC numeric description (via numeric locations)

- PS product specification (MCM inspection and test)

### 1.3 References

Several MCM test vehicles have recently been designed and produced in small quantities at KCD. Further, there are several individuals who now possess considerable knowledge of the many facets of MCM design and production and may be used as MCM reference sources.

#### 1.3.1 Documents

As a consequence of the MCM test vehicle development work, the following report is available as reference information.

#### Report No.

KCP-613-5076 High-Speed Digital Project, Waveform Synthesizer (6/93)

Title

As the test vehicle development continues, additional reports will be drafted to document specific areas of MCM development, and all such reports will serve as additional reference information.

#### 1.3.2 Personnel

While many people have participated in the development of the cited MCM test vehicles, the key KCD individuals involved in their design and production have developed expertise in the following areas and may be considered as reference sources.

MCM Design Substrate and MCM Layout Substrate Design and Fab MCM Assembly and Rework MCM Testing

## 2.0 PREREQUISITES

The following subsections detail the desired prerequisite information necessary to successfully initiate the MCM design activities as addressed in Section 3. While such information may be available from the customer, it is more likely that a concurrent effort between the MCM design team and the customer will be needed to develop part of this information.

#### 2.1 ELECTRICAL REQUIREMENTS

#### 2.1.1 Functionality

A brief, high-level description of the MCM functional requirements is required. This description should include information on MCM usage in the user system, and it should provide a concise listing, preferably tabular, of the pertinent functional parameters with associated accuracies and precision.

#### 2.1.2 Block Diagram

An MCM block diagram is desirable and should identify by name:

- the major function blocks within the MCM boundary,

- the signal paths between these blocks, and

- the signal paths crossing the MCM boundary.

#### 2.1.3 Draft Schematic

An MCM draft schematic is necessary to expand the block diagram, and, as a minimum, it must define the module electrical architecture. It can be a completed schematic with all components and interconnects fully identified.

## 2.1.4 Electrical Interface

An electrical interface definition is required to specify the MCM electrical inputs and outputs. Key details to be declared include:

- signal-to-pin or lead assignments;

- interconnect impedances, terminations, loads and bandwidths;

- required stimuli and expected responses; and

- logic levels, sequencing and protocols.

## 2.2 MECHANICAL REQUIREMENTS

### 2.2.1 Space and Size

The physical requirements of the MCM must be identified to establish the maximum available footprint size and headroom for the MCM. If applicable, constraints on MCM mass and/or center of gravity must also be identified.

### 2.2.2 Heat Transfer

Adequate detail of the appropriate user system parameters should be provided so that a detailed MCM thermal analysis can be conducted. As a minimum, such detail should include the available mechanisms and the maximum rate of heat transfer from the MCM to the user system.

### 2.2.3 Mechanical Interface

The MCM mechanical interface must be specified, including information on MCM mounting method and attachment materials. Specified details should include:

- pin or lead geometry and locations and associated tolerances,

- thermal coefficient of expansion of the MCM attachment surface,

- attachment material composition and process temperatures,

- encapsulation materials, and

- location of thermal pathways.

## 2.3 ENVIRONMENTAL REQUIREMENTS

## 2.3.1 Radiation

Radiation environments must be identified, including anticipated radiation types and dose rates. The maximum radiation levels required for MCM survival and continuous operation should also be specified.

#### 2.3.2 Thermal

Thermal environments must be identified since they communicate the anticipated thermal extremes and rates of change for MCM survival and continuous operation.

## 2.3.3 Hermetic

Hermeticity requirements must be specified for the MCM die cavity and should detail the maximum acceptable gaseous leak rates under specific conditions; i.e., pressure, temperature, humidity, gaseous composition, etc. For example, MIL-STD-883D provides specific details for hermetic sealing and testing as applied to microelectronics.

### 2.3.4 Atmosphere

The atmospheric conditions under which the MCM will operate must be specified, including humidity levels (condensing and noncondensing) and atmospheric pressure ranges.

## 2.3.5 Storage and Transportation

The nonoperating environments (storage and transportation events) must be identified for the MCM. These environmental factors should include:

- temperature extremes and cycling,

- humidity levels,

- radiation types and dose rates, and

- shock and vibration duration and spectra.

## 2.4 TESTING REQUIREMENTS

### 2.4.1 Electrical

To electrically verify MCM functionality, the electrical testing requirements must be identified for the MCM. Stimuli and expected responses should be listed for each test sequence specified.

### 2.4.2 Temperature

Operating and nonoperating MCM temperature testing requirements must be specified, including temperature extremes and rates of change.

### 2.4.3 Burn-in

Burn-in requirements must be identified for the MCM, including temperature, duration, MCM operational status (unpowered, powered or operating), and monitoring requirements.

### 2.4.4 Shock and Vibration

Shock and random vibration testing requirements must be specified. Shock test details should include shock waveform shape, peak acceleration, duration, axes to which shock is applied, MCM operational status (unpowered, powered or operating), and monitoring requirements. Vibration test details should include vibration spectra, duration, axes to which vibration is applied, MCM operational status (unpowered, powered or operating), and monitoring requirements.

#### 2.4.5 Special

Special test modes, stimuli and/or responses must be identified for the MCM. Customer resources (expertise, facilities or equipment) should be specified which may be used in detailed test plan development, test setup, test execution, and/or troubleshooting.

### 2.4.6 Data Type, Format and Medium

The data type, format and storage medium for all recorded test data must be identified. Instructions should be provided regarding whether acceptance limits should be recorded with the test data.

#### 2.5 DOCUMENTATION REQUIREMENTS

#### 2.5.1 Reports

A listing of reports to be delivered to the customer shall be specified. A brief description of the scope of each report and its delivery time within the program shall also be specified.

#### 2.5.2 Analyses

Documented analyses to be delivered to the customer shall be specified. A brief description of the scope of each analysis and its delivery time within the program shall also be specified.

#### 2.5.3 Drawings

A list of all drawings to be delivered to the customer shall be specified. A brief description of the content of each drawing, the delivery format and medium, and delivery time within the program shall also be specified.

#### **2.6 OTHER REQUIREMENTS**

In addition to MCM performance and documentation, other customer requirements including cost, quantity, schedule and quality must be defined. Since these items are interrelated and invariably require tradeoffs, the design team can most effectively analyze and communicate such tradeoffs by first understanding the customer's priorities in these areas.

#### 2.6.1 Schedule

A schedule shall be specified indicating the time available for MCM development and production. If applicable, production rates shall also be specified (for example, 10 MCMs per month).

#### 2.6.2 Quantity

The total quantity of fully functional MCMs shall be specified, including the number of prototypes to be

produced in development. Also, any required nonfunctional MCMs must be specified.

#### 2.6.3 Cost

The overall cost of MCM development and the desired production cost per unit shall be specified.

#### 2.6.4 Classification

The level of classification of the MCM shall be specified. If classified, a classification guide shall be provided indicating which aspects of the program are to be protected.

#### 2.6.5 Quality Level

The desired quality level of the assembled MCM shall be specified. This level may range from a desired MTBF to a detailed quality plan.

## 3.0 DESIGN CONSIDERATIONS

The following subsections encompass the many interrelated considerations which must be addressed during an MCM design: electrical, mechanical, packaging, substrate, manufacturing and testing factors. The MCM design must evolve through concurrent, team effort that iterates among the cited factors until the design is optimized, not only for the desired form and functionality, but also for manufacturability and testability.

## 3.1 ELECTRICAL DESIGN

The electrical design of the MCM must produce the schematic definition inclusive of all component symbols, signal I/O definitions, and signal timing relationships or event sequences. This design cannot be considered complete until some degree of design testing is successfully conducted, such as the use of simulation and analysis tools and/or actually breadboarding the design and testing for correct functionality.

#### 3.1.1 Schematic Definition

The MCM schematic, a diagram of the MCM electrical connectivity of a circuit with components represented by graphical symbols, is the first step in the creation of any MCM definition. After the schematic has been completed and verified, it is available for use by MCM design evaluation tools (e.g., bill of materials, circuit simulations, and netlist generation) and for the MCM package design/layout process. Some MCM designs may require the creation of new schematic symbols.

#### 3.1.1.1 New Schematic Symbols

The EDMA system has a large library of commercial components and their schematic symbols (the schematic graphical representation of the electronic components). However, because many MCMs utilize custom ASICs and new technology components, schematic symbols must be created for these new devices to facilitate schematic capture.

#### 3.1.1.2 Schematic Capture

Schematic capture is the process of entering the electrical schematic into the EDMA system along with pertinent defining notes, special net requirements (e.g., conductor width, length, layer and spacing), TKN resistor information and other electronic parameters. This MCM schematic, once entered and verified, becomes the foundation for subsequent substrate layout and automatic routing activities.

#### 3.1.2 Simulation

Simulation of the MCM design offers the ability to manipulate device parameters and study their effects on module performance. The typical sequence of events leading up to a simulation would include the following items.

- The MCM schematic must be captured within the EDMA system.

- Each MCM component, be it ASIC, logic block, clock, transistor, resistor, etc., must be modeled. In the simpler component cases, SPICE or similar models may be available in existing libraries. For the more complex cases such as digital ASICs, a VHDL behavioral model from the die supplier is almost imperative.

- Once the schematic and compatible component models are available for the EDMA simulation, setup conditions such as stimuli, input event timing, and output monitoring can be specified, and then the simulation can be run.

The ability to conduct circuit simulation is currently in an evolutionary state for the EDMA system.

#### 3.1.3 Analysis

Design of an MCM should invariably include several different analyses which give credibility to the design. As a minimum, these analyses should encompass the following areas:

- MCM functional analysis, particularly if simulation is not possible;

- I/O compatibility with the system application;

- component power dissipation, substrate trace, and I/O current carrying capabilities; and

- quantity, piecepart availability, cost and schedule.

#### 3.1.4 Breadboard

Perhaps one of the most effective ways of verifying a new design is to actually build the "MCM" and test it. Usually, the resulting hardware is created from available components (possibly packaged counterparts rather than die devices) and a substrate (possibly a printed wiring board in place of ceramic). Although the final package related effects on functionality can only be extrapolated at best, a valid functional demonstration of the MCM breadboard hardware goes far in validating the MCM design.

#### **3.2 PACKAGING DESIGN**

MCM-C multichip module substrates can serve as both the interconnecting network and the module package. As such, electrical and mechanical design issues must be considered as detailed in the following subsections.

#### 3.2.1 Electrical Considerations

Once the electrical design has been completed, implementation techniques must be identified that will ensure the required electrical performance. Issues to be resolved include power distribution (voltage, current, grounding), and signal integrity (isolation, controlled impedance interconnects, dielectric effects, propagation delay, MCM I/O launch). The product of this effort should be MCM layout and routing rules, a preliminary layer stackup, dielectric tape selection, and a concept for MCM I/O interconnect to the user system.

#### 3.2.1.1 Voltages

All supplied voltages required for MCM operation shall be identified and named. Power planes may be dedicated to any voltages which are used by many components. To minimize any variation in potential across the MCM, each power plane should be connected to the user system with multiple pins or leads. Voltages requiring special attention should be indicated; e.g., high voltage.

#### 3.2.1.2 Currents

Anticipated currents (average and peak) for each supplied voltage should be identified. Connections and traces (signal, power or ground) expected to carry large currents should be indicated, and the techniques used to accommodate such currents should be described. Techniques used to accommodate high currents include:

- parallel pins or leads for current splitting;

- wider traces; and

- larger bond wire diameters, ribbons and/or multiple wires (refer to Tables D.6 and D.7).

#### 3.2.1.3 Grounding

One or more dedicated ground planes may be used to provide a low impedance, uniform reference across the MCM. To minimize any variation in ground potential across the MCM, the ground plane should be connected to the user system with multiple pins or leads.

## 3.2.1.4 Isolation (shielding and guarding)

Signals requiring isolation to minimize undesired energy coupling must be identified. Isolation techniques (such as shielding and guarding) should be evaluated for effectiveness and design complexity. The selected technique must then be incorporated into the layout rules for this class of signals. These rules could include minimum trace separation, routing alternating layers in orthogonal directions, or placing a power or ground plane between routing layers.

## 3.2.1.5 Controlled-Impedance Interconnects

Controlled-impedance transmission lines are needed to transmit high-speed signals; i.e., signals with transition times less than the signal propagation times between the source and destination. Geometries providing controlled impedance include microstrip, stripline, slotline and coplanar. Factors affecting geometry selection include:

- ceramic dielectric properties,

- cross-talk and isolation requirements,

- desired signal density and the number of available routing layers, and

- accuracy and precision of trace fabrication processes.

Once a transmission line structure has been selected, parameters such as dielectric thickness, dielectric permittivity, trace width, and trace thickness can be specified for 50  $\Omega$  characteristic impedance signal connections. Additionally, a parametric sensitivity analysis of the characteristic impedance should be performed with regard to variations in these same parameters to evaluate the impact of material and process variations.

#### **3.2.1.6 Dielectric Properties**

Dielectric properties of the substrate material affect controlled-impedance, transmission line design, signal coupling, distributed line capacitance, and other characteristics. Selection of the dielectric material to be used in the MCM substrate should include an examination of these effects. Table A.3 lists several substrate materials and their dielectric properties including relative dielectric constant (or permittivity), loss tangent, and electrical resistivity.

#### 3.2.1.7 Propagation Delay

For synchronous signals, such as digital data buses or clock distribution networks, the propagation delay of each signal must be controlled to avoid undesired timing skew. Matched trace lengths integrated into the layout rules can limit layoutinduced skews.

## 3.2.1.8 Method and Locations of I/O Launch

The electrical interface between the MCM and the user system must be designed to transmit the signal content accurately. Factors which degrade the transmission include coupling from adjacent signals, impedance mismatches, reactive loading, and path resistance. To ensure a quality electrical interface, an analysis should be performed on the launch geometry and interface materials. Factors which can usually be varied to enhance interface integrity include signal pin assignment, pin or lead dimensions, and pin or lead spacing.

In addition to I/O launch by pins or leads, other launch techniques include pigtail cable, SM connector, optical interconnect, etc.

#### 3.2.2 Special Considerations

In addition to the normal electrical operating considerations discussed above, special environmental conditions may impact package design.

#### 3.2.2.1 Radiation

Exposure to radiation can adversely affect MCM performance; therefore, radiation considerations must be included in the MCM design. Various design methods are available to manage the radiation effects, depending on the type of radiation (photons, charged particles, neutrons) and the operating requirement (operate through or allow shutdown during radiation events). These methods include circumvention, shielding, careful layout of metals and dielectrics, component selection, redundant functions, etc. Analysis and customer

1.3 +

requirements will dictate the methods to be implemented.

#### 3.2.2.2 Thermal and Hermetic

The thermal and atmospheric environments the MCM is intended to operate in may affect MCM design. Ambient temperature and the heat sinking capacity of the user system could limit the power dissipation of the MCM and affect MCM reliability. Hermeticity requirements impact cavity sealing options. Other design areas which can potentially degrade MCM hermeticity include thermal vias, substrate material, and lid design.

#### 3.2.2.3 Shock and Vibration

Mechanical shock and vibration requirements will affect the MCM design with regard to maximum acceptable wire bond length, minimum substrate thickness, substrate material selection, mechanical interface design, and encapsulation within the user system. Analysis and/or laboratory testing may be required to validate the MCM design.

#### 3.2.3 Component Definition

A definition is required for each unique component to be used in the MCM design. The component characteristics which are essential for proper MCM design are detailed in the following subsections.

#### 3.2.3.1 Size (L x W x T)

The length, width and thickness dimensions are required for each component.

## 3.2.3.2 Bond Pad Pitch, Size and Material

Information about bond pad dimensions, pitch and the material composition is required for MCM layout and assembly.

## 3.2.3.3 Die Bond Pad Layout (vendor map)

A die bond pad layout showing the location of all bond pads with meaningful names is required for MCM layout and assembly. This information could be in the form of a die photograph or a scaled drawing.

## 3.2.3.4 Die Technology (GaAs, CMOS, etc.)

Knowledge of the die technology is required to establish appropriate assembly, handling and testing processes. Die technology includes semiconductor material (Si or GaAs), logic type (TTL, CMOS, FET, ECL, etc.), and information on die passivation.

## 3.2.3.5 Backside Metallization and Potential

Knowledge of the semiconductor die backside potential is required so that the die attach pad may be connected to the proper voltage or allowed to float. Also, information regarding the semiconductor die backside metallization is required as it impacts die attach options.

#### 3.2.4 Thermal Analysis

A thermal analysis is always in order for any MCM design. Failure to adequately design for MCM self-heating can result in component drift, reduced MTBF, and catastrophic failure. Several factors must be examined in the thermal analysis. These are addressed in the following subsections.

#### 3.2.4.1 Materials

The materials used in the MCM are critical to its thermal performance. The thermal conductivity of the material affects the temperature differential between the heat generating devices and the surface of the MCM. Also, any TCE mismatches between MCM materials will result in mechanical tension and compression which can cause fatigue, micro-cracking and, if severe enough, component fracture. The material selection process must address these issues. As an aid, Appendix A provides a convenient reference for some key properties of materials used in multichip module applications, including TCE.

#### 3.2.4.2 Semiconductor Devices

From a thermal analysis viewpoint, semiconductor devices are just another MCM material and have the same considerations mentioned previously. In addition, the semiconductor devices will likely represent a heat source. Active devices (transistors, diodes) on the surface of the semiconductor die not only dissipate heat but are also the focus of concern in the thermal analysis. Material properties of silicon and gallium arsenide devices are presented in Table A.5.

Semiconductor MTBF is often directly related to device junction temperature; i.e., shorter MTBFs are associated with higher operating junction temperatures. Thus, a thermal analysis will often strive to achieve a given junction temperature (hence, a device MTBF) by minimizing the thermal impedance between the surface of the die and the outer surface of the MCM. One option available to the designer is die thinning by the die supplier. Die material (Si or GaAs) may be the source of significant thermal impedance. By thinning the die, the thermal impedance due to the die itself can be reduced. Another alternative is to flip-chip bond the die to the substrate with z-directional electrically conductive epoxy, thereby placing the active surface of the die in close proximity to the substrate. However, this technology is not currently available at KCD.

#### 3.2.4.3 Die Attach Technology

The basic goal of MCM thermal analyses is to minimize the thermal impedance between the semiconductor die surface (where the active, heatgenerating junctions are located) and the outer surface of the MCM (where the heat transfer to the environment or to the user system occurs). Die attach techniques dramatically impact this thermal impedance between the semiconductor die and the MCM substrate. Many adhesive materials are available and several are included in Tables A.4 and D.5. Metal attach methods such as solders and eutectics are not currently compatible with cofired substrate technology due to irregular surfaces and incompatible metal systems.

#### 3.2.4.4 Passive Devices

Passive devices may also represent a significant source of heat dissipation within the MCM. In these cases, an acceptable operating device temperature must be determined which in turn dictates the maximum acceptable thermal impedance between the heat dissipating device and the MCM outer surface. As in the case of die attach, component attachment techniques and material selection can be critical to the thermal performance.

#### 3.2.4.5 Substrate Configuration

MCM thermal characteristics are often dominated by the substrate characteristics. Thus, special attention should be paid to the thermal design of the substrate.

One factor impacting substrate thermal performance is the thickness of the substrate beneath the heat-dissipating devices. By placing these devices in cavities, substrate thickness can be reduced locally.

Another option available to the designer is the use of thermal vias. Cofired metals typically have significantly higher thermal conductivity than cofired ceramics. Therefore, by placing dense arrays of large, metal-filled vias beneath hot components, the thermal impedance through the substrate can be significantly reduced. Substrate fabrication capabilities limit the maximum size and packing density of these thermal vias as stipulated in Table C.1.

#### 3.2.4.6 Heat Spreader

To facilitate heat transfer, use of a heat spreader is sometimes beneficial. A heat spreader is a layer of material with a relatively high thermal conductivity which spreads the heat flow laterally and increases the heat transfer surface area. Materials usually considered for heat spreading application include metals (copper and aluminum), metal alloys with TCEs close to those of ceramics (Kovar, Invar and others), ceramics with good thermal properties (alurninum nitride, beryllia, silicon carbide), and synthetic diamond (CVD and polycrystalline). Properties of these materials are listed in Tables A.1, A.2 and A.3. Selection of a heat spreader material must include evaluation of the material's thermal and electrical properties, density, ES&H concerns, and cost.

Current substrate fabrication capabilities require that heat spreaders not be integral parts of the substrate; rather, the heat spreader must be added in a subsequent MCM assembly process. Heat spreaders can be used both internal to the MCM (as a component carrier) and external to the MCM thereby enhancing heat transfer to the user system or the environment. In either case, attachment techniques (solder, thermoplastic adhesive, epoxy) will impact overall thermal transfer characteristics and must be included in the analysis.

#### 3.2.5 Substrate Definition

This section discusses the information that must be gathered and defined to design an LTCC substrate. Fabrication considerations and constraints are addressed because of equipment, tooling and/or process limitations. If additional information is required or the application presents unique fabrication considerations, the substrate engineer should be contacted for assistance.

Throughout the LTCC substrate design, all design dimensions are post-fired (final) dimensions. Dimensions that apply to the pre-fired green tape are simply scaled up to account for the tape shrinkage that will occur during the firing process (about 13% in length and width and about 15% in thickness).

#### 3.2.5.1 Thickness and Contour

The minimum post-fired thickness for an MCM-C substrate is set at 40 mils at its thinnest point (typically in the cavity area). The minimum thickness for an MCM-C substrate outside the

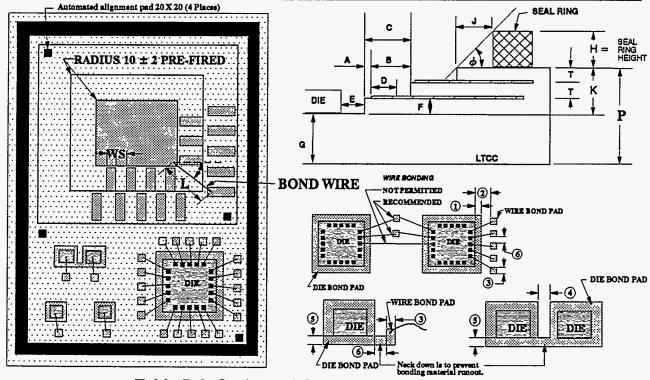

cavity area is set at 60 mils. These thicknesses are established to ensure that the LTCC substrate will have a strength similar to a 25-mil-thick alumina substrate (see Table D.2.). The tightest dimensional tolerance on the contour of a substrate can be held if the substrate is rectangular (see Table C.1). Arcs, keyways and irregular shapes are possible but not with tight tolerances because they are cut before firing. The largest post-fired substrate possible is a 2.25-inch square or 2.25 inches on the minor side of the rectangle as restricted by the current work holder and automated wire bonding tool. Other substrate sizes may be possible after consultation with the substrate and assembly engineers.

#### 3.2.5.2 Layer Allocation

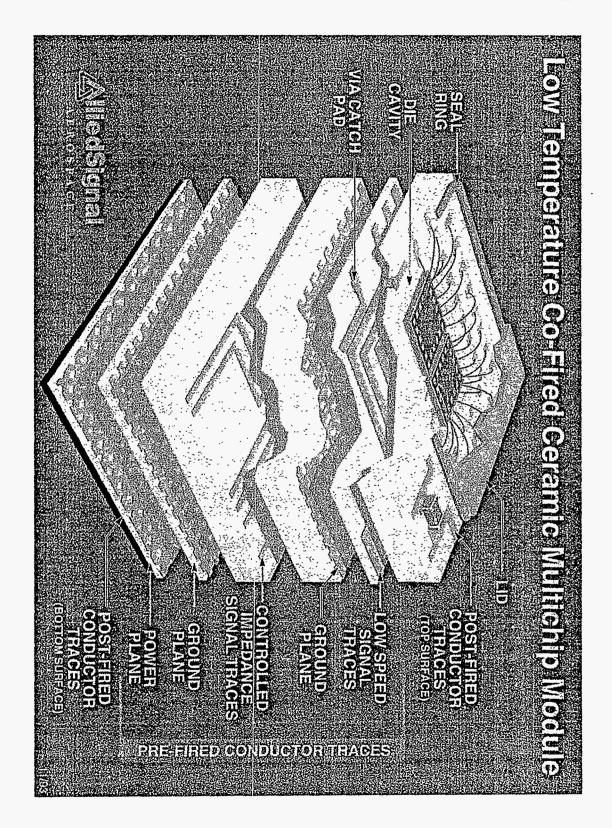

Layer allocation is a two-step process: first, establishing the number of layers for the designed and second, assigning electrical thickness. functionality to each layer. The substrate thickness will be based on the mechanical requirements of the substrate and its physical features including those layers which form the die cavity. The electrical functionality of the substrate layers will be assigned based on the number of ground and/or required and the electrical power planes interconnect density of the signal layers. Finally, if required, layer assignment must include any stripline or microstrip traces with appropriate layer separation from related ground or power planes (see Figure C.1).

#### 3.2.5.3 Cavity Definition

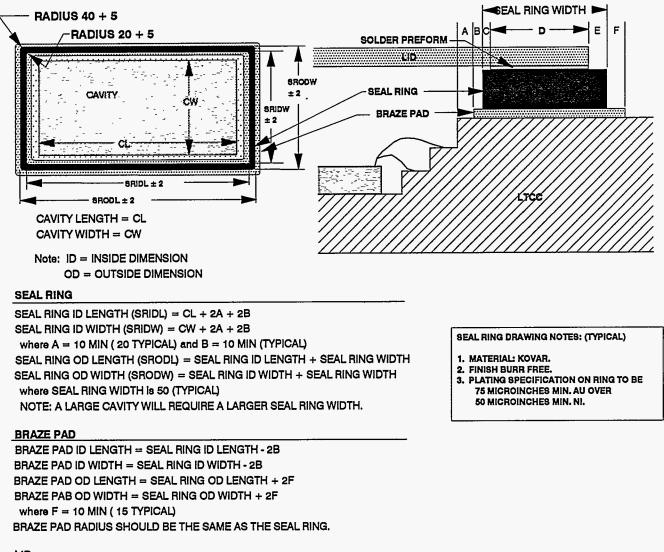

The MCM design will typically have a hermetically sealable cavity area where bare die components can be attached and bonded to the substrate. The maximum cavity depth is 150 mils, inclusive of seal ring height, as restricted by the substrate test system, and it is measured from the lowest wire bond pad (substrate or die) to the top of the seal ring. Table D.2 provides design guidelines for the die bond pad and wire bond pad features for bare die components. Table D.5 provides general processing information about the different die attach materials, and Tables D.6 and D.7 provide information about different bond wire and ribbon materials and assembly processes. After the final cavity size has been determined, Figure C.2 presents a method for defining the seal ring, seal ring braze pad, and lid dimensions.

#### 3.2.5.4 Power and Ground Planes

Usually, voltages and grounds are distributed to the MCM components by metal planes designed into specified substrate layers, one plane for each voltage and ground. Each plane is typically composed of metal printed on the specified layer in a cross-hatched pattern. The cross-hatching enhances lamination adhesion to the adjacent tape layer. Table C.1 provides guidelines for defining such planes, including the material pattern and clearance requirements for vias.

#### 3.2.5.5 Signal Layers

An adequate number of substrate signal layers must be defined so that all of the MCM interconnections can be successfully routed. Signal layers are normally defined as a pair of two conductor layers where one layer is used to route traces primarily in an X direction while the traces on the other layer are routed primarily in the Y direction. This orthogonal routing technique tends to reduce coupling between layers and retain planar external surfaces.

#### 3.2.5.6 Traces and Vias

The recommended width for an internal trace is 8.7 mils (10 mils, pre-fired). Spacing between traces should be 8.7 mils (10 mils, pre-fired). Wider traces are possible for unique signal properties. Traces of lesser widths are possible, but substrate yield could be reduced. The recommended diameter for an internal electrical via is 8.7 mils (10 mils, pre-fired). Larger via diameters are possible, but the ratio of via diameter to tape thickness becomes critical (the ink may not remain in the via until firing). Smaller via diameters are possible, but forcing the ink into the smaller via becomes more difficult and substrate yield would be reduced. Each electrical via must have a cover pad that is twice the via's diameter. The minimum spacing between electrical via centers should be three times their diameter. Vias should be staggered every two layers with a minimum stagger of twice the via diameter. Thermal vias are treated separately from electrical vias. Their recommended diameter is 17.4 mils (20 mils, pre-fired). The minimum spacing between thermal via centers should be twice the via diameter. The thermal vias do not require cover pads.

These recommendations are tabulated in Table C.1 along with more detailed recommendations for traces and vias. Also, a summary of typical paste properties is presented in Table C.2.

#### 3.2.5.7 Component Placement

Component placement on the substrate should follow the guidelines listed in Table D.2 for die and Table D.3 for surface mount components. In general, components should be placed to provide adequate room for attachment and connection. Components should be placed and oriented for the shortest trace interconnect lengths. The interconnect length of high-speed signal traces requires particular attention.

#### 3.2.5.8 Bond Pads and Wires

After each die has been attached to the substrate, it must be electrically connected to the substrate. This interconnect is accomplished with wires bonded between appropriate die and substrate bond pads. It is recommended that the substrate bond pads be at least 10 mils square. The spacing (gap) between bond pads should also be 10 mils. In general, the wire length from die to substrate should not be over 100 mils. Additional recommendations in this area are listed in Table D.2. Details on the physical limitations of the wire and ribbon bonding processes, rework procedures, and current carrying capabilities are listed in Tables D.6 and D.7.

#### 3.2.5.9 Test Pads

Test pads may be included in any MCM design. Some of these pads (test points) can aid in pre-lid and post-lid MCM electrical testing. Other test points can be utilized to verify substrate integrity (i.e., nonfunctional continuity loops). Such pads must be considered in the very early phases of any design and directly reflect the substrate and module test plans. Typical test pads are 30-mil-square pads.

#### 3.2.5.10 Printed Resistors

The EDMA system has the capability of designing thick film resistors based on specified design factors. These factors include geometry, resistor inks, aspect ratio, power, voltage and other parameters. The basic resistor material parameters are defined in Table C.1, and resistor pad dimensions are defined in Table D.3. The remaining parameters are based on the specific resistor application.

There are three basic considerations associated with thick film resistor designs:

- resistance value,

- required power dissipation, and

- allowable resistance tolerance.

The resistor value is defined by its length-to-width ratio; the power dissipation is a function of the resistor area; and the resistor tolerance is a function of the manufacturing processes.

The resistor value is defined by the resistor material (sheet resistance) and the length-to-width ratio of the resistor; neither the width nor the length of the printed resistor should be less than 50 mils. This resistance value may be calculated as

. . . . . . . . . . . .

Resistance =

$$\frac{\text{sheet resistance} \times \text{length}}{\text{width}}$$

For a given power dissipation, an equation for calculating the minimum resistor width is as follows:

$$W = \sqrt{\frac{P \cdot P_s}{D \cdot R}} ,$$

where

- P = maximum power dissipation in resistor (mW);

- $P_s$  = sheet resistance of resistor material (ohms/sq.);

- D = power density rating of system (W/sq.in.);

- R = resistor value (k ohms); and

- W = minimum resistor width (mils).

Thick film resistors can typically be printed to within  $\pm 35\%$  of nominal value. However, thick film resistors are typically trimmed closer to nominal value with a tolerance listed in Table C.1. The trimming operation can only provide an increase in resistance; therefore, the resistor should be designed to 70% of the final value.

All resistors that are to be trimmed or have their values measured must have connected probe pads. However, since the resistor trimming operation generally occurs before components are attached, probe areas may naturally exist without resorting to the addition of special probe pads (for example, the conductor pad for a capacitor may be schematically connected to one side of the resistor; thus, no special probe pad will be required on the substrate).

#### 3.2.5.11 Surface Mount Components

These components are usually LCCs, chip resistors, or chip capacitors. Guidance on their layout, attachment and rework is provided in Tables D.3 and D.9. Interconnect traces for these components are typically located on internal layers to eliminate solder dams. The surface mount pads used for attaching these components must be a double printing of platinum/gold. This double print is required to minimize the tin/lead solder from leaching the gold out of the vias and causing opens.

#### 3.2.5.12 Pins and Leads

Pins or leads are typically used for the electrical interface and mechanical support between the

. . . . .

MCM and the user system. The dimensions of these parts must be defined. For example, a pin definition should include the pin diameter and length and the pin head diameter and thickness. Likewise, a lead definition must include lead length and thickness where the initial length may be associated with lead frame dimensions and the final length would then be the trimmed length following lead frame-to-substrate assembly. Pins and leads typically have a base material of Kovar with a plating specification of 75 microinches minimum Au over 50 microinches minimum of electrolytically plated Ni.

#### 3.2.5.13 Soldering Considerations

There are many options for soldering components to the substrate. The primary consideration is to choose a solder system compatible with the component termination material. A common solder used is 63/37 tin/lead. It can be applied by screen printing, preforms or automated dispensing. Component reflow soldering attachment can be accomplished by using a convection or IR belt furnace or a vapor phase chamber. Tin/lead and eutectic solder properties are presented in Table A.6, and a description of the solder and rework processes is contained in Table D.9.

#### 3.2.5.14 Brazing Considerations

Brazing (high-temperature soldering) is possible with LTCC MCMs. Typically, it is used to attach pins or leads and a seal ring. The ability to braze a seal ring to the substrate allows a hermetic die cavity to be formed with the addition of a lid. Several constraints and recommendations on the design of a seal ring, its braze pad, and the companion lid are illustrated in Figure C.2. A braze pad must be printed on the substrate before the seal ring is attached. The braze pad is composed of two separate ink layers: an adhesion layer and a barrier layer, printed sequentially as listed. The adhesion layer must be printed 5 mils smaller on a side than the barrier layer. The barrier layer is between the adhesion layer and the braze solder. The braze solder material can be based on a gold/tin system. If it is printed on, it must be printed 5 mils less on a side than the barrier layer printing. The manufacturing process for attaching the seal ring is listed in Table D.4 and is typically a belt furnace operation using graphite fixturing.

Pins or leads can also be attached using the process described above. The printed braze solder can be eliminated if the pins or leads are purchased with a solder preform already attached or if a solid preform is used. The manufacturing process used

for attaching the pins or leads is also described in Table D.4.

#### 3.2.5.15 Hermetic Seal

With a seal ring brazed to the LTCC substrate around the die cavity, the cavity can then be sealed by brazing a lid to the ring after die assembly. Recommendations for specifying the seal ring and lid are contained in Figure C.2. The process of attaching the lid to the seal ring is described in Table D.8 along with the methods used to test for hermeticity. It should be noted that testing per MIL-STD 883 requires different preconditioning parameters depending on the cavity size. The particular parameters requiring consideration for a specific size can be found in the MIL-STD or by consulting the assembly engineer.

## 3.2.5.16 Substrate and MCM Marking Requirements

To provide traceability, the MCM and its substrate can both be marked for identification (part and serial numbers as a minimum) by specifying location, size, format and method of the marking characters. The marking area must be proportional to the amount of encoded information and the application method. The final identifying characters can be marked on the lid or on a section of exposed substrate. In-process identification can be placed under surface mount components. In all cases, adequate room must be allocated in the design.

## 3.2.5.17 Additional Printing Considerations