# Implementation of MP\_Lite for the VI Architecture

by

Weiyi Chen

A thesis submitted to the graduate faculty in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

Major: Computer Science

Program of Study Committee: Ricky A. Kendall, Co-major Professor Srinivas Aluru, Co-major Professor Lu Ruan

Iowa State University

Ames, Iowa

2001

Sec. Starter

Graduate College Iowa State University

This is to certify that the Master's thesis of

Weiyi Chen

has met the thesis requirements of Iowa State University

Co major Professor

mil

Comajor Professor

For the Major Program

. <

ii

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS                           |                                           |    |  |  |  |  |  |

|-------------------------------------------|-------------------------------------------|----|--|--|--|--|--|

| ABSTRACT                                  |                                           |    |  |  |  |  |  |

| CHAPTER 1. INTRODUCTION                   |                                           |    |  |  |  |  |  |

| 1.1                                       | Parallel Computing                        | 1  |  |  |  |  |  |

| 1.2                                       | Communication in Parallel Computers       | 2  |  |  |  |  |  |

| 1.3                                       | The Goal of This Thesis                   | 3  |  |  |  |  |  |

| 1.4                                       | Organization                              | 4  |  |  |  |  |  |

| 1.5                                       | Other Research Efforts                    | 4  |  |  |  |  |  |

| CHAPTER 2. COMMUNICATION WITHIN A CLUSTER |                                           |    |  |  |  |  |  |

| 2.1                                       | Parallel Virtual Machine                  | 7  |  |  |  |  |  |

| 2.2                                       | Message Passing Interface                 | 8  |  |  |  |  |  |

|                                           | 2.2.1 MPICH                               | 10 |  |  |  |  |  |

|                                           | 2.2.2 LAM MPI                             | 11 |  |  |  |  |  |

|                                           | 2.2.3 MP_Lite                             | 1  |  |  |  |  |  |

| 2.3                                       | Other Message-Passing Libraries           | 4  |  |  |  |  |  |

| 2.4                                       | User-level Networking 1                   | .5 |  |  |  |  |  |

|                                           | 2.4.1 Active Messages                     | 5  |  |  |  |  |  |

|                                           | 2.4.2 U-Net                               | 6  |  |  |  |  |  |

|                                           | 2.4.3 Fast Messages                       | 6  |  |  |  |  |  |

|                                           | 2.4.4 Virtual Memory-Mapped Communication | 7  |  |  |  |  |  |

|                                           | 2.4.5 Basic Interface for Parallelism     | 7  |  |  |  |  |  |

|                                           | 2.4.6 Scheduled Transfer Protocol         | 7  |  |  |  |  |  |

.

|                                                    |      | 2.4.7 Virtual Interface Architecture             | 18 |  |

|----------------------------------------------------|------|--------------------------------------------------|----|--|

|                                                    | 2.5  | VIA Implementations                              | 22 |  |

|                                                    |      | 2.5.1 M-VIA                                      | 22 |  |

|                                                    |      | 2.5.2 The Berkeley VIA Implementation            | 23 |  |

|                                                    |      | 2.5.3 Commercial Products                        | 23 |  |

|                                                    | 2.6  | VIA Implementations for MPI                      | 23 |  |

|                                                    |      | 2.6.1 MVICH                                      | 23 |  |

|                                                    |      | 2.6.2 M-VIA for LAM MPI                          | 24 |  |

|                                                    |      | 2.6.3 VIA for MPI/PRO                            | 25 |  |

|                                                    |      | 2.6.4 MPI Implementation on the NTSC VIA cluster | 25 |  |

|                                                    |      | 2.6.5 MP_Lite M-VIA                              | 25 |  |

| C                                                  | HAP  | TER 3. IMPLEMENTATION OF MP_LITE FOR M-VIA       | 26 |  |

|                                                    | 3.1  | System Overview                                  | 26 |  |

|                                                    | 3.2  | Queue Management                                 | 28 |  |

|                                                    | 3.3  | Buffer Management                                | 29 |  |

|                                                    | 3.4  | Important Data Structures                        | 31 |  |

|                                                    | 3.5  | Initialization                                   | 32 |  |

|                                                    | 3.6  | Communication Protocols                          | 34 |  |

|                                                    |      | 3.6.1 The Eager Protocol                         | 35 |  |

|                                                    |      | 3.6.2 The Handshake Protocol                     | 36 |  |

|                                                    | 3.7  | Dynamic Memory Registration                      | 38 |  |

|                                                    | 3.8  | Send                                             | 38 |  |

|                                                    | 3.9  | Receive                                          | 40 |  |

|                                                    | 3.10 | Channel-Bonding                                  | 42 |  |

|                                                    | 3.11 | Finalization                                     | 44 |  |

|                                                    | 3.12 | Porting M-VIA to the Alpha Platform              | 44 |  |

| CHAPTER 4. PERFORMANCE OF MP_LITE M-VIA ON LINUX 4 |      |                                                  |    |  |

|                                                    | 4.1  | Experimental Environment                         | 46 |  |

|                                                    |      |                                                  |    |  |

|       | 4.1.1           | Configuration                             | 46 |  |  |

|-------|-----------------|-------------------------------------------|----|--|--|

|       | 4.1.2           | NetPIPE Performance Evaluator             | 47 |  |  |

| 4.2   | Point-          | to-Point Communication                    | 47 |  |  |

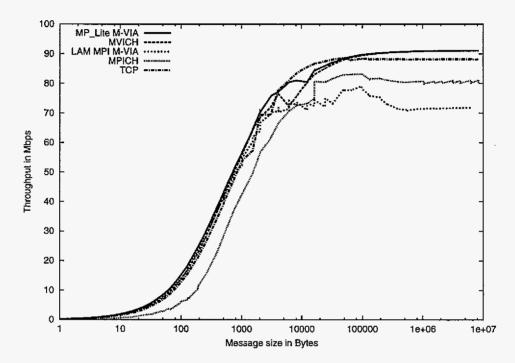

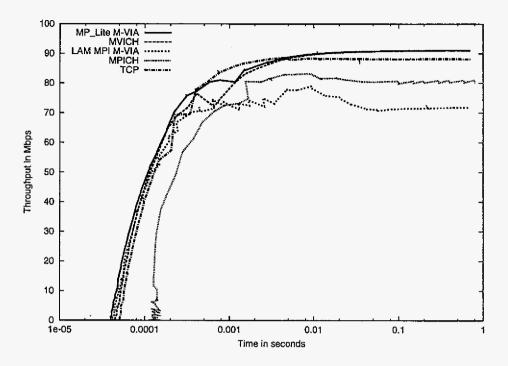

|       | 4.2.1           | Fast Ethernet on the PC Cluster           | 47 |  |  |

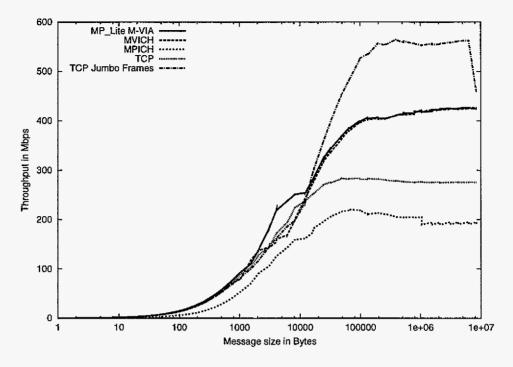

|       | 4.2.2           | Gigabit Ethernet on the PC Cluster        | 49 |  |  |

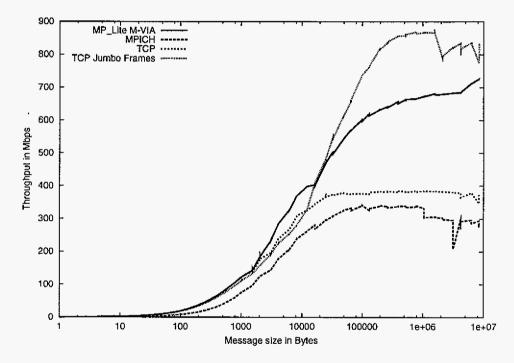

|       | 4.2.3           | Gigabit Ethernet on the Alpha Cluster     | 51 |  |  |

| 4.3   | Chanr           | nel-Bonding on Linux Clusters             | 52 |  |  |

| 4.4   | Summ            | nary                                      | 53 |  |  |

| CHAP  | TER :           | 5. DISCUSSION AND CONCLUSIONS             | 55 |  |  |

| 5.1   | Featur          | res                                       | 55 |  |  |

|       | 5.1.1           | High Performance                          | 55 |  |  |

|       | 5.1.2           | Channel-Bonding                           | 56 |  |  |

|       | 5.1.3           | Portability                               | 56 |  |  |

|       | 5.1.4           | User Friendly System                      | 57 |  |  |

| 5.2   | Limita          | ations                                    | 57 |  |  |

|       | 5.2.1           | Reliability                               | 57 |  |  |

|       | 5.2.2           | Resource Reservation                      | 59 |  |  |

|       | 5.2.3           | Channel-Bonding Issues                    | 60 |  |  |

|       | 5.2.4           | Overlapping Communication and Computation | 60 |  |  |

|       | 5.2.5           | Other Issues                              | 61 |  |  |

| 5.3   | Conclu          | usions and Future Efforts                 | 62 |  |  |

| BIBLI | BIBLIOGRAPHY 65 |                                           |    |  |  |

# LIST OF TABLES

| Table 3.1 | Memory copy compared to memory registration | 36 |

|-----------|---------------------------------------------|----|

| Table 4.1 | Test cluster configuration                  | 46 |

| Table 4.2 | Installed M-VIA implementation for MPI      | 46 |

| Table 5.1 | Reliability guarantees                      | 58 |

# LIST OF FIGURES

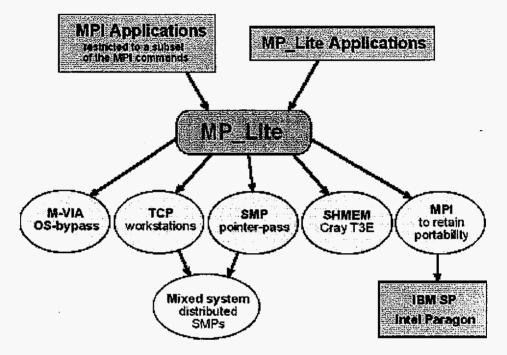

| Figure 2.1 | Diagram of the structure of MP_Lite                                         | 13 |

|------------|-----------------------------------------------------------------------------|----|

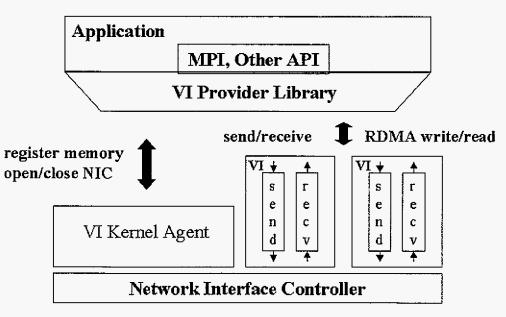

| Figure 2.2 | VI architecture model                                                       | 19 |

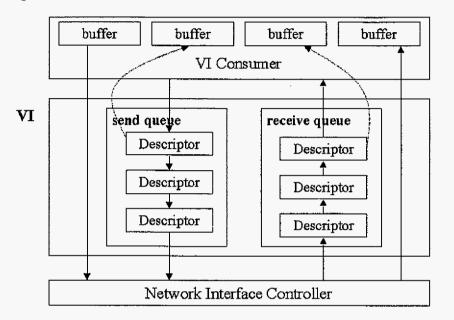

| Figure 2.3 | A Virtual Interface                                                         | 20 |

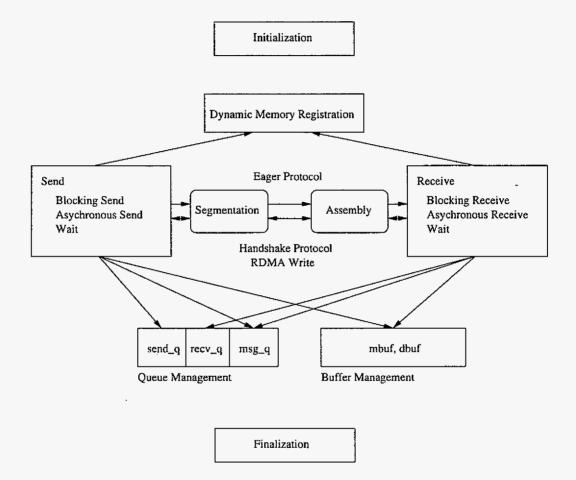

| Figure 3.1 | MP_Lite M-VIA module overview                                               | 27 |

| Figure 3.2 | An example of the receive queue                                             | 29 |

| Figure 3.3 | mbufs                                                                       | 30 |

| Figure 3.4 | Diagram of the eager protocol                                               | 35 |

| Figure 3.5 | Diagram of the handshake protocol                                           | 37 |

| Figure 3.6 | Channel-bonding for small messages                                          | 43 |

| Figure 3.7 | Channel-bonding for large messages sent by the RDMA Write $\ldots$ .        | 43 |

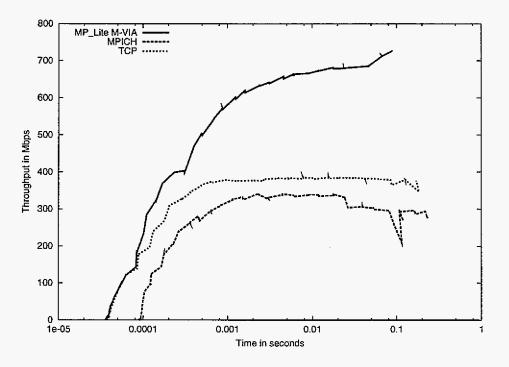

| Figure 4.1 | The throughput between Tulip Fast Ethernet cards on two PCs $\ldots$        | 48 |

| Figure 4.2 | The communication latency between Fast Ethernet cards                       | 49 |

| Figure 4.3 | The throughput between Syskonnect Gigabit Ethernet cards on the PC          |    |

|            | test cluster                                                                | 50 |

| Figure 4.4 | The throughput as a function of message size on the Alpha cluster $\ . \ .$ | 51 |

| Figure 4.5 | The signature graph on the Alpha cluster                                    | 52 |

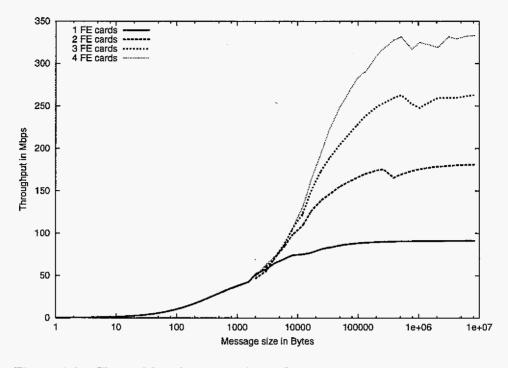

| Figure 4.6 | Channel-bonding up to four 3Com Fast Ethernet cards between PCs .           | 53 |

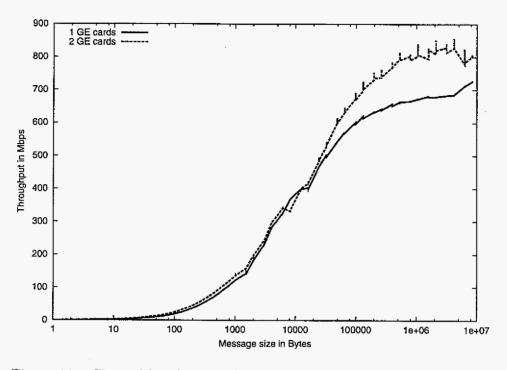

| Figure 4.7 | Channel-bonding two Gigabit Ethernet cards on the Alpha cluster             | 54 |

vii

.

# ACKNOWLEDGMENTS

I am grateful to many people who helped me in my research and the writing of this thesis. Thanks to my advisors Dr. Ricky A. Kendall and Dr. David E. Turner for their guidance, patience, mentoring, and support during my research work at the Scalable Computing Laboratory and the preparation of this thesis. My committee members Dr. Srinivas Aluru, Dr. Lu Ruan and Dr. Don E. Heller also gave me much help and advice.

Thanks to Mike Welcome and Paul Hargrove of NERSC for several helpful conversations about the M-VIA and MVICH projects. I would also like to give my special thanks to SCL secretary Vicki O'Neal for correcting grammar errors in this thesis.

This work was performed at Ames Laboratory under contract NO. W-7405-Eng-82 with the U.S. Department of Energy. The United States government has assigned the DOE report number IS-T 2030 to this thesis.

viii

ix

# ABSTRACT

MP\_Lite is a light weight message-passing library designed to deliver the maximum performance to applications in a portable and user friendly manner. The Virtual Interface (VI) architecture is a user-level communication protocol that bypasses the operating system to provide much better performance than traditional network architectures. By combining the high efficiency of MP\_Lite and high performance of the VI architecture, we are able to implement a high performance message-passing library that has much lower latency and better throughput.

The design and implementation of MP\_Lite for M-VIA, which is a modular implementation of the VI architecture on Linux, is discussed in this thesis. By using the eager protocol for sending short messages, MP\_Lite M-VIA has much lower latency on both Fast Ethernet and Gigabit Ethernet. The handshake protocol and RDMA mechanism provides double the throughput that MPICH can deliver for long messages. MP\_Lite M-VIA also has the ability to channel-bonding multiple network interface cards to increase the potential bandwidth between nodes. Using multiple Fast Ethernet cards can double or even triple the maximum throughput without increasing the cost of a PC cluster greatly.

# CHAPTER 1. INTRODUCTION

#### 1.1 Parallel Computing

The need for more computational power is the main driving force in the development of computers. Scientific and engineering problems require extremely fast computers to simulate physical phenomena. Some typical examples include weather prediction, the atomic structure of materials, the evolution of galaxies and the behavior of microscopic electronic devices (CS99). To satisfy the computation need, one approach is to build a more powerful processor and use a huge amount of memory. However, a single processor in many cases still cannot meet the computational demand. For example, it will take 13 hours to predict the earth's weather for the next two days by using a computer that can execute one trillion (10<sup>12</sup>) calculations per second (Pac97). Moreover, the speed of light is an intrinsic limitation to the speed of computers (Dem95). Instead of using a more powerful single processor, another solution is parallel computing: use multiple-cooperating processors to solve large problems.

There are two broad classes of parallelism: SIMD (Single Instruction Multiple Data) and MIMD (Multiple Instruction Multiple Data). SIMD systems perform the same operation on different data concurrently. Vector machines, such as Cray T-90, and systems like the CM2 are examples of the SIMD architectures. MIMD systems perform different operations on different data concurrently. MIMD architectures have two basic types: shared-memory or distributedmemory.

Shared-memory MIMD architectures consist of a collection of processors and memory modules that share the same memory bus. Each processor can access any memory module directly. Although the memory access is faster than distributed memory computers, shared-memory systems have specific problems such as memory consistency. Examples of shared-memory

1

architectures include the SGI Origin systems, IBM 43p/44p and Compaq ES40/DS20.

In distributed-memory MIMD systems, each processor has its own private memory. Access to other processors and memory is via the network. There are many network interconnect topologies such as 2D and 3D meshes, fat trees, and flat networks. Examples of distributedmemory architectures include the Cray T3E, Intel Paragon and IBM SP-2.

Distributed-memory MIMD systems can also be built using a group of PCs or workstations. Such systems are referred to as clusters. A cluster is a collection of independent computer systems tightly-coupled by a dedicated network to form a multiprocessor computing environment. Building a cluster is very economical and can have significant computational power, but the network can limit the kind of applications that will run effectively on it.

# 1.2 Communication in Parallel Computers

Shared-memory computers typically use compiler directives that control concurrency and access to data or use a native shared-memory library for inter-process communication. Distributedmemory computers use a message-passing paradigm. Parallel computer vendors usually have their own message-passing libraries optimized for their particular machines. There are also many free distributions suitable for a variety of architectures. Among those implementations, MPICH (GLnDS96) and LAM MPI (BDV94) are the two most commonly used message-passing libraries that conform to the message passing interface (MPI) standard(For94).

The basic operations of message-passing are the *send* and *receive* functions. The simplest model to measure the communication cost for sending a message is: *communication time* = latency + message size / bandwidth. The communication time can make a big difference in the performance of a parallel application. Therefore, it is always desirable to improve the performance of the underlying message-passing library and the network protocol. The performance of a message-passing library or a network protocol is usually measured by three factors:

1. Latency: The preparation time for sending a message, or the time to send a smallest useful message. It can be roughly measured by sending and receiving a 1 byte message

2

to another node and dividing the round-trip time by 2. Latency has a significant impact on applicatons that pass small to moderately sized messages.

- 2. Bandwidth: The measurement of the communication rate. It tells us the maximum number of bits or bytes that can be transfered per second.

- 3. Host processing cost: The CPU cycles consumed for communication.

From a software perspective, the performance of a message-passing library can be improved in two ways: improve the performance of the message-passing layer or improve the underlying network protocol.

The implementation of traditional network protocols, such as TCP, suffers a performance penalty because of the operating system processing overhead and the extra memory-to-memory copies between kernel space and user space. Many research efforts have designed user-level protocols that bypass the operating system to deliver higher performance (vECgS92; vEBBV95; PKC97; DBL<sup>+</sup>97; PT98; fIT00; CCC97). The Virtual Interface Architecture (CCC97) is one such protocol that defines an interface between high performance network hardware and computer systems.

The message-passing layer can also be improved. For portability issues, many messagepassing implementations complicate the internal queuing structure and require extra buffering for normal operations. Therefore, they do not match the performance of the underlying network protocol. MP\_Lite (Tur) is a light weight message-passing library designed to streamline the flow of data and deliver the maximum performance to the application.

# 1.3 The Goal of This Thesis

It is clear that if we can integrate the advantages of a light-weight message-passing library and OS-bypass network protocols, we can implement a message-passing library that has better performance. In this thesis, we will discuss the design and implementation of the MP\_Lite message-passing library on top of M-VIA, which is a modular implementation of the VI architecture for Linux. The goal is to combine the high efficiency of MP\_Lite with the high performance of M-VIA, and exploit the potential of the VI architecture to provide a low latency and high bandwidth message-passing library for applications. MP\_Lite M-VIA uses two different communication modes to achieve low latency for short messages and high bandwidth for long messages. Also, MP\_Lite M-VIA is the first to implement channel-bonding mechanisms on M-VIA, which provide double or triple the maximum throughput by using two or three Fast Ethernet cards in each machine in a cluster computer.

#### 1.4 Organization

In chapter 2, a brief introduction to the message-passing paradigm and its implementations will be presented. We will also investigate some user-level communication protocols. The emphasis is on the MP\_Lite message-passing library and the Virtual Interface Architecture. Chapter 3 will discuss the design and implementation details of MP\_Lite for M-VIA. The experimental results, compared to MPICH, MVICH and TCP will be presented in chapter 4. The discussion of the limitations of MP\_Lite M-VIA, as well as a summary and discussion of future efforts, will be presented in chapter 5.

#### 1.5 Other Research Efforts

In addition to the thesis work described here, a generic floating-point data compression library was also designed and implemented as the partial fulfillment of the requirement for the degree. The goals of my effort on this project were to develop the initial prototype for the compression library and fine tune the algorithms for the arbitrary precision routines.

Data compression is an effective way to increase the data transfer bandwidth or storage capacity in high performance computing. In the compression library, we only deal with scientific data: integer and floating-point numbers, single and double precision. The goals of the compression library include (CKS<sup>+</sup>00):

- A fast, robust library for application use.

- Utilize determinable and limited amount of resources.

4

- Run-time resource configuration.

- Operate on local data structure or distributed data structure (via Global Arrays).

- Portability by avoiding assembly level code.

The compression library is still under development. Currently it provides interfaces to compress and uncompress double precision data using different algorithms and contains several utility functions.

Given an uncompressed buffer, the size of the compressed buffer is dynamically determined and allocated and the handle of the compressed buffer is returned to the user. The handle contains the address of the compressed buffer as well as the header information. The compression algorithms currently implemented are:

- Double precision to single precision.

- Double precision to arbitrary precision.

- Skip lists.

- Double precision to arbitrary precision then using skip list mechanism.

IEEE standard 754 specifies that a double precision number contains one *sign* bit, 11 *exponent* bits, and 52 *mantissa* bits. The exponent has a bias of 1023, thus an exponent of zero means that 1023 is stored in the exponent field. In the algorithm of double precision to arbitrary precision, the user specifies how many exponent and mantissa bits are needed and the algorithm adjusts the numerical representation accordingly. The algorithm must deal with several aspects of compressing the numerical representation of a double precision number:

1. If the number of exponent bits the user specified is not enough to represent the data, the algorithm will automatically increase the number of bits to that required. There is a compression option that can let the algorithm automatically determine how many exponent bits are needed to represent the maximum (or minimum) number in the user data.

$\mathbf{5}$

- Some representations are reserved for special values. For example, infinity is represented with an exponent of all ones and a mantissa of all zero. These values should be handled differently.

- Big endian and little endian have different representations of a floating-point number.

So the endian information should be stored in the compression header.

The skip list algorithm represents a number in two components: data value and data index. It eliminates the need to represent a zero value therefore it is usefully for any sparse array or matrix. A variation of the skip list is to count the number of continuously repeated values. One of the requirement of the compression library is that user can modify the compressed data without uncompressing the entire buffer. For a skip list compressed buffer, the modification may lead to size change of the buffer. So an extra buffer is provided in skip list compressed buffer to store small changes. If too many changes are made and lead to the overflow of extra buffer, the current implementation must uncompress and re-compress the entire buffer.

Some application level functions are provided to operate on the compressed buffer: get or put a portion of successive data, gather or scatter data according to an index map, and accumulate data.

# CHAPTER 2. COMMUNICATION WITHIN A CLUSTER

Shared-memory multi-processor machines usually use shared-memory for inter-process communication. For distributed systems, especially in clusters, message-passing is a more common approach. The two most commonly used message-passing standards are PVM (Parallel Virtual Machine) and MPI (Message Passing Interface). MPI does not support some features of PVM such as dynamic process spawning, but it has more flexible collective functions (gather/scatter) and asynchronous send and receive communication capabilities. Some commonly used messagepassing libraries are investigated in this chapter. The MP\_Lite message-passing library will be discussed in more detail.

Message-passing libraries are implemented on top of an underlying network protocol. Compared to traditional network protocols, a user-level protocol allows the user to bypass the operating system and access the network device directly, thus providing low latency and better performance. We will investigate several user-level protocols and focus on the Virtual Interface Architecture.

## 2.1 Parallel Virtual Machine

PVM (PVM; Sun90) is one of many message-passing systems that preceded the formation of the MPI standard. It is an integrated set of software packages that allows a heterogeneous collection of computers to be used as a single parallel computer. PVM provides a general programming interface for algorithms, and the underlying infrastructure permits the execution of applications in a virtual computing environment that supports multiple computation models, such as functional parallelism and data parallelism. It provides support for a variety of architectures. The processors involved can be scalar machines, multi-processor machines or

7

other special processors. The principles of PVM include:

- User-selected running host. The user selects a set of machines to run the application on and can exploit the capability of each specific machine.

- The basic unit of parallelism is a *task*. A task is often but not always a process in the operating system.

- Explicit message-passing model. Message-passing is accomplished by using explicit send and receive commands.

- Heterogeneity and multiprocessor environment support.

A typical execution of a PVM application is a set of one or more sequential programs containing embedded PVM function calls in either the C or FORTRAN language. Each application program or instance of the application corresponds to one task. The compiled and linked binary codes are placed in a location accessible from each machine involved. The user starts one task, which eventually invokes other tasks. Those active tasks exchange messages to complete local computations. The results in each node are finally combined.

# 2.2 Message Passing Interface

MPI (For95), which was first defined in 1992, is a widely accepted standard for writing message-passing programs on multiprocessor machines. The standard provides portability between various architectures and an easy-to-use, consistent interface for application development.

MPI is a library that can be called from C, C++ or FORTRAN programs. It is designed to allow efficient inter-processor communication, reduce memory-to-memory copies and allow the developer to overlap communication and computation. The semantics of the interface is architecture independence and language neutral. Therefore, MPI applications can be developed on and for many platforms and used in a heterogeneous environment. MPI provides reliable communication for the upper layer, so applications do not need to deal with communication failures. MPI guarantees thread-safety for multithreaded programming as well. MPI describes the syntax and semantics for point-to-point communications, collective communications, group, context and communicator management, process topologies, environment management and profiling interface.

In point-to-point communications, the messages are not *overtaking*. If two sends match one receive or one send matches two receives, the destination node will not receive the second message if the first one is pending. In a single-threaded program, the send and receive are also ordered. There are four communication modes for point-to-point communications:

- Standard mode: The blocking send and receive are standard mode communication. In this mode, a send can start whether or not a matching received has been posted and can complete before a matching receive is posted. It is up to the MPI implementation to decide whether outgoing message will be buffered and if the send operation should be blocked. The standard send mode is **non-local**: the completion of the send may depend on the matching receive.

- Buffered mode: This is similar to standard mode, but it is local. If a send operation is executed before a matching receive is posted, the outgoing message will be buffered to allow the send call to complete.

- Synchronous mode: A send can start whether or not a matching receive is posted, but will complete successful only when the matching receive is posted and has started receiving. This is a non-local function.

- **Ready mode:** A send may start only when the matching receive is posted. Otherwise an error is returned.

In addition to these blocking communication mechanisms, MPI defines non-blocking communication mechanisms. A non-blocking send initiates the data transfer and returns immediatedly. A wait function needs to be called to complete the operation. Non-blocking communication mechanisms can use all four communication modes described above.

Collective communications involve a group of processes. The collective operations provided by MPI include: barrier synchronization, broadcast, gather/scatter, global reduction operations such as sum, max and min and many other variations. Collective functions are typically built upon basic point-to-point communication primitives.

Since version 1.1 of the MPI standard, many efforts have been made to add new functionality. MPI 2.0 was introduced in 1997. Many new features were added such as dynamic process creation, one-side communication and parallel IO (For97).

There are many implementations of the MPI standard. Computer vendors usually have their own MPI implementation optimized for their specific architectures. There are also many implementations that are freely distributed and suitable for a variety of architectures. MPICH and LAM MPI are the two most commonly used implementations.

#### 2.2.1 MPICH

MPICH (GLnDS96) is a complete implementation of the standard. The initial implementation was available immediately when the MPI standard was released in 1994. The goal of the MPICH project is to provide a portable, robust and efficient MPI implementation and promote the adoption of the MPI standard. MPICH is essentially a base implementation for parallel computers. MPICH is suitable for a variety of architectures. It supports traditional distributed-memory parallel computers (Intel Paragon, IBM SP, NCube, Cray T3D). sharedmemory architectures (SGI Origin, IBM SMP, Compaq ES40) and clusters of workstations running Unix or Windows. MPICH is intended to exploit the capability of specific architectures to obtain high performance communications.

The key for performance and portability in MPICH is the Abstract Device Interface (ADI), which is architecture independent. All MPI functions are implemented using macros and functions that make up the ADI. The ADI layer provides basic send and receive functions and message management. It contains codes for message packetizing, attaching headers, buffer management, queue management and handling heterogeneous environments.

For each different architecture, the ADI is implemented by using an architecture specific low level *channel interface*. The channel interface implements three data transfer protocols: The eager protocol where data is sent to the destination immediately; the rendezvous protocol where data is sent to the destination only when a matching receive is posted; the get or put protocol where data is read or written directly. The simplicity of the channel interface, which can be as small as five functions, provides a quick way to port MPICH to new architectures.

#### 2.2.2 LAM MPI

LAM (Local Area Multicomputer) (BDV94) is a full implementation of MPI and is a programming environment for heterogeneous computers on a network. LAM provides enhanced monitoring and debugging tools, such as a snapshot of a process and message status, to facilitate the message-passing application development.

Each computer runs a LAM daemon, which consists of a nano-kernel and a dozen system processes. The nano-kernel schedules these internal processes and some external processes to provide a communication subsystem for message passing between other LAM daemons. The LAM buffer daemon collects incoming messages and stores outgoing messages for forwarding. LAM MPI has the capability of dynamic process spawning, in which a group of MPI processes can collectively create a new group of processes and a new communicator is established for communication.

#### 2.2.3 MP\_Lite

MP\_Lite (TCK01) is a light weight message-passing library designed to streamline the data flow and deliver the maximum performance to applications in a portable and user-friendly manner. The purpose of MP\_Lite is to minimize the overhead of the message-passing layer and deliver as much performance as possible to applications. A full implementation of the MPI standard requires complicated buffering and queue management to provide portability for various architectures and handle situations such as MPI\_ANY\_SOURCE in receive operations, out-of-order messages and byte mismatches between send and receive pairs. The extra buffering and memory copy overhead, as well as the complicated multi-layered programming structure, reduce the communication bandwidth and increase the latency.

MP Lite provides a subset of the most commonly used MPI functions, which are enough

for a large number of the parallel codes. The simplicity makes it easy to reduce extra buffering and programming overhead, and thus deliver the maximum performance from the underlying network layer to the application. It is an ideal research tool for studying the performance of message-passing. Below is a listing of MPI commands that MP\_Lite supports.

• Initialization and cleanup

MPI\_Init, MPI\_Comm\_size, MPI\_Comm\_rank, MPI\_Finalize.

• Send and receive functions

MPI\_Send, MPI\_Recv, MPI\_Sendrecv, MPI\_Bsend. MPI\_Isend, MPI\_IRecv, MPI\_Ssend, MPI\_Srecv, MPI\_Wait.

• Collective operations

MPI\_Allreduce, MPI\_Bcast, MPI\_Barrier.

• Timing functions

MP1\_Wtime.

• Cartesian coordinate functions

MPI\_Cart\_create, MPI\_Cart\_coords, MPI\_Cart\_rank, MPI\_Cart\_shift, MPI\_Cart\_get.

The MP Lite does not support groups, the use of communicators for creating subgroup and the abstraction of the data types in a heterogeneous environment. It is not appropriate for more complex codes using those features. Below is listing of what is not supported.

- Communicators other than Cartesian grid functions and MPI\_COMM\_WORLD.

- MPI\_File\_ and MPIO\_ functions.

- Many variations on the basic communication functions.

- Heterogeneous environments.

Figure 2.1 represents the organization of MP\_Lite. Applications can use the MP\_Lite syntax, which is simpler than standard MPI syntax, or choose to use standard MPI syntax. The MP\_Lite layer has support for all the implemented send/receive functions, collective functions, timing functions, IO functions and Cartesian functions. There are also functions for a variety of other ongoing areas of research.

Figure 2.1 Diagram of the structure of MP\_Lite

Each MP Lite module implements point-to-point communication functions for different architectures. For the TCP module, there are two modes: synchronous and asynchronous. Communication events within an SMP node can be through either TCP or through sharedmemory segments. There is also a module for using the Cray T3E SHMEM library that provides twice the performance of the Cray optimized MPI. In chapter 3 of this thesis, we present the work on the M-VIA module, which bypasses the operating system to provide lower latency and higher bandwidth.

The TCP synchronous module simply increases the TCP send and receive buffers. Because all the messages must be buffered at TCP layer, this is an efficient way to reduce extra buffering and memory-to-memory copies. Therefore, the TCP synchronous module provides the maximum performance to the application layer. However, it will lock up if the user puts more data than can fit into the enlarged TCP buffers. Setting TCP buffers to a large size can make it usable for many applications but requires large amounts of memory for this configuration.

In the TCP asynchronous mode, the send and receive functions initiate the data transfer but return before completion. Whenever the data is transfered out of the TCP buffer or more data arrives in the TCP receive buffer, a SIGIO signal is generated so that a signal handling routine can continue transfering the data. Asynchronous send and receive functions are nonblocking and are more robust than the synchronous mode. The MP\_Wait() function will buffer the send data when necessary, therefore it will never be blocked even if two nodes are both sending. This asynchronous mode provides good performance even when using the default TCP buffer size.

All modules of MP\_Lite implement the basic communication primitives and use the same type of message queues to manage the message buffering when needed, such as for out-of-order messages. They provide a consistent interface to the upper layer though the implementation details may differ.

#### 2.3 Other Message-Passing Libraries

In addition to the traditional two-side communication libraries, which require the cooperation of both the source and destination, there are one-sided communication libraries that can put or get messages without the explicit cooperation of the iteracting node. The version 2.0 of the MPI standard has some support for one-sided communication, but the typical example is the Cray T3E SHMEM library (SHM94).

There are also several high-level libraries that build upon or beyond traditional messagepassing libraries to provide a simple to use interface for applications. As an example, Global Arrays (NHL96) provides a distributed multi-dimensional array interface as well as one-sided communication mechanisms.

14

# 2.4 User-level Networking

All message-passing libraries are implemented on top of one or more underlying network protocols. The performance of the network protocol is critical to the performance of messagepassing libraries. Traditional network protocols such as TCP usually use kernel protocol stacks to handle data transfer and demultiplexing operations. This mechanism requires data being copied multiple times between user space and kernel space. For example, in Linux, to receive a packet, the data is moved from the I/O device to the kernel  $sk\_buff$  data structure, and then moved to the user buffers. The extra memory-to-memory copy as well as the operating system processing overhead increases the data transfer latency and decreases the bandwidth (CJRS89).

In order to improve the performance, it is desirable to move the network interface much closer to the application. A User-level Networking (ULN) protocol defines an interface between applications and underlying network devices. Applications can talk directly to the network interface controllers through a protected environment, thus reducing the operating system processing overhead and eliminating the extra memory copies. Examples of ULN are U-Net. Active Messages, Fast Messages, Virtual Memory-Mapped Communication, Basic Interface for Parallelism, Scheduled Transfer Protocol and the Virtual Interface Architecture.

#### 2.4.1 Active Messages

Active Messages (AM) (vECgS92) is an asynchronous communication mechanism intended to overlap communication and computation. The traditional send/receive model often uses blocking or a handshaking mechanism to implement the blocking communications, and a buffering mechanism to implement the non-blocking asynchronous communication mode. Thus the effectiveness of an application using the message-passing library is degraded under the traditional send/receive model due to poor overlap of communication and computation. In Active Messages, each message contains as its header the address of a user-level handler which is executed on message arrival at the destination side. The handler is executed to extract the message body from the network, which is viewed as a pipeline. The sender launches the message into the network and continues computing; the receiver is notified or interrupted on the message arrival and runs the handler to receive the message body. The Active Messages differ from the Remote Procedure Call (RPC) in that the handler executed on the message arrival is to extract the message body from the network instead of performing computation. Buffering is not needed for Active Messages.

#### 2.4.2 U-Net

The User-Level Network Interface (U-Net) (vEBBV95) communication architecture provides processes with a virtual view of a network interface to enable user-level access to highspeed communication devices. It focuses on reducing the processing overhead to provide lowlatency communication and exploit the full network bandwidth even for small messages. It is an architecture designed to support traditional network protocols such as TCP/IP, as well as newer networking abstractions such as Active Messages.

The U-Net architecture consists of three parts: the *end-point* represents a handler to the network, the *communication segments* hold the communication data and the *message queues* hold descriptors for incoming or outgoing messages. To send a message, the send descriptor is pushed to the send queue and then the network interface will complete the descriptor. Incoming messages are demultiplexed into the appropriate destination based on message tags. The U-Net architecture specifies two levels of communication: a *base-level* which requires an intermediate memory copy at both the source and destination, and a *direct-access* mode which supports true zero-copy data transfers.

#### 2.4.3 Fast Messages

Fast Messages (FM) (PKC97) is a low-level messaging layer similar to Active Messages, but expands Active Messages by imposing stronger reliability guarantees. It uses essentially the same API as Active Messages and has the same concept of message handlers, but provides a guarantee for reliable delivery, ordered delivery and control over the scheduling of the communication work (decoupling), which is a mechanism to allow programs to control their cache performance. This allows the higher message layers the ability to avoid flow control, retransmission and other reliability issues.

#### 2.4.4 Virtual Memory-Mapped Communication

Virtual Memory-Mapped Communication (VMMC) (DBL+97) is a communication model providing direct data transfer between the virtual address space of the sender and receiver. The receiver *exports* the destination memory region, and the sending process *imports* remote buffers. VMMC protects the memory access by restricting the exporting and importing of the buffers. After a successful import, the sender can transfer data from its virtual address space into the imported destination buffer. This is accomplished by using a Remote Direct Memory Access (RDMA) mechanism.

#### 2.4.5 Basic Interface for Parallelism

The Basic Interface for Parallelism (BIP) (PT98) is a small API implemented on Myrinet network hardware. It implements all communication in a user layer library and gives the user direct access to the hardware. Memory copies are minimized during data transfer. Short messages are stored in an circular queue, so that send calls will not block even if no matching receive has been posted. Sending a long message requires a receive to be posted before or no longer than 50ms after the send.

#### 2.4.6 Scheduled Transfer Protocol

The Scheduled Transfer Protocol (STP) (fIT00; SGI) is an ANSI specified connectionoriented data transfer protocol. The protocol supports flow-controlled *Read* and *Write* sequences and non-flow-controlled, persistent-memory *Put*, *Get* and *FetchOp* sequences. The objective of STP is to provide high-bandwidth data transfer with minimal host CPU usage for long messages, and very low latency for short messages. STP has been implemented on Gigabyte System Network (GSN) and Gigabit Ethernet for Irix 6.5. The implementation on Linux is under development. The STP flow-controlled *Read* and *Write* sequences are designed to increase the bandwidth of the long message transfer. A small control message is used to pre-allocate buffers on the destination node, and the user buffers are mapped into the network interface's address space. Therefore, data can be transfered directly from the source user buffers to the destination user buffers using a RDMA mechanism to achieve potentially true zero-copy data transfer.

The non-flow-controlled Get/Put/FetchOp sequences are designed for short messages where low latency is the key. These sequences rely on more persistent memory mapping of the data buffers. The data buffers, once mapped through the kernel, are subsequently used and re-used to send/receive multiple blocks of data several times, thus resulting in very low latencies.

STP provides the basic transport layer infrastructure that can be used to implement multiple Upper Layer Protocols (ULP). Currently the only ULP implemented for Linux is the INET sockets API, AF\_INET sockets of type SOCK\_SEQPACKET using the protocol family IPPROTO\_STP. STP can use hardware acceleration, or use full software support. The current Linux implementation includes a full software support module and the enhancements to Gigabit Ethernet drivers with the Alteon firmware.

The current Linux implementation consists of a complete STP stack for long message transfers through the socket API. However, it does not support reliable data delivery, and is still in a very unstable beta stage. There is also an OS-bypass library (libST) for short message transfers, but it does not work because the receive ring in the device driver has not been implemented and the send sequences can only send header information. Therefore, we have not implemented MP\_Lite for STP.

#### 2.4.7 Virtual Interface Architecture

Virtual Interface Architecture (VIA) (CCC97; DRM<sup>+</sup>98), which is a standard proposed by Compaq, Intel and Microsoft, is an architecture for the interface between high performance network hardware and computer systems. The VIA is designed to enable applications to communicate over a System Area Network (SAN). A SAN is a type of network that provides high bandwidth, low latency communication, and has very low error rates. Very similar to U-Net, VIA defines a set of functions, data structures, and associated semantics, and provides direct access to the network interface for moving data directly into and out of process memory without additional copies of data and bypassing the operating system in a fully protected manner.

The VIA model consists of several components, as illustrated in Figure 2.2. The application and VI user agent form the **VI consumer** part of VIA. The VI user agent, typically the VI Provider Library, is an API for the application to access the kernel agent and the virtual interfaces. The kernel agent, which is a privileged part of the operating system and usually a device driver, performs operations such as memory registration, and opening/closing network interfaces. The data transfer is through Virtual Interfaces. A network interface controller (NIC) can be associated with multiple Virtual Interfaces. Each VI represents an end-point of a connection. The kernel agent, Network Interface Controllers and Virtual Interfaces form the **VI provider** part of the architecture.

Figure 2.2 VI architecture model

A VI consists of a pair of work queues: a send queue and a receive queue. The VI consumer performs the send and receive operations by posting descriptors to the send queue and receive queue. A descriptor is a data structure that contains all the information that the VI provider needs to process the requests, such as pointers to data buffers. Each queue is associated with a doorbell. Whenever a new descriptor is posted to the queue, the doorbell is used to notify the underlying NIC. The status information is returned from NIC to the VI consumer. Figure 2.3 shows a diagram of a Virtual Interface.

Figure 2.3 A Virtual Interface

Each work queue in the VI can associate with a completion queue. The notification of the completed descriptor in the work queue can be directed to the completion queue. A completion queue allows a VI consume to coalesce notification of descriptor completions from the work queues of multiple VIs in a single location. There are four methods to check the status of a descriptor:

- Poll the send or receive queue.

- Wait on the send or receive queue.

- Poll the completion queue.

- Wait on the completion queue.

The polling method provides the minimum latency but requires more CPU cycles. The VI

specification recommends using completion queues. Waiting on the completion queue is more efficient.

The VI architecture requires that user buffers be registered before they are used. The registration of a buffer locks the buffer memory pages into physical memory and translates the virtual address to a physical address. This memory registration process allows the VI consumer to reuse the registered buffers. The VI provider can transfer data directly between buffers of VI consumers and the network interface controller without additional buffering.

There are two data transfer models in VI: the send/receive model and RDMA model. In the send/receive model, descriptors are posted to the send queue and receive queue. Data is transfered from the buffers specified by the send descriptors to the buffers specified by the receive descriptors. Send descriptors and receive descriptors keep a strict one-to-one mapping and are queued and dequeued in FIFO order. The VI consumer is responsibile for the management of flow control, so the receive side must pre-post at least one descriptor of sufficient buffer size before the data arrives.

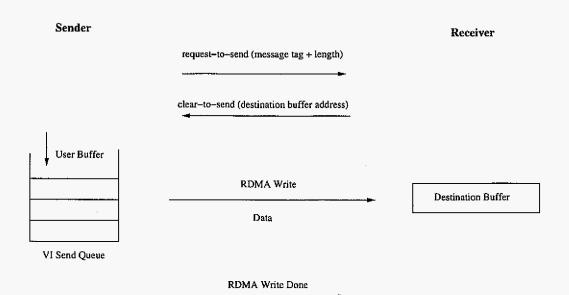

In the RDMA model, the initiator of the data transfer specifies the address of both the source buffer and the destination buffer. There are two types of RDMA operations: the RDMA Write and RDMA Read. In an RDMA Write, the data is transfered from the local buffer to the remote buffer. In an RDMA Read, the data is transfered from the remote buffer to the local buffer. Prior to the data transfer, the remote VI informs the local VI of the address and the registered memory handle of the remote buffer. The RDMA mode does not consume any descriptors in the remote VI queues, and no notification is given to the remote VI unless the *Immediate Data* field is specified in the local descriptor. The support for RDMA Write is mandatory, while the support for RDMA Read is optional.

The VI architecture supports three reliability levels: unreliable delivery, reliable delivery and reliable reception. All VI NICs are required to support Unreliable Delivery. Other levels are highly recommended but not required. The detailed information about reliability is discussed in chapter 5.

The VI architecture and the Scheduled Transfer Protocol are very similar. They both

provide RDMA mechanisms to increase the bandwidth of long message transfers and use preregistered buffers for short messages to reduce latency. In STP, the sending of control messages to pre-allocate buffers at the destination is automatically handled by the protocol, but in VIA, the handshaking and the flow-control must be handled by the VI consumer.

#### 2.5 VIA Implementations

#### 2.5.1 M-VIA

M-VIA (BS99) is a modular implementation of the VIA for Linux being developed by National Energy Research Scientific Computing Center (NERSC) at Lawrence Berkeley National Laboratory. The modular implementation allows it to support many types of network interfaces, and provides a portable and robust interface conforming to the VIA standard. M-VIA consists of a *user provider library*, a loadable kernel agent module and several modified device drivers. It can operate in either hardware acceleration mode or full software mode. It supports hardware VIA "doorbell" or software "doorbell" modes with a fast trap (a trap to a privileged mode that does not incur the overhead of a system call) for legacy hardware.

M-VIA is a full featured implementation of the VIA. The M-VIA kernel module is divided into several independent components including connection management, protection tag management, registered memory management, completion queue management, error queue management and the requisite Linux kernel extensions. The modular design makes it easy to be integrated into current Linux systems, for either the 2.2 or 2.4 kernels of Linux. The hardware support includes: Loop-back driver, DEC tulip Fast Ethernet cards, Intel Pro/100 Fast Ethernet cards, 3Com "Boomerang" Fast Ethernet cards, PacketEngines GNIC-I Yellowfin Gigabit Ethernet cards, PacketEngines GNIC-II Hamachi Gigabit Ethernet cards, Syskonnect SK-98XX Gigabit Ethernet cards and Intel Pro/1000 Gigabit Ethernet cards.

The current release does not have full support for reliable reception. Version 1.2b2 supports reliable delivery, which is very close to the reliable reception level. The latter is required to provide a full robust message-passing library for scientific applications.

The design of M-VIA 2 has been initiated. M-VIA 2 will redesign the internal structure to

provide better support for VI-aware hardware.

#### 2.5.2 The Berkeley VIA Implementation

The Berkeley VIA implementation (BGC98) is a prototype implementation on Sun Solaris, Windows NT and PC Linux over Myrinet. It follows the suggested reference implementation contained in the appendices of the VIA specification. One design choice was to keep as little information in the NIC's memory as possible. The VI creation and connection are protected by mapping a queue for protected commands into the kernel driver's memory so only the kernel driver can perform those operations. Doorbells are implemented as a single memory location on the NIC and polled by the firmware.

The Berkeley VIA implementation only supports a subset of VIA rather than the entire standard. It does not implement the scatter/gather capability, reliability modes, error and completion queues and the RDMA facilities.

#### 2.5.3 Commercial Products

Many vendors provide VI-aware hardware and corresponding VIA implementations. They are: Giganet (Emulex) - cLan, Finisar - Fibre Channel VI Host Bus Adapter, Tandem -ServerNet II. Fujitsu System Technologies - Synfinity CLUSTER, and NEC - V1000 NIC.

## 2.6 VIA Implementations for MPI

#### 2.6.1 MVICH

MVICH (Cen) is an MPICH-based implementation of MPI over VIA. It provides a high performance MPI for high speed networks such as Gigabit Ethernet, GigaNet, ServerNet II, or Fast Ethernet.

MVICH is a full implementation of the ADI2 for VIA, developed from scratch. It implements four protocols to maximize performance over a range of message sizes:

• For short messages, MVICH uses an eager protocol, in which data is sent and received through pre-posted buffers, with the source sending data immediately.

- For long messages, MVICH uses one of three protocols, depending on whether the underlying NICs support RDMA Write or Read.

- 1. The "r3" protocol is a standard rendezvous protocol in which data is sent only when the receiver has sent an *ok-to-send* message.

- 2. The "rput" protocol is an RDMA Write protocol. Data is sent after an *ok-to-send* is posted by the receiver. Memory on both the sender and receiver is dynamically registered so this protocol is zero-copy.

- 3. The "rget" protocol is an RDMA Read protocol similar to "rput".

MVICH is still under development. The current release is 1.0a6.1. Work is in progress to pass the full conformance and stress tests. We will compare the performance of MVICH with communication libraries in chapter 4.

#### 2.6.2 M-VIA for LAM MPI

The ParMa2 project has a basic M-VIA implementation for LAM MPI (BBCR: aUoP). It also utilizes the normal send/receive and RDMA mechanism to improve the performance. The basic communication functions supported include:

- Standard send, synchronous send, buffered send and ready send.

- Non-blocking primitives.

- Tag and communicator control on messages.

- MPLProbe and non-blocking MPLIProbe, used to read a matching envelope.

- Support for receive from any process: MPLANY\_SOURCE in receive functions.

This package also has a flow control functionality to avoid exhausting all communication resources including RDMA space and pre-posted descriptors. Packet fragmentation and reassembly are implemented due to the 32 KB limitation of the maximum packet size. The drawback of this implementation is that user buffers are not dynamically registered. Data is transfered between pre-registered send and receive buffers. Therefore, a memory copy is needed to copy data between the user buffer and the pre-registered buffer at both the source and destination. This greatly reduces the performance for large messages. Moreover, it is currently very unstable. One problem is that it is unable to send messages more than approximately 1600 times. Therefore, it is impossible to run a full NetPIPE (SMG97) benchmark test.

#### 2.6.3 VIA for MPI/PRO

MPI/Pro (DS98; DS99) is a commercial MPI implementation by MPI Software Technology Inc. MPI/Pro uses a progress thread in each of its VI and SMP communication devices for implementing an independent, non-polling message progression, thus MPI/Pro makes progress on all messages independent of the sequence of user calls. Similar to other implementations, two different protocols are used to handle short message send/receive and long message RDMA to achieve the required low latency and high bandwidth. Other features include multiple receive queues and optimized derived data types. Currently MPI/Pro VIA supports Giganet, ServerNet-II and FC-VI (Finisar). The support for Myrinet is in development.

#### 2.6.4 MPI Implementation on the NTSC VIA cluster

The National Center for Supercomputing Applications (NCSA) has implemented a Fast Messages layer on top of VIA for their large scale Windows NT Super Cluster (NTSC), so that MPI-FM, which is derived from MPICH that uses Fast Messages Interface, can run on top of VIA through the Fast Message layer (Pan).

#### 2.6.5 MP\_Lite M-VIA

In the next chapter, we will discuss the implementation of MP\_Lite on top of M-VIA. By combining the light weight, highly efficient MP\_Lite with high performance M-VIA, we will be able to deliver most of the available performance that the underlying hardware offers to the application layer.

# CHAPTER 3. IMPLEMENTATION OF MPLITE FOR M-VIA

Using M-VIA to implement message-passing libraries has several advantages. For slower networks such as Fast Ethernet, M-VIA provides much lower latency. For faster networks such as Gigabit Ethernet, M-VIA offers much higher throughput because memory-to-memory copies are minimized. M-VIA can use hardware acceleration to further improve the performance. By combining the light-weight MP\_Lite with M-VIA, we will be able to fully utilize the benefits of both in order to deliver low latency and high bandwidth communication to applications in a portable manner. The goals of this research project are:

- High performance (low latency, high throughput and low CPU load). The MP\_Lite M-VIA module will deliver almost all the performance that M-VIA can offer to the application layer in an optimal situation.

- Channel-bonding capability. MP\_Lite M-VIA will have the capability to use multiple network interface controllers simultaneously to improve potential bandwidth.

- Minimizing resource usage. MP\_Lite should minimize memory utilization and CPU workload. This is important for scalability.

- User friendly. Reduce M-VIA related configuration for MP\_Lite and provide the same interface and configuration mechanisms as other MP\_Lite modules.

# 3.1 System Overview

The MP\_Lite library already provides the high level functions that are independent of the underlying communication protocols. These include global reduction functions and gather/scatter functions. Therefore, what is required for a module is the implementation of the point-to-point

26

functions, buffer management, message management, queue control, data segmentation and assembly, as well as initialization and finalization procedures. The components of the system and their respective relationships are shown in Figure 3.1.

Figure 3.1 MP\_Lite M-VIA module overview

The initialization procedure checks input parameters, allocates memory and sets up connections. The point-to-point functions include blocking and non-blocking asynchronous send and receive commands using two different transmission protocols: the eager protocol and the handshake protocol. Dynamic memory registration is critical for the performance of long message transfers. Data segmentation and assembly is necessary during transmission because of the 32 KB limit of the maximum transfer unit in M-VIA. It is also imperative since we need to use multiple network interface controllers for channel-bonding. The important data structures in message queue management are the receive queue, send queue and message queue. Buffer management controls the memory resource usage. The finalization stage frees the allocated memory and shuts down related processes.

In the following section, the details of the module implementation of M-VIA for each of the sub-modules are delineated.

## 3.2 Queue Management

Queue management provides a mechanism to buffer and access outstanding messages. The *send* and *receive* queues are used to manage the asynchronous messages. The *message* queue is used to buffer incoming messages that do not have a matching receive. Messages are queued and dequeued in First In First Out (FIFO) order. The related data structures are:

- struct MP\_msg\_entry: The MP\_Lite message data structure which contains all the necessary information for a message, such as the message id, source, destination, buffer address, length, tag and segmentation information for channel-bonding.

- struct MP\_msg\_entry \*send\_q[]: Each node has a send queue for all other destination nodes. A message of destination dest is appended to the end of send\_q[dest]. The send function dequeues messages from the head of send\_q[dest] as it delivers the message to the destination node.

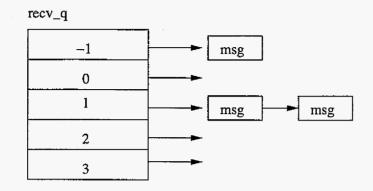

- struct MP\_msg\_entry \*recv\_q[]: Each node has a receive queue for each source nodes. Messages expected from source src are posted to the end of recv\_q[src]. When a message is coming from src, the recv\_q[src] is searched from the beginning for a match. recv\_q[-1] is reserved for messages whose source is a wildcard.

- struct MP\_msg\_entry \*msg\_q[]: The buffered message queue is for incoming messages that do not have a match in recv\_q. A message that is sent to itself is also posted to msg\_q.

The separation of queues by message destination or source speeds up the demultiplexing of incoming and outgoing messages which enhances the performance. An example of the recv\_q is shown in Figure 3.2

Figure 3.2 An example of the receive queue

Functions related to queue operation are:

- **post()**: Post a message to the send\_q, recv\_q or msg\_q

- send\_to\_q(): Send a message directly to msg\_q, which is used only when a node sends a message to itself.

- $recv_from_q()$ : Try to retrieve a message from the msg\_q. This is the first step to receive any message. When a match is found, the data is copied to the destination buffer and the message in msg\_q is dequeued and destroyed. A receive message matches if the tags of these two messages are the same or the tag of the receive message is a wildcard and the number of bytes is less than or equal to the expected length.

- find\_a\_posted\_receive(): Find a matching receive in recv\_q when a message is coming. If a match is found, the message is returned and dequeued from the recv\_q.

## 3.3 Buffer Management

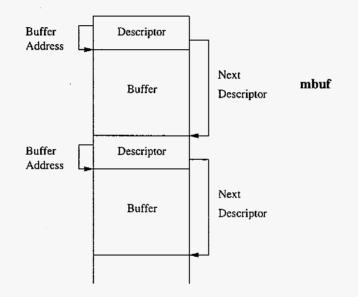

Sending and receiving is accomplished by posting descriptors, which describe the data address, length and registered memory handle. The short messages are copied to the preregistered buffers for sending (long messages use user buffers directly). Receive descriptors need to be pre-allocated before connection is setup in order to receive unexpected data before user buffers are available. Because limited memory resources, buffer management is needed to control the memory usage. In our implementation, we use the concept of *mbuf*, which is similar to the data structure used in many operating system memory management designs. A *mbuf* is a block of memory that contains both the buffer description (in our case, the VI descriptor) and the actual buffer space. An *mbuf* is linked as a queue. Functions are provided to queue and dequeue a block of *mbuf* from the head of the queue. An *mbufs* is allocated in a contiguous address space so that when it is registered, we get only one memory handle to make things easier. This is illustrated in Figure 3.3.

Figure 3.3 mbufs

In addition to *mbuf*, there is another type of buffer unit called *dbuf*. A block of *dbuf* only contains a VI descriptor and does not have its own buffer space. An *mbuf* is for sending and receiving small messages, which are always be buffered in *mbufs* before sending or receiving. A *dbuf* is for sending large messages. The buffer pointer will be redirected to the actual user buffer. The advantages of the separation of *mbuf* and *dbuf* are:

Because the size of *dbuf* is small, we can allocate a lot of *dbufs* for sending large messages without greatly increasing the system resource utilization. For example, we can allocate 300 *dbufs* (descriptors) for sending messages of up to 8 MB (each descriptor can point to a 32 KB block of user data). 2. We can increase the size of *mbuf* to improve the short message performance. Because an *mbuf* is only used for sending small messages, which do not require many descriptors, we can increase the size of an *mbuf* without greatly increasing the total system memory usage. For example, we can set the size of an *mbuf* to 16 KB, so that a message smaller than 16 KB can be sent in one descriptor.

In the MVICH implementation, there is only one type of buffer *vbuf*, which is similar to *mbuf*. An *vbuf* is used to send both small and large messages. To send a large message, lots of *vbufs* are needed. Because each *vbuf* has its own buffer space, to reduce resource usage, the *vbuf* size should be small. For example, set the *vbuf* size to 1 KB in MVICH. A message of size 5 KB needs to be send 5 times, which limits the MVICH performance.

Functions related to *mbuf* (*dbuf* is similar) are:

via\_desc\_request(): In response to the user buffer request, dequeue a block of mbuf from the mbuf list for usage.

via\_desc\_release(): When finished using an *mbuf*, queue the *mbuf* to make it available again.

via\_desc\_restore(): Restore the default value of the descriptor in an *mbuf*.

### 3.4 Important Data Structures

- struct via\_conn: This is the data structure represents the VIA connection. All the information of a VI connection, such as the VI handle, the connection handle and the remote address, is included in this data structure. Since the current M-VIA implementation does not provide fully reliable data transfer, a *sending sequence number* and an *expected receiving sequence number* are added to improve the error detection.

- Message headers: Message headers tell the destination what type of incoming message it is. They can be used to distinguish messages and selectively receive them. They are also called message envelopes. To reduce transfer overhead, we use variable size headers instead of a large fixed one to keep the header as small as possible. A few fields of the

beginning of these headers are identical, so they have a common small header for easy analysis. There are four types of headers used in different transmission modes:

- 1. OP\_SEND: Normal send by using the eager protocol. Data is accompanied with the header. The message length and tag are included in the header.

- 2. OP\_RDMAW\_RTS: RDMA Write *request-to-send*. Parameters include message length, tag and source message id.

- 3. OP\_RDMAW\_CTS: RDMA Write *clear-to-send*. Parameters include destination buffer length, tag, source message id, destination message id, and registered destination memory handle.

- 4. OP\_RDMAW\_DONE: This is used to notify the data destination that an RDMA Write operation is done. This header contains the message length, tag, destination message id and destination memory handle. This header can be eliminated if using the *ImmediateData* field of the descriptor to inform the completion of the RDMA opertion.

## 3.5 Initialization

Initialization is done in the MP\_Init() function. The library needs to read and analyze input arguments, determine the process id, initialize log and status files, allocate and create data structures and setup VI connections.

The run-time parameters are stored in a configuration file *.mplite.config* in the current working directory. The configuration file is created by the *mprun* startup script. The format of this file is:

```

<number of nodes>

<number of NICs>

<program name and arguments>

0 <node0 NICO>, <node0 NIC1>, ...

1 <node1 NICO>, <node1 NIC1>, ...

```

Each node started by *mprun* reads those parameters and begins to determine its own process id. The process id is an integer starting at zero and uniquely identifies each node. Because multiple nodes can run on the same machine (especially on an SMP machine), and they are basically identical, we need a mechanism to avoid contention in determining the process id. It would be easy if the *mprun* script could determine the process id when it launches each process, and then transfer this id as an input argument to each process. However, because Fortran support for command line arguments is limited, it is not easy to deliver the process id to the correct process if multiple identical processes are running on the same machine. So each process has to determine the id independently.

Our approach is to use System V shared memory to determine the unique process id. All the nodes on the same machine try to create a named shared memory region. The name of the shared memory region is unique to each *mprun* session. If the shared memory region already exists, then the processes try to attach to this memory region. The shared memory region contains an integer. The initial value of this integer is zero. Each process grabs the current value in the shared memory region and increments the value by one. Of course the shared memory needs to be locked using a semaphore to avoid contention from other processes accessing the same shared memory region. All the processes running on the same machine will get different values and can be ordered accordingly. Each process uses the grabbed value combined with the value read from the file *.mplite.config* to determining its unique process id. The last process closes the shared memory region.

After determining the unique process id, the next step is to determine the network devices to be used (the VIA device name), such as "/dev/via\_eth0" for the first NIC, "/dev/via\_eth1" for the second NIC, etc. The NIC name or IP address must be translated to the specific device name. In MVICH, the device name is fixed in the source code, so if you want to use another NIC on your machine instead of the default one, you have to recompile the MVICH package. The M-VIA implementation of LAM MPI uses a configuration file to store the VIA device

. . .

names, so you have to manually modify the configuration file if you want to use another  $NIC^{1}$ .

MP\_Lite can stripe data across multiple NICs simultaneously to increase the transmission bandwidth. The MP\_Lite implementation dynamically determines the device from the user provided NIC name at run-time. It works by getting the IP address of the specified NIC name, using the *ioctl()* function to get a list of all the network interfaces installed on the system and comparing the IP address with each of these interfaces. Dynamic configuration eliminates the need for special configuration options for the M-VIA module and keeps the arguments of *mprun* the same as for other modules.

The VI initialization procedure also allocates memory and creates data structures. This includes allocating all the message and queue structures, allocating and registering *mbufs* and *dbufs* (whose address must be properly aligned for performance), opening the VI devices and creating VIs.

The last step of the MP-Lite initialization stage is to set up a fully-connected network. Connections must be made between each pair of nodes. Each VI can only represent one connection, so we have to create nprocs - 1 VIs and make nprocs - 1 connections in each node for nprocs nodes. Each VI is given the local and remote address when created. The descriminator (similar to the port number in TCP, but not restricted to integers) of each VI is specified as a triplet {local node id, remote node id, NIC id}. Thus different VIs on the same node have different descriminators.

The connection sequence is determined by the process ids. Each node accepts a connection from nodes with a smaller id, then each node initiates connections to nodes with larger id values. To synchronize this procedure, every node will send a *go* signal to its upper neighbor and receive a *go* signal from its lower neighbor after all connections are generated.

#### 3.6 Communication Protocols

Two communication protocols have been implemented in the MP\_Lite M-VIA module: the **eager protocol** and the **handshake protocol**. The eager protocol is for short message, and

<sup>&</sup>lt;sup>1</sup>In fact, due to at least one bug, you can only use the first NIC unless you utilize some non-trivial hacks.

the handshake protocol is for long messages.

## 3.6.1 The Eager Protocol

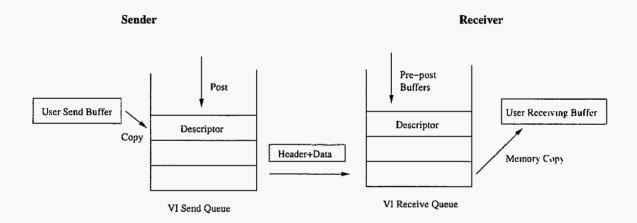

The eager protocol assumes the receive node has enough pre-posted buffers to hold the incoming messages. Once messages are posted for sending, messages accompanied with headers are sent to the destination node immediately. On the destination node, the arriving messages are stored in the pre-posted buffers and copied to the user buffers when a matching receive is posted. Because of limited buffer resources, this protocol is only suitable for small messages. The eager protocol is illustrated in figure 3.4.

Figure 3.4 Diagram of the eager protocol

The eager protocol can significantly reduce the communication latency since messages are sent without delay. However, it requires pre-posting enough buffers to hold the incoming data from arbitrary sources and at least one memory copy is needed at the destination node to copy data from the pre-posted buffers to the user buffers.

The MP\_Lite M-VIA implementation involves an additional memory copy at the source node, from the user buffers to the pre-registered *mbufs*. A procedure can be implemented that dynamically registers the user buffers and posts the user buffer directly to the VI send queue. However, for small messages, it takes more time to register/deregister buffers than to copy data to pre-registered buffers. Table 3.1 shows the time comparison of memory copy and registration/deregistration of different data sizes on an Intel PIII PC.

| Data size (bytes) | Memory copy $(\mu s)$ | <b>Registration</b> /deregistration ( $\mu s$ ) |

|-------------------|-----------------------|-------------------------------------------------|

| 8                 | 0                     | 4                                               |

| 64                | 0                     | 4                                               |

| 256               | 0                     | 4                                               |

| 2048              | 1                     | 4                                               |

| 4096              | 2                     | 5                                               |

| 8192              | 4                     | 6                                               |

| 16384             | 47                    | 8                                               |

| 32768             | 91                    | 12                                              |

| 65536             | 181                   | 21                                              |

Table 3.1 Memory copy compared to memory registration

The table shows that when the data size is less than 8 KB, the memory copy is faster than memory registration/deregistration. Therefore, for small messages, it is more efficient to use the memory copy. For large messages, we switch to the handshake protocol and use the RDMA Write to achieve high performance, zero-copy data transfer.

### 3.6.2 The Handshake Protocol