# The Lector CRAPAR

## BNL CRADA BNL-C-95-05

M. Atiya\*, D. Padrazo, Y. Zhao Brookhaven National Labortaory

R. Sumner, U. Untermeyer LeCroy Research Systems

B. Carlson, Z. Zheng State University of New York at Stony Brook

Development of a 10-bit 500 Msample/sec Waveform Digitizer

#### **Outline:**

- Overview & History

- Objectives

- Technical Progress

- Future Potential

<sup>\*</sup> Principal Investigator

#### **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, make any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

#### **DISCLAIMER**

Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.

## Waveform Digitizer: Overview

"An Oscilloscope on a chip" A simple, robust, low-cost device to sample fast analog signals and convert them into digital data.

The device is characterized by the following:

• Sampling rate.

The number of digital samples per second.

• Dynamic range/effective bits.

The number of bits per sample.

• Input bandwidth.

The speed of the signal that can be captured.

Note that a mathematical theorem limits the bandwidth to less than half the sampling speed.

• Depth of Memory.

The length of time samples can be stored prior to readout

• Readout speed.

The length of time for the acquisition of digitized samples into standardized format.

• Cost.

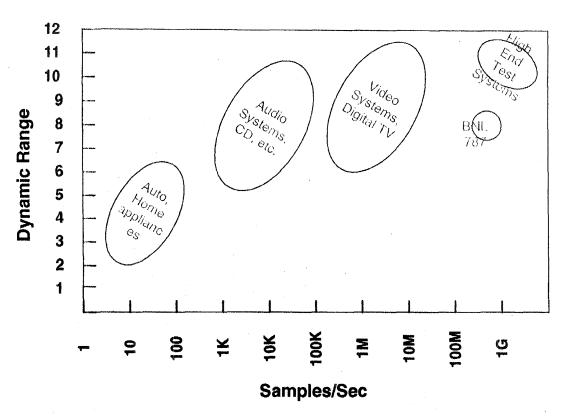

Figure 1 Performance of current Digital to Analog systems.

# **Funding**

#### DOE (BNL)

|          | 3/95-2/96    |                   | 3/96-2/97    |                   |

|----------|--------------|-------------------|--------------|-------------------|

|          | BNL<br>CRADA | BNL non-<br>CRADA | BNL<br>CRARA | BNL non-<br>CRADA |

| Manpower | 237,022      | 0                 | 248,873      | 0                 |

| Software | 26,074       | 0                 | 0            | 12,000            |

| Parts    | 8,148        | 0                 | 22,861       | 15,000            |

| Total    | 271,244      | 0                 | 271,734      | 27,000            |

#### Industry (LeCroy )

| ADC design    | 207,000 |   |

|---------------|---------|---|

| Memory design | 253,000 | · |

| System design | 21,000  |   |

| Total         | 481,000 |   |

## **Project Summary**

- Approved in late 1994, funded in March 1995.

- Goal is to utilize existing LeCroy Front End developments and BNL previous efforts to:

- Extend the dynamic range from 8 to 9-10 bits.

- Extend the depth of memory.

- Lower the cost.

- Increase availability to general research and industrial community.

| Subsystem                                                 | Responsibility    |

|-----------------------------------------------------------|-------------------|

| Analog Front End (S/H) IC                                 | LeCroy            |

| MFE415 & MSH417                                           | ·                 |

| ADC IC                                                    | LeCroy            |

| MAD422                                                    |                   |

| Memory IC                                                 | LeCroy            |

| MEM424                                                    |                   |

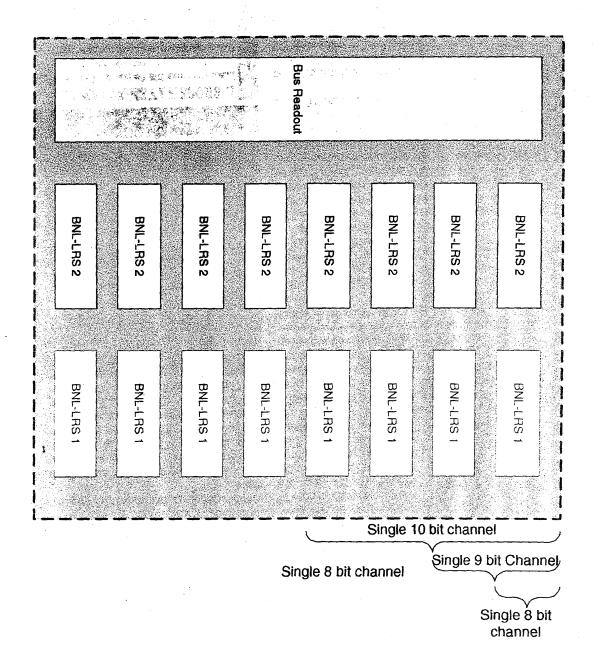

| Integration of front end and extension to 9-10 bits (MCM) | BNL (Stony Brook) |

| (BNL-LRS 1)                                               |                   |

| Fast readout controller                                   | BNL               |

| (BNL-LRS 2)                                               |                   |

| Bus interface logic                                       | BNL               |

|                                                           |                   |

| System Integration                                        | BNI.              |

## Why BNL, Stony Brook and LeCroy?

- Long standing interest in this area.

- Proven accomplishments.

- Matched an Non-overlapping skills.

#### Examples

- BNL-E787 produced one of the largest waveform digitizers in existence.

- 500 Msamples/sec at 8 bits dynamic range.

- 2-400 μsec memory.

- Fast readout (50 Mb/sec).

- Zero suppression at write time.

- 500 Channels.

- In operation since 1988.

- LeCroy is one of the largest producers of high performance test systems.

- Gsample/sec digital oscilloscopes.

- Innovative Front End IC design.

#### Benefits and relevance to DOE mission

- Advances in this area of instrumentation are of critical importance to many areas of applied and basic research.

- Detector instrumentation (the majority of US high energy physics research is funded by DOE).

- Accelerator instrumentation (All US accelerators are funded entirely by DOE).

- Test systems (relevant to DOE's mission in energy, environmental and health areas).

- Existing laboratory expertise and developments are made available to US industry.

- First generation of devices developed for specific research purposes with DOE's support in 1988.

- Leveraging of existing infrastructure allows for an efficient transfer to industry.

There is strong interest from both research and industrial community in this development.

Partial List of Expressed Interest (Customers?).

- High Energy/Nuclear Physics

- g-2 Experiment at BNL.

- Rare Kaon Experiments at BNL.

- RHIC Beam Instrumentation Group.

- Industry (ref. LeCroy)

At least one previous generation of E787 development has been licensed to outside industry (SandersAssoc, Lockheed Corp.).

## **Technical Progress**

- Sample & Hold, ADC, and Memory exist.

- Sample & Hold capable of providing over 7 effective bits at 150 MHz input bandwidth (2GHz analog bandwidth).

- ADC capable of 500 Msamples/sec and 8 bits of dynamic range.

- Memory capable of 256 Kbytes and 2 nsec write speed.

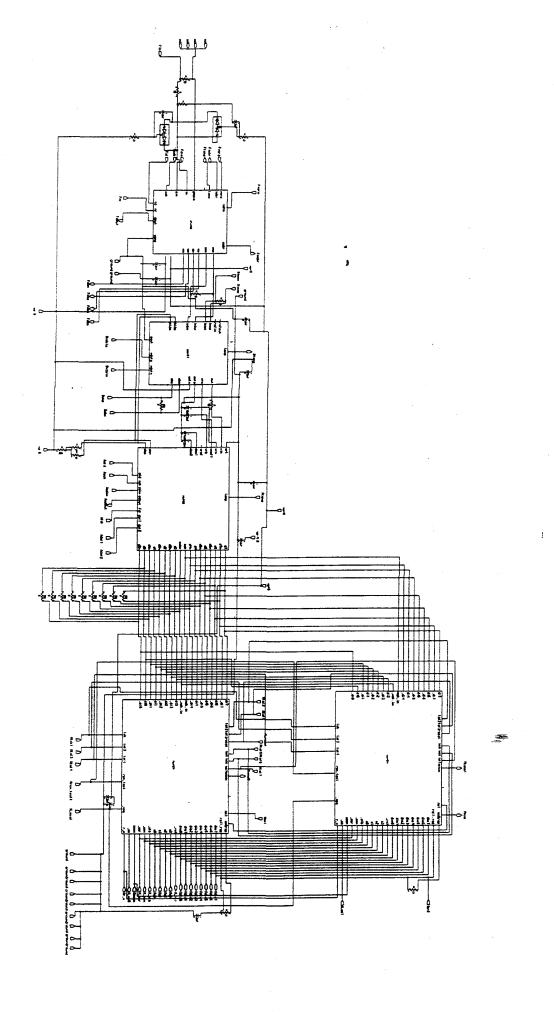

- Integration MCM module has been designed and is under fabrication.

- Use of a Multi-Chip Module (MCM) is essential to lower noise, increase packaging density and enhance reliability.

- MCM is a single deliverable component that can be used by others.

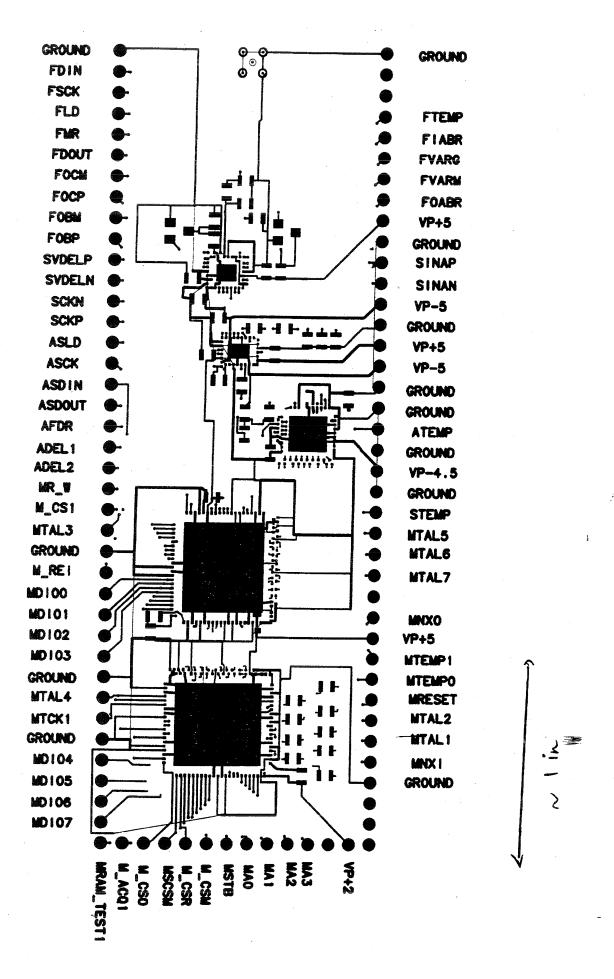

- Readout custom IC designed and tested.

- Fast readout with "on the fly" zero subtraction is essential to allow use of the device at high rates.

- Standardized output formats allow use in a wide variety of modules.

- Designed using VHDL to allow utilization of the latest technology without extensive redesign.

- Board level integration has started.

# Specification of Waveform Digitizer

8 Channels in a single module capable of operating as 8 8-bits, 4 9-bits or 2 10-bits ADC.

**Sampling Speed**

.

**Depth of Memory**

Input Bandwidth

**Readout Speed**

Zero suppression

Bus interface standard

Power

. .

**Software Support**

> 500 Msamples/sec

150-200 MHz

256 µsec

40 nsec per non-zero sample

At read, with pre and post sampling

CAMAC, Fastbus, VME

< 60 watt /module

Standard PC and UNIX readout codes