1.28 - 1 1.28 - 1 1.28 - 1

## SANDIA REPORT

SAND2000-2766 Unlimited Release Printed November 2000

# ow-Power Public Key Cryptography

Cheryl Beaver, Timothy Draelos, Victoria Hamilton, Richard Schroeppel, Rita Gonzales, Russell Miller, and Edward Thomas

Prepared by Sandia National Laboratories Albuquerque, New Mexico 87195

Albuquerque, New Mexico 87185 and Livermore, California 94550 Sandia is a multiprogram laboration

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy under Contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831

Telephone: (865)576-8401 Facsimile: (865)576-5728 E-Mail: reports@adonis.osti.gov Online ordering: http://www.doe.gov/bridge

Available to the public from U.S. Department of Commerce National Technical Information Service 5285 Port Royal Rd Springfield, VA 22161

Telephone: (800)553-6847 Facsimile: (703)605-6900 E-Mail: <u>orders@ntis.fedworld.gov</u> Online order: http://www.ntis.gov/ordering.htm

## DISCLAIMER

Portions of this document may be illegible in electronic image products. Images are produced from the best available original document. SAND2000-2766 Unlimited Release Printed November 2000 NOV 2 3 2000 OSTI

## Low-Power Public Key Cryptography

Cheryl Beaver, Timothy Draelos, Victoria Hamilton, and Richard Schroeppel Cryptography and Information Systems Surety Department

> Rita Gonzales and Russell Miller Digital Microelectronics Department

Edward Thomas Statistics & Human Factors Department

> Sandia National Laboratories P.O. Box 5800 Albuquerque, NM 87185-0449

#### Abstract

This report presents research on public key, digital signature algorithms for cryptographic authentication in low-powered, low-computation environments. We assessed algorithms for suitability based on their signature size, and computation and storage requirements. We evaluated a variety of general purpose and special purpose computing platforms to address issues such as memory, voltage requirements, and special functionality for low-powered applications. In addition, we examined custom design platforms. We found that a custom design offers the most flexibility and can be optimized for specific algorithms. Furthermore, the entire platform can exist on a single Application Specific Integrated Circuit (ASIC) or can be integrated with commercially available components to produce the desired computing platform.

3

Several digital signature algorithms are candidates for low-power usage, but some may have restrictions. We recommend an elliptic curve implementation of an El Gamal signature as a general solution. We used special elliptic curve and finite field operations to optimize the algorithm, and designed an implementation for an ASIC. The design is available to interested readers and is ready for easy integration into specific applications.

This page intentionally left blank.

## Contents

| 1. | Intro | oductio | n                                                             | 11 |

|----|-------|---------|---------------------------------------------------------------|----|

| 2. | Alg   | orithms | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                       |    |

|    |       |         | per Theoretic Schemes                                         |    |

|    |       | 2.1.1   | ESIGN                                                         |    |

|    |       | 2.1.2   | Feige-Fiat-Shamir                                             |    |

|    |       | 2.1.3   | •                                                             |    |

|    |       | 2.1.4   | Elliptic Curve El Gamal                                       |    |

|    | · .   | 2.1.5   | Knapsack Schemes                                              |    |

|    | 2.2   |         | nental Schemes                                                |    |

|    | 2.3   |         | g Theoretic Schemes                                           |    |

|    | 2.4   |         | bilistic Identification Schemes                               |    |

|    |       | 2.4.1   | Permuted Kernel Problem Scheme                                |    |

|    |       | 2.4.2   | Syndrome Decoding Based Identification Scheme                 |    |

|    |       | 2.4.3   | Constrained Linear Equation Scheme                            |    |

|    |       | 2.4.4   | Perceptron Scheme                                             |    |

|    |       | 2.4.5   | General Strategies For Efficiently Implementing Probabilistic |    |

|    |       | 2.4.5   | Schemes                                                       |    |

|    | 2.5   | Hash-   | Based Signature Schemes                                       | 27 |

|    |       | 2.5.1   | One-Time Signatures                                           | 27 |

|    |       | 2.5.2   | Converting One-time Schemes to N-time Schemes                 |    |

|    | 2.6   | Polyn   | omial Schemes                                                 |    |

|    |       | 2.6.1   | Hidden Field Equations (HFE)                                  | 37 |

|    |       | 2.6.2   |                                                               |    |

|    |       | 2.6.3   | HFE signature and verification                                |    |

|    |       | 2.6.4   | Variation on Length of the signature                          |    |

|    | 2.7   | Crypt   | ographic Primitives                                           |    |

|    |       | 2.7.1   | Modular Multiple-Precision Exponentiation Algorithms          |    |

|    |       | 2.7.2   | Finite Field Arithmetic and Field Towers                      |    |

|    | 2.8   | Comp    | parative Summary and Conclusions                              | 41 |

| 3. | Gen   | eral Pu | rpose Commercial Computing Platforms                          | 43 |

|    | 3.1   | Issues  | s of Concern                                                  | 43 |

|    | 3.2   | Micro   | processors/Microcontrollers                                   |    |

|    |       | 3.2.1   |                                                               |    |

|    |       | 3.2.2   | NEC V850/SA1 Microcontroller                                  |    |

|    |       | 3.2.3   | Toshiba/Motorola Echelon Neuron Chip                          |    |

|    | 3.3   | Digita  | al Signal Processors                                          |    |

|    |       | 3.3.1   | Analog Devices ADSP-2103                                      |    |

|    |       | 3.3.2   | Hitachi SH-DSP                                                |    |

|    |       | 3.3.3   | Lucent DSP1611/17                                             | 47 |

|    |       | 3.3.4   | Motorola DSP56L811                                            |    |

|    |       | 3.3.5   | NEC uPD7701x                                                  | 48 |

| 3.3.7       Zilog Z89462                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |         | 3.3.6 TI TMS320LC5x                                | 48 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|----------------------------------------------------|----|

| 3.4 Comparative Summary.       48         4. Memory Storage on Custom Designed Circuits.       49         4.1 Memory Storage on Custom Designed Circuits.       49         4.2 Read Only Memories.       50         4.2.1 Atmel       50         4.2.2 Advance Micro Devices (AMD).       50         4.2.3 Cypress.       51         4.2.4 Intel       51         4.2.5 Samsung       51         4.2.6 Micron       51         4.2.7 EPROM Comparative Study.       52         4.3 Random Access Memories.       53         4.3.1 Hitachi       53         4.3.2 Cypress       53         4.3.3 Samsung       53         4.3.4 Mitsubishi       53         4.3.5 Performance Semiconductor       54         4.3.6 GSI Technology.       54         4.3.7 Comparative Study       54         5. Special Purpose Computing Platforms       55         5.1 SGS Thompson ST16CF54       55         5.2 Motorola MSC0501       56         5.3 Siemens SLE44CR80S       56         5.4.1 Frequency       58         6.1.2 Contage Techniques for Low-Power Applications       57         5.6 Motorola Advanced INFOSE Modules       57         5.6 Lot    |     |         | 3.3.7 Zilog Z89462                                 | 48 |

| 4.1       Memory Storage on Custom Designed Circuits       49         4.2       Read Only Memories       50         4.2.1       Atmel       50         4.2.2       Advance Micro Devices (AMD)       50         4.2.3       Cypress       51         4.2.4       Intel       51         4.2.5       Samsung       51         4.2.6       Micron       51         4.2.7       EPROM Comparative Study       51         4.2.8       Flash Memory Comparative Study.       52         4.3       Random Access Memories       53         4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology       54         4.3.7       Comparative Study       54         5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motrola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C83                                                                      |     | 3.4     |                                                    |    |

| 4.1       Memory Storage on Custom Designed Circuits       49         4.2       Read Only Memories       50         4.2.1       Atmel       50         4.2.2       Advance Micro Devices (AMD)       50         4.2.3       Cypress       51         4.2.4       Intel       51         4.2.5       Samsung       51         4.2.6       Micron       51         4.2.7       EPROM Comparative Study       51         4.2.8       Flash Memory Comparative Study.       52         4.3       Random Access Memories       53         4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology       54         4.3.7       Comparative Study       54         5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motrola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C83                                                                      | 4.  | Men     | norv Storage                                       |    |

| 4.2       Read Only Memories.       50         4.2.1       Atmel       50         4.2.2       Advance Micro Devices (AMD)       50         4.2.3       Cypress       51         4.2.4       Intel       51         4.2.5       Samsung       51         4.2.6       Micron       51         4.2.7       EPROM Comparative Study       51         4.2.8       Flash Memory Comparative Study       52         4.3       Random Access Memories       53         4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology       54         4.3.7       Comparative Study       55         5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR808       56         5.4       Philips P3C4588       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Module                                                                      |     |         |                                                    |    |

| 4.2.1       Aimel       50         4.2.2       Advance Micro Devices (AMD)       50         4.2.3       Cypress       51         4.2.4       Intel       51         4.2.5       Samsung       51         4.2.6       Micron       51         4.2.7       EPROM Comparative Study       51         4.2.8       Flash Memory Comparative Study       52         4.3       Random Access Memories       53         4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology       54         4.3.7       Comparative Study       54         4.3.7       Comparative Study       54         5.1       SGS Thompson ST16/CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44(CR80S       56         5.4       Philips P83/C858       56         5.5       Cobrocessor for Cryptography Applications       57         6.1       General Design Techniques for                                                                       | ·   | 4.2     |                                                    |    |

| 42.3       Cypress       51         42.4       Intel       51         42.5       Samsung       51         42.6       Micron       51         42.7       EPROM Comparative Study       51         42.8       Flash Memory Comparative Study       52         4.3       Random Access Memories       53         4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology.       54         4.3.7       Comparative Study       54         4.3.7       Comparative Study       54         4.3.7       Comparative Study       54         5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.1       Gener                                                                      |     |         |                                                    |    |

| 42.4       Intel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |         | 4.2.2 Advance Micro Devices (AMD)                  | 50 |

| 4.2.5       Samsung       \$1         4.2.6       Micron       \$1         4.2.7       EPROM Comparative Study       \$1         4.2.8       Flash Memory Comparative Study       \$2         4.3       Random Access Memories       \$3         4.3.1       Hitachi       \$33         4.3.2       Cypress       \$33         4.3.3       Samsung       \$33         4.3.4       Mitsubishi       \$33         4.3.5       Performance Semiconductor       \$54         4.3.6       GSI Technology.       \$44         4.3.7       Comparative Study       \$54         4.3.7       Comparative Study       \$54         4.3.7       Comparative Study       \$54         4.3.7       Comparative Study       \$54         5.       Special Purpose Computing Platforms       \$55         5.1       SGS Thompson ST16CF54       \$55         5.2       Motorola MSC0501       \$66         5.3       Siemens SLE44CR80S       \$66         5.4       Philips P83C838       \$66         5.5       Co-processor for Cryptography Applications       \$77         5.6       Motorola Advanced INFOSEC Modules       \$77                            |     |         | 4.2.3 Cypress                                      | 51 |

| 4.2.6       Micron       \$1         4.2.7       EPROM Comparative Study       \$1         4.2.8       Flash Memory Comparative Study       \$2         4.3       Random Access Memories       \$33         4.3.1       Hitachi       \$33         4.3.2       Cypress       \$53         4.3.3       Samsung       \$33         4.3.4       Mitsubishi       \$33         4.3.5       Performance Semiconductor       \$44         4.3.6       GSI Technology       \$44         4.3.7       Comparative Study       \$44         5.       Special Purpose Computing Platforms       \$55         5.1       SGS Thompson ST16CF54       \$55         5.2       Motorola MSC0501       \$66         5.3       Siemens SLE44CR80S       \$66         5.4       Philips P83C858       \$56         5.5       Co-processor for Cryptography Applications       \$57         5.6       Motorola Advanced INFOSEC Modules       \$57         6.1       General Design Techniques for Low-Power Applications       \$58         6.1.1       Frequency       \$58         6.1.2       Voltage       \$59         6.1.3       Capaocitance       <          |     |         |                                                    |    |

| 4.2.7       EPROM Comparative Study       51         4.2.8       Flash Memory Comparative Study       52         4.3       Random Access Memories       53         4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology       54         4.3.7       Comparative Study       54         4.3.7       Comparative Study       54         5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         6.6       Custom Design Computing Platform       58         6.1       General Design Techniques for Low-Power Applications       58         6.1.2       Voltage       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random                          |     |         | •                                                  |    |

| 4.2.8       Flash Memory Comparative Study       52         4.3       Random Access Memories       53         4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology       54         4.3.7       Comparative Study       54         4.3.7       Comparative Study       54         4.3.7       Comparative Study       54         5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         6.       Custom Design Computing Platform       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       59 </td <td>1</td> <td></td> <td></td> <td></td> | 1   |         |                                                    |    |

| 4.3       Random Access Memories       53         4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology       54         4.3.7       Comparative Study       54         4.3.7       Comparative Study       54         5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         6.6       Motorola Advanced INFOSEC Modules       57         6.1       General Design Techniques for Low-Power Applications       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       59         6.2.2       True Random Number Genera                          |     |         | 4.2.7 EPROM Comparative Study                      | 51 |

| 4.3.1       Hitachi       53         4.3.2       Cypress       53         4.3.3       Samsung       53         4.3.4       Mitsubishi       53         4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology       54         4.3.7       Comparative Study       54         5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.       Custom Design Computing Platform       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance.       59         6.2.2       True Random Number Generation       59         6.2.2       True Random Number Generation       59         6.2.2       True Random Number Generation       60         7.1       Design of Capitate Low-Power Algorithms                                 |     |         | 4.2.8 Flash Memory Comparative Study               | 52 |

| 4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 4.3     |                                                    |    |

| 4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |         |                                                    |    |

| 4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |         |                                                    |    |

| 4.3.5       Performance Semiconductor       54         4.3.6       GSI Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |         | <b>U</b>                                           |    |

| 4.3.6       GSI Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |         |                                                    |    |

| 4.3.7       Comparative Study       54         5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.1       General Design Computing Platform       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       59         6.2.2       True Random Number Generation       60         7.1       Design of Candidate Low-Power Algorithms       60         7.2       Detimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       62                                               |     |         | •                                                  |    |

| 5.       Special Purpose Computing Platforms       55         5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.       Custom Design Computing Platform       58         6.1       General Design Techniques for Low-Power Applications       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       59         6.2.2       True Random Number Generation       60         7.1       Design of Candidate Low-Power Algorithms       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                               |     |         |                                                    |    |

| 5.1       SGS Thompson ST16CF54       55         5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.       Custom Design Computing Platform       58         6.1       General Design Techniques for Low-Power Applications       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       59         6.2.2       True Random Number Generation       60         7.1       Design of Candidate Low-Power Algorithms       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                    |     |         |                                                    |    |

| 5.2       Motorola MSC0501       56         5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.       Custom Design Computing Platform       58         6.1       General Design Techniques for Low-Power Applications       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance       59         6.2       Design Techniques for Random Number Generation       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       60         7.1       Design of Candidate Low-Power Algorithms       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                      |     | Spec    |                                                    |    |

| 5.3       Siemens SLE44CR80S       56         5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.       Custom Design Computing Platform       58         6.1       General Design Techniques for Low-Power Applications       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance       59         6.2       Design Techniques for Random Number Generation       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       60         7.1       Design of Candidate Low-Power Algorithms       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                                                                  | • . | ÷ · · - |                                                    |    |

| 5.4       Philips P83C858       56         5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.       Custom Design Computing Platform.       58         6.1       General Design Techniques for Low-Power Applications.       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance.       59         6.2       Design Techniques for Random Number Generation       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       60         7.       A Custom Design of Candidate Low-Power Algorithms       60         7.1       Design of Generic Mathematical Operations       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                                |     |         |                                                    |    |

| 5.5       Co-processor for Cryptography Applications       57         5.6       Motorola Advanced INFOSEC Modules       57         6.       Custom Design Computing Platform       58         6.1       General Design Techniques for Low-Power Applications       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       59         6.2.2       True Random Number Generation       60         7.       A Custom Design of Candidate Low-Power Algorithms       60         7.1       Design of Generic Mathematical Operations       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                                                                                             |     |         |                                                    |    |

| 5.6       Motorola Advanced INFOSEC Modules       57         6.       Custom Design Computing Platform       58         6.1       General Design Techniques for Low-Power Applications       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance       59         6.1.3       Capacitance       59         6.2       Design Techniques for Random Number Generation       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       60         7.       A Custom Design of Candidate Low-Power Algorithms       60         7.1       Design of Generic Mathematical Operations       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.2       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                                                                                                           |     |         |                                                    |    |

| 6.       Custom Design Computing Platform.       58         6.1       General Design Techniques for Low-Power Applications.       58         6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance.       59         6.2       Design Techniques for Random Number Generation       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       60         7.       A Custom Design of Candidate Low-Power Algorithms       60         7.1       Design of Generic Mathematical Operations       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                                                                                                                                                                                                              |     |         |                                                    |    |

| 6.1 General Design Techniques for Low-Power Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4   | 5.0     | Motorola Advanced INFOSEC Modules                  |    |

| 6.1.1       Frequency       58         6.1.2       Voltage       59         6.1.3       Capacitance       59         6.2       Design Techniques for Random Number Generation       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       60         7.       A Custom Design of Candidate Low-Power Algorithms       60         7.1       Design of Generic Mathematical Operations       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6.  |         |                                                    |    |

| 6.1.2       Voltage       59         6.1.3       Capacitance       59         6.2       Design Techniques for Random Number Generation       59         6.2.1       Pseudo Random Number Generation       59         6.2.2       True Random Number Generation       59         6.2.2       True Random Number Generation       60         7.       A Custom Design of Candidate Low-Power Algorithms       60         7.1       Design of Generic Mathematical Operations       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 6.1     |                                                    |    |

| 6.1.3       Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |         |                                                    |    |

| <ul> <li>6.2 Design Techniques for Random Number Generation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |         | $\mathbf{v}$                                       |    |

| <ul> <li>6.2.1 Pseudo Random Number Generation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |         |                                                    |    |

| 6.2.2       True Random Number Generation       60         7.       A Custom Design of Candidate Low-Power Algorithms       60         7.1       Design of Generic Mathematical Operations       60         7.2       Design of Optimal El Gamal Signature Algorithm with Pre-Computation       61         7.2.1       Optimal El Gamal Hardware Implementation       62         7.2.2       Optimal El Gamal Hardware Verification       65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 6.2     |                                                    |    |

| <ul> <li>7. A Custom Design of Candidate Low-Power Algorithms</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |         |                                                    |    |

| <ul> <li>7.1 Design of Generic Mathematical Operations</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |         | 6.2.2 True Random Number Generation                |    |

| <ul> <li>7.2 Design of Optimal El Gamal Signature Algorithm with Pre-Computation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.  | A C     |                                                    |    |

| <ul><li>7.2.1 Optimal El Gamal Hardware Implementation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 7.1     | Design of Generic Mathematical Operations          |    |

| <ul><li>7.2.1 Optimal El Gamal Hardware Implementation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 7.2     |                                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |         | 7.2.1 Optimal El Gamal Hardware Implementation     | 62 |

| 7.3 Design of Elliptic Curve Operations and Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |         |                                                    |    |

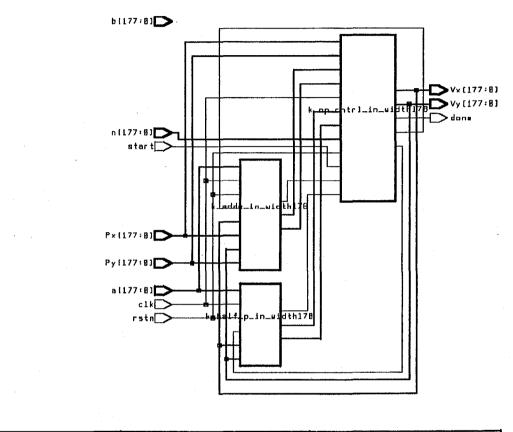

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •   | 7.3     | Design of Elliptic Curve Operations and Algorithms | 68 |

7

.

|     |      | 7.3.1 Hardware Implementation of Basic Mathematical Elliptic Curve Functio | ns 68 |

|-----|------|----------------------------------------------------------------------------|-------|

|     |      | 7.3.2 Elliptic Curve Operations                                            | 73    |

|     |      | 7.3.3 Elliptic Curve Scalar Multiplication Algorithm                       | 73    |

|     | 7.4  | Obtaining the VHDL Code for Implemented Functions                          |       |

|     | 7.5  | Comments and Further Optimizations                                         | 78    |

| 8.  | Refe | erences                                                                    | 79    |

| 9.  | App  | endix A—Additional Algorithms                                              | 81    |

|     |      | Storage/Work Balanced El Gamal Scheme                                      |       |

|     |      | 9.1.1 Evaluation of Storage/Work El Gamal Scheme                           | 81    |

|     | 9.2  | Schnorr Scheme                                                             |       |

|     | 9.3  | Chor-Rivest Knapsack Signature Scheme                                      | 83    |

|     | 9.4  | McEliece Scheme                                                            | 84    |

| 10. | App  | pendix B                                                                   | 86    |

|     | 10.1 | Permuted Kernel Problem Scheme                                             | 86    |

|     |      | 2 Syndrome Decoding Based Identification Scheme (Stern)                    |       |

## Figures

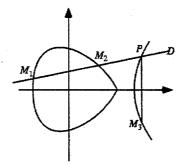

| Figure 2.1 Addition on an Elliptic Curve                               |    |

|------------------------------------------------------------------------|----|

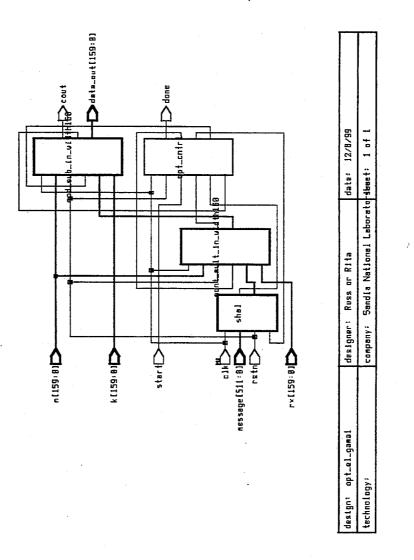

| Figure 7.1 Optimal El Gamal Hardware Implementation Diagram            | 63 |

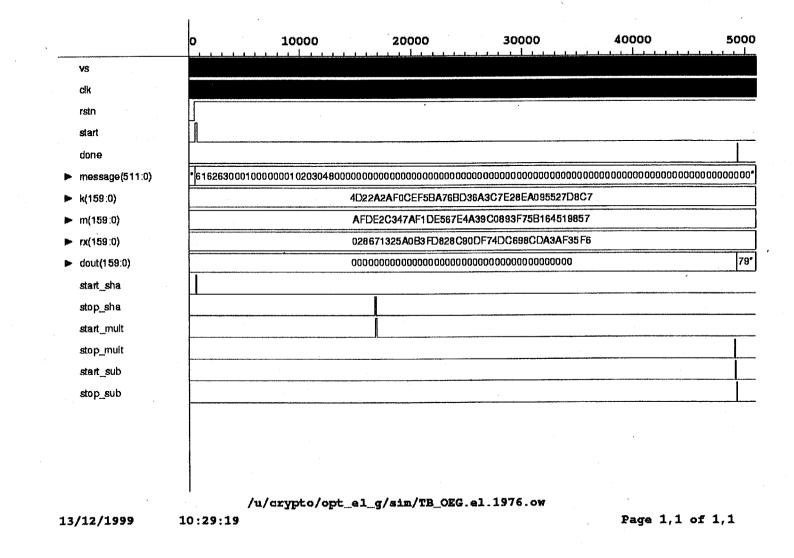

| Figure 7.2a Optimal El Gamal Hardware Verification, Inputs and Outputs |    |

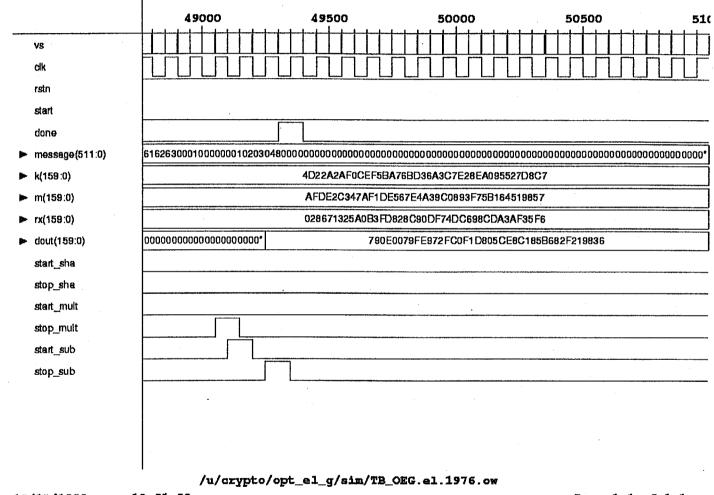

| Figure 7.2b Optimal El Gamal Hardware Verification, Inputs and Outputs | 67 |

| Figure 7.3 Elliptic Curve Scalar Multiplication                        | 74 |

| Figure 7.4 Multiplication in $GF(2^{178})$                             | 77 |

## Tables

| Table 2.1 Parameter Sizes for ESIGN                                                    | 15 |

|----------------------------------------------------------------------------------------|----|

| Table 2.2 Parameter Sizes for Feige-Fiat-Shamir                                        | 17 |

| Table 2.3 Parameter Sizes for Optimal El Gamal Scheme                                  |    |

| Table 2.4 Parameter Sizes for Elliptic Curve El Gamal over GF(p)                       |    |

| Table 2.5 Security versus q and k for Syndrome Decoding                                |    |

| Table 2.6 Parameter Sizes for Merkle's Single Bit Scheme                               |    |

| Table 2.7 Candidate Public Key Authentication Algorithms for the Low-Power Environment |    |

| Table 4.1 Comparative Study of ROM Memories                                            |    |

| Table 4.2 EPROM Data Compilation                                                       |    |

| Table 4.3 Flash Memory Data Compilation                                                |    |

| Table 4.4 SRAM Data Compilation                                                        |    |

| Table 7.1 Size and Speed Comparisons of Implementations of Mathematical Operations     |    |

| Table 9.1 Parameter Sizes for Storage/Work El Gamal Scheme |  |

|------------------------------------------------------------|--|

|------------------------------------------------------------|--|

This page intentionally left blank.

#### 1. Introduction

Cryptography is used to provide privacy, integrity, authentication, and non-repudiation of data. There are two basic categories of cryptography today: conventional or symmetric key cryptography, and public or asymmetric key cryptography. Both conventional and public key cryptography provide privacy and integrity of data through encryption; however, only public key cryptography provides the functions of authentication and non-repudiation. This is done through the use of digital signatures.

Public key, digital signature algorithms are typically computationally intensive and generate large signatures. Our focus is on low-power environments where available computing resources and power are limited. Such environments may be too prohibitive to support digital signatures. Yet, such environments often must support devices transmitting critical data that must be authenticated. For example, multilateral treaties may require remote monitoring devices for treaty verification. The device may be located in hostile territory; it may use only a small processor; and it may be required to run off a single battery that is left unattended for years. The data reported by the device will have international ramifications and must be authenticated. Digital signatures would be ideal in such situations, yet the demands of a public key algorithm may not conform to the environment.

The purpose of this Laboratory Directed Research and Development Project (LDRD) was to find, modify, or invent a computationally inexpensive public key signature scheme for efficient use in such low-power environments. We researched and tested implementations of several different types of algorithms and also investigated commercial, special purpose, and custom hardware for efficiency.

As a general solution, we recommend an elliptic curve-based digital signature scheme optimized for low-power use on custom hardware. We developed and tested such a design targeted to a custom integrated circuit (ASIC, FPGA, PLA) for use in low-power public key cryptography applications. Even more efficient algorithms may be available for use in special situations, and we point those out as well.

In symmetric key cryptography, every user of the system shares a common key that is used both for encryption and decryption. The algorithms are fast and efficient, and use commands easy for computers to carry out, such as *shift* and *exclusive-or* operations. The encryption functions are effectively "one way" (i.e., there is no mathematical way to invert the operation); however, if one has access to the key, the encryption process can be reversed to decrypt.

Since the encryption/decryption key must be kept secret and shared by users in several locations, key management problems can arise. In public key cryptography, each participant holds a private-public key pair and only the user's private key must be kept secret. Although the public key is mathematically related to the private key, knowledge of the public key reveals nothing about the secret private key and so the public key can be openly available to all. The public key is used to encrypt data that only the holder of the private key can decrypt. Because of the asymmetry of the keys and the fact that a private key belongs to a unique user, the private key can also be used to generate a digital signature unique to the user and each message.

11

Although key asymmetry in public key cryptography enables cryptographic functionality not possible with symmetric cryptographic systems, these extra capabilities are not "free." In order to enable different keys for encryption and decryption, algorithms with special mathematical properties must be used. Exploitation of these mathematical properties leads to attacks on the system. To protect against such attacks, the keys that must be used are much larger than those used with symmetric key cryptosystems. The mathematical operations, together with the large keys, means the work involved in a public key system is usually many times greater than with conventional cryptography.

Our goal was to find, modify, or create a public key signature scheme that could be adapted to perform in a low computation, low-power environment. There were several issues to consider in each scheme, including signature size and computation and storage requirements.

- Signature Size: Many of the signature schemes require that large signatures be sent with the message, regardless of message size. Since bandwidth can consume the most power in the system, minimizing the size of the signature is important.

- **Computation**: Most public key systems require modular exponentiation, a very costly operation. One of the first steps was to look at systems in which modular exponentiation was minimized or could be avoided in the signing function of the scheme (i.e., systems for which pre-computation is possible).

- **Storage**: Although storage may be a lesser issue than power consumption, unlimited storage should not be assumed.

- **RAM/ROM**: Although RAM/ROM size may be a lesser issue than power consumption, unlimited RAM/ROM should not be assumed.

Each algorithm in a public key system has a "hard" mathematical problem as the basis of its security. Used in this sense, "hard" means the operation is computationally not feasible to invert without special knowledge (e.g., the private key). We looked at algorithms based on a variety of problems including number theoretic, probabilistic, coding theoretic, polynomial-based, and hash-based. While several algorithms have great potential, others perform well only in certain situations. The study of the algorithms, together with some optimizations and a comparison of their features, can be found in Section 2.

The secondary goal of this LDRD was to evaluate various computing platforms for suitability to low-power public key cryptography. While section 2 presents an analysis of candidate public key algorithms, sections 3 and 5 present information on various computing platforms on which these algorithms must run and section 4 discusses currently available memory options. We discuss basic power consumption issues and processing features that lend themselves to low-power public key cryptography applications as well as evaluate specific general-purpose commercially available processors as candidate computing platforms. Section 5 also offers information on special purpose (e.g., smart card) and custom (e.g., ASIC) computing platforms and their potential in low-power public key cryptography applications. For hardware applications, memory can be a vital issue. Indeed, we found that the performance of some algorithms improved dramatically if pre-computed stored values could be accessed during implementation. Section 6 discusses low-power design techniques for a custom-computing platform. A customdesign platform offers the most flexibility in giving the customer exactly what is needed. Custom designs can address issues such as speed, power, security, and functionality. The entire computing platform can exist on a single Application Specific Integrated Circuit (ASIC), or can be integrated with commercially available components to produce the desired computing platform. Reconfigurable logic (Field Programmable Gate Arrays–FPGAs, Programmable Logic Arrays–PLAs) can be just as easily targeted as ASICs depending on the needs of the design.

Finally, having determined that an elliptic curve implementation of the El Gamal digital signature scheme has the most potential as a general-purpose solution, in Section 7, we present a design that further optimizes the code and takes advantage of the custom-computing platform. The design is targeted to a custom integrated circuit (ASIC, FPGA, PLA) for use in low-power public key cryptography applications.

#### 2. Algorithms

Public key algorithms base their security on the improbability that an adversary will solve a particular problem. The problems may be difficult in the sense that they are thought to be NP-complete, or it may simply be the case that no efficient algorithms are known. Number theoretic problems provide the most common basis for public key schemes of today. Indeed, most cryptosystems base their security on the difficulty of solving the discrete logarithm problem, the integer factorization problem, or a related analog of these problems. These schemes involve expensive computations such as modular multiplications and can have long signatures. Hence, these algorithms may not be suitable for many low-power environments. Nevertheless, optimizations may be made to improve the performance of these algorithms.

In addition to studying common public key schemes, we broadened our search to include some lesser-studied and lesser-used algorithms in the hope they would be useful in a low-power environment. In particular, we studied schemes based on coding theoretic problems, probabilistic schemes, hash-based schemes and polynomial schemes. We found that coding theoretic schemes generally have very large keys, making them unsuitable for low-power environments. We present them here for informational purposes only.

Probabilistic schemes have been defined primarily as identification schemes. Most are based on NP-complete problems, and any public key identification scheme can be converted into a signature scheme. Although we had difficulty translating them into signature schemes efficient enough for the low-power world, those ideas are presented as a possible basis for future research.

Hash-based schemes are very efficient computationally but can be limiting in other ways. For example, many schemes require pre-determination of the number of signatures that will be signed. Others are based on chaining, and verification becomes impossible if messages are ever lost, leaving them open to denial of service attacks.

Finally, polynomial-based schemes hold promise for computing shorter signatures, but the public key sizes are very large and verification can be difficult.

In each category (number theoretic, coding theoretic, probabilistic, hash-based and polynomial) we examined a number of algorithms and analyzed their performance based on our criteria of signature size, storage and computation requirements. We present a comparative summary of the best candidate algorithms in a table near the end of this section. Some of the algorithms are good for signatures and some are most efficient at verification. Often, the very low-power environments are concerned only with signing; hence, the emphasis is on signing.

If two-way authentication is desired, different algorithms may be used for signing and verification. The best general solution we found for signatures was the elliptic curve-based version of the El Gamal scheme. In addition to being quite efficient as is, we found some very helpful optimizations in the elliptic curve operations as well as the underlying field operations. The implementation of the algorithm in custom hardware design is described in Section 7.

All of the problems presented here are "hard" in the sense that there are no known algorithms for solving them efficiently. The recommended key sizes are chosen to protect against attacks that the best computers with the most efficient algorithms could reasonably mount. As algorithms to solve these problems become more efficient, key sizes should be increased. The user is advised to consult the literature for current recommended key sizes.

#### 2.1 Number Theoretic Schemes

There are two main problems that the security of number theoretic schemes is based upon: the discrete logarithm problem and the integer factorization problem. Given a group G and two group elements  $\alpha$ ,  $\beta = \alpha^{l}$ , the discrete logarithm problem is to find the integer t. The group G should be chosen so that this problem is difficult. The most common groups chosen for use include  $(Z/pz)^{*} = \{1,2,..,p-1\}$ , the non-zero group of integers modulo a large (non-smooth) prime, p, and the group of points on an elliptic curve modulo p. Given a large integer n, the integer factorization problem is to find the divisors of n. Typically, cryptographic systems based on this problem use a large integer n which is the product of two large primes p and q: n = pq. Most of the algorithms presented here are based on one of these problems or a variant of one of these problems.

The following algorithms require modular multiple-precision operations. Although modular arithmetic usually requires a fair amount of computing power, these algorithms minimize these requirements by avoiding exponentiation or by minimizing the cost of exponentiation, and by using pre-computation and added storage. Features associated with each algorithm make it a viable choice despite the requirement for modular multiple-precision arithmetic operations.

#### 2.1.1 ESIGN

The ESIGN (Efficient digital SIGNature) Algorithm is described in [MvV97]. It is based on the Integer Factorization problem. This algorithm may be a candidate in a low-power environment where two-way authentication is required.

To generate a key pair:

- 1. Select random primes p and q such that  $p \ge q$  and p, q are roughly the same bit-length

- 2. Compute  $n = p^2 q$

- 3. Select a positive integer  $k \ge 4$

An entity's public key is (n, k). The corresponding private key is (p, q).

To generate a signature:

1. Compute  $v = H(m), H : \{0,1\}^* \rightarrow Z/nZ$

2. Select a secret random integer  $x, 0 \le x < p$

- 3. Compute  $w = |((v x^k) \mod n)/(pq)|$  and  $y = w \cdot (kx^{k-1})^{-1} \mod p$

- 4. Compute the signature  $s = (x + ypq) \mod n$

To verify a signature:

- 1. Compute  $u = s^k \mod n$  and z = H(m)

- 2. Accept the signature iff  $z \le u \le z + 2^{\left\lfloor \frac{2}{3} \lg n \right\rfloor}$

The recommended modulus length, n, is 768 bits. Therefore the signature length is also 768 bits or 96 bytes. Since k can be chosen to be small, the exponentiation required to generate w can be optimized for a small known exponent and a known modulus. The same is true of the exponentiation required for verification, making this algorithm a possibility in a low-power environment where two-way authenticated communication is required.

#### 2.1.1.1 Evaluation of ESIGN

| Parameter | Description                                               | Size (in bits) |

|-----------|-----------------------------------------------------------|----------------|

| Р         | Secret prime                                              | ≈256           |

| Q         | Secret prime                                              | ≈ 256          |