## GENERAL PURPOSE COMPUTING IN GPU - A WATERMARKING CASE STUDY

## Anthony Hanson

Thesis Prepared for the Degree of

MASTER OF SCIENCE

### UNIVERSITY OF NORTH TEXAS

August 2014

### APPROVED:

Saraju Mohanty, Major Professor

Elias Kougianos, Co-Major Professor

Mahadevan Gomathisankaran, Committee

Member

Barret Bryant, Chair of the Department of

Computer Science and Engineering

Costas Tsatsoulis, Dean of the College of

Engineering

Mark Wardell, Dean of the Toulouse Graduate

School

Hanson, Anthony. *General Purpose Computing in GPU - A Watermarking Case Study*. Master of Science (Computer Science), August 2014, 78 pp., 8 tables, 15 figures, references, 42 titles.

The purpose of this project is to explore the GPU for general purpose computing. The GPU is a massively parallel computing device that has a high-throughput, exhibits high arithmetic intensity, has a large market presence, and with the increasing computation power being added to it each year through innovations, the GPU is a perfect candidate to complement the CPU in performing computations. The GPU follows the single instruction multiple data (SIMD) model for applying operations on its data. This model allows the GPU to be very useful for assisting the CPU in performing computations on data that is highly parallel in nature. The compute unified device architecture (CUDA) is a parallel computing and programming platform for NVIDIA GPUs. The main focus of this project is to show the power, speed, and performance of a CUDA-enabled GPU for digital video watermark insertion in the H.264 video compression domain. Digital video watermarking in general is a highly computationally intensive process that is strongly dependent on the video compression format in place. The H.264/MPEG-4 AVC video compression format has high compression efficiency at the expense of having high computational complexity and leaving little room for an imperceptible watermark to be inserted. Employing a human visual model to limit distortion and degradation of visual quality introduced by the watermark is a good choice for designing a video watermarking algorithm though this does introduce more computational complexity to the algorithm. Research is being conducted into how the CPU-GPU execution of the digital watermark application can boost the speed of the applications several times compared to running the application on a standalone CPU using NVIDIA visual profiler to optimize the application.

Copyright 2014

by

Anthony Hanson

# ACKNOWLEDGEMENTS

I would like to thank my wife, Yuting, for her support during the time it has took me to finalize this thesis.

I would like to thank my thesis advisor Dr. Saraju Mohanty as well for his support and guidance during my thesis.

I would like to thank Dr. Elias Kougianos and Dr. Mahadevan Gomathisankaran for serving on my committee.

# TABLE OF CONTENTS

|     | Page                                                                     |

|-----|--------------------------------------------------------------------------|

| AC  | CKNOWLEDGEMENTSiii                                                       |

| LIS | ST OF TABLESviii                                                         |

| LIS | ST OF FIGURESix                                                          |

| Ch  | napters                                                                  |

| 1.  | INTRODUCTION1                                                            |

|     | 1.1. Overview                                                            |

|     | 1.2. Heterogeneous CPU-GPU Computing Systems                             |

|     | 1.2.1. Parallel Programming                                              |

|     | 1.3. Digital Watermark on H.264 Compressed Video                         |

|     | 1.3.1. Parallel Processing of Digital Watermarking and H.264 Operations5 |

|     | 1.4. Organization of This Thesis                                         |

| 2.  | RELATED PRIOR RESEARCH8                                                  |

|     | 2.1. General-purpose Computing on Graphics Processing Units              |

|     | 2.2. Digital Watermark Parallelization                                   |

|     | 2.2.1. Hardware Implementation                                           |

|     | 2.2.2. Software Implementation                                           |

|     | 2.2.2.1. Digital Image Watermark                                         |

|     | 2.2.2.2. Digital Video Watermarking                                      |

|     | 2.3. Video Coding on GPU                                                 |

|     | 2.4. Novel Contributions of This Thesis                                  |

| 3. | GENERAL PURPOSE COMPUTING PROBLEM ON GPU                   | 17 |

|----|------------------------------------------------------------|----|

|    | 3.1. Overview                                              | 17 |

|    | 3.2. Modern CPU Architecture                               | 18 |

|    | 3.3. Modern GPU Architecture                               | 20 |

|    | 3.4. Heterogeneous CPU-GPU Architecture                    | 22 |

|    | 3.5. General-Purpose Computing on Graphics Processor Units | 23 |

|    | 3.5.1. Overview                                            | 23 |

|    | 3.5.2. Concepts and Methods                                | 23 |

|    | 3.5.3. Bottleneck                                          | 25 |

| 4. | PARALLEL COMPUTING AND PROGRAMMING ON A CUDA-ENABLED GPU   | 27 |

|    | 4.1. Overview                                              | 27 |

|    | 4.2. Languages and Libraries                               | 27 |

|    | 4.2.1. CUDA                                                | 28 |

|    | 4.2.1.1. Scalability                                       | 28 |

|    | 4.2.2. OpenACC                                             | 29 |

|    | 4.2.3. C++ AMP                                             | 31 |

|    | 4.2.4. OpenCL                                              | 31 |

|    | 4.3. Programming Model                                     | 32 |

|    | 4.4. Applications                                          | 34 |

| 5. | DIGITAL VIDEO WATERMARK                                    | 35 |

|    | 5.1. Introduction                                          | 35 |

|    | 5.2. Watermark Framework                                   | 36 |

|    | 5.3. Security and Attacks                                  | 40 |

|    | 5.4. Video Watermarking                                   | 41 |

|----|-----------------------------------------------------------|----|

|    | 5.4.1. Overview                                           | 41 |

|    | 5.4.2. H.264/MPEG-4 AVC                                   | 42 |

|    | 5.4.2.1. Watermark Embedding and Extraction and Detection | 42 |

|    | 5.4.2.2. Security and Attacks                             | 43 |

|    | 5.5. Software Implementation                              | 44 |

|    | 5.6. Hardware Implementation                              | 45 |

|    | 5.7. Parallelization                                      | 45 |

|    | 5.7.1. Software Implementation on a CUDA-Enabled GPU      | 45 |

|    | 5.7.2. Hardware Implementation                            | 46 |

| 6. | H.264/MPEG-4 AVC                                          | 47 |

|    | 6.1. Overview                                             | 47 |

|    | 6.2. Concepts of Video Coding                             | 48 |

|    | 6.2.1. Block Motion Compensation-Based Video Compression  | 49 |

|    | 6.2.2. H.264 Syntax and Structure                         | 49 |

|    | 6.2.3. Profiles and Levels                                | 51 |

|    | 6.3. Encoding and Decoding                                | 52 |

|    | 6.3.1. Encoding Process                                   | 52 |

|    | 6.3.2. Decoding Process                                   | 54 |

|    | 6.4. Software Implementation                              | 55 |

|    | 6.5. Parallelization                                      | 57 |

|    | 6.5.1. Software Implementation on a CUDA-Enabled GPU      | 57 |

|    | 6.5.2. Hardware Implementation                            | 57 |

| 7. | THE  | PROPOSED VIDEO COMPRESSION AND WATERMARK IN GPU COMPUTIN | 1G |

|----|------|----------------------------------------------------------|----|

|    | ENV  | VIRONMENT                                                | 59 |

|    | 7.1. | H.264 Video Compression Algorithm                        | 59 |

|    | 7.2. | H.264 Digital Video Watermark Embedding Algorithm        | 60 |

| 8. | EXP  | ERIMENTAL RESULTS                                        | 61 |

|    | 8.1. | Experimental Setup                                       | 61 |

|    | 8.2. | Experiment                                               | 63 |

|    | 8.3. | Results                                                  | 65 |

|    | 8.4. | Discussion of Results                                    | 68 |

|    | 8.5. | Comparison With Related Research                         | 69 |

| 9. | CON  | ICLUSION AND FUTURE RESEARCH                             | 70 |

|    | 9.1. | Summary                                                  | 70 |

|    | 9.2. | Conclusions                                              | 71 |

|    | 9.3. | Future Research                                          | 72 |

| RF | FFRE | ENCE LIST                                                | 73 |

# LIST OF TABLES

| 8.1. | Test Hardware Setup                               | 61 |

|------|---------------------------------------------------|----|

| 8.2. | NVIDIA GeForce GT 555M Properties                 | 61 |

| 8.3. | Test System Software Setup                        | 62 |

| 8.4. | Test Software Setup                               | 63 |

| 8.5. | Video Properties                                  | 63 |

| 8.6. | Watermark Properties                              | 64 |

| 8.7. | Frame Rate and Bitrate Calculated for CPU and GPU | 65 |

| 8.8. | Watermark Execution Time (s)                      | 65 |

# LIST OF FIGURES

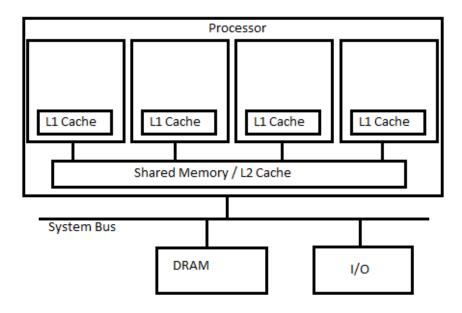

| 3.1. | Multi-core chip with inter-core bus                                               | 19 |

|------|-----------------------------------------------------------------------------------|----|

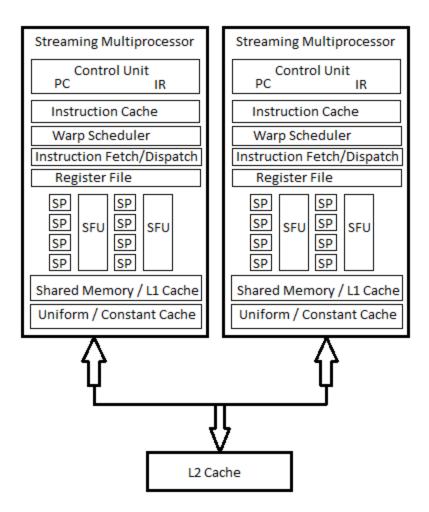

| 3.2. | CUDA GPU streaming multiprocessor (SM)                                            | 21 |

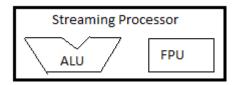

| 3.3. | CUDA GPU streaming processor (SP)                                                 | 21 |

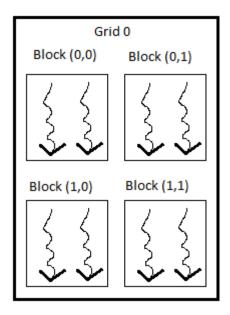

| 4.1. | 2-Dimensional (2,2,1) grid organization                                           | 33 |

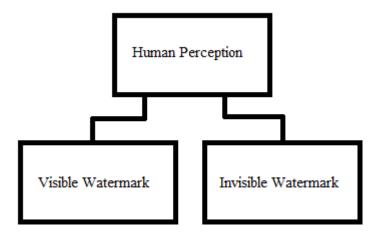

| 5.1. | Human perception                                                                  | 36 |

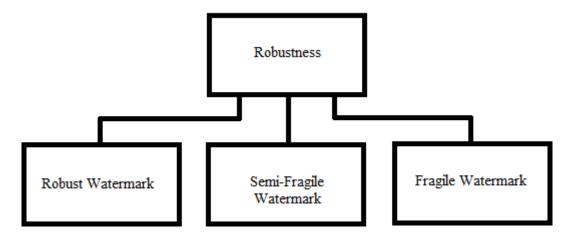

| 5.2. | Robustness                                                                        | 37 |

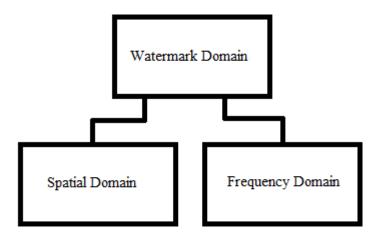

| 5.3. | Watermark domain                                                                  | 38 |

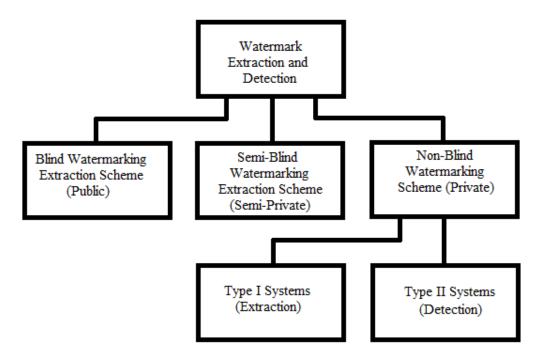

| 5.4. | Watermark extraction and detection process                                        | 38 |

| 5.5. | Watermark encoder and decoder                                                     | 39 |

| 6.1. | The encoder stages                                                                | 52 |

| 6.2. | The decoder stages                                                                | 54 |

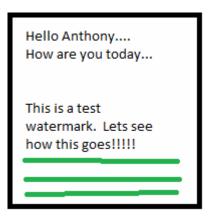

| 8.1. | A watermark logo used during the watermark insertion                              | 64 |

| 8.2. | Comparison of the original H.264 and watermarked H.264 frame in the short video   | 66 |

| 8.3. | Comparison of the original H.264 and watermarked H.264 frame in the midsize video | 67 |

| 8.4. | Comparison of the original H.264 and watermarked H.264 frame in the long video    | 68 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1. Overview

Today's computers are heterogeneous CPU-GPU computing systems. The CPU, at the moment, is a multi-core system designed to work on general computing of data that is serial in nature and maintain the execution speed of sequential programs. The GPU is a massive parallel computing platform supporting many-core (or many-threads) processor comprising of many arithmetic units to work on data that is parallel in nature. The GPU's primary role is to support 2D and 3D graphics, audio-, image-, and video-processing, video games, visual computing, and graphical user interfaces for today's complexly designed operating systems. Recent additions to the GPU such as programming instructions, multiple gigabytes of graphic double data rate (GDDR) DRAM supporting a wider bandwidth for higher throughput, more highly threaded streaming multiprocessors (SMs) and streaming processors (SPs), unified graphics and computing processors, programmable processors, and most importantly, a generic data-parallel computation model for non-graphics applications, have enabled non-graphics programmers to take advantage of the massive parallel computing power of the GPU for developing applications. However, there is one major limitation to the GPU and that is, the data has to be parallel in nature for the GPU to be effective at processing it in a highly efficient manner.

A digital watermark is the insertion of an image in a robust and visible or invisible manner inside an image or video for the purposes of protecting intellectual property (IP) and enforcing copyright protection. Various implementations have been proposed for images and video. Inserting a watermark into a video comes with its own challenges and computational complexities. What complicates this matter even more is the video compression format of the

video the digital watermark is being inserted into, such as the H.264/MPEG-4 AVC (or H.264 for short). Compression is needed for videos that involve storage and/or transmission such as movies and streaming video.

By their very nature, digital watermarking and video compression formats such as H.264 are computationally intensive tasks. Real-time encoding of video streams using a digital watermarking scheme is extremely computationally intensive. Being able to support high video quality and high throughput while minimizing distortion in a reasonable amount of time is a daunting task. Fortunately, the encoding and decoding stage of the H.264 video compression and the inserting of the digital watermarking do contain operations that can be parallelized such as computing DCT coefficients from macroblocks, variable block size motion estimation implementation, inter prediction, and intra prediction to name a few.

## 1.2. Heterogeneous CPU-GPU Computing Systems

Modern GPUs are massive parallel processors that are designed to support many threads and are throughput oriented. They are designed to complement the CPU, not replace it. This is because the GPUs do not perform well on some tasks that the CPU is designed to perform well on, such as tasks that are serial in nature. For application tasks that are low latency and only have a few threads, the CPU is the best choice. For application tasks that have a long latency, high throughput, and are parallel in nature, the GPU is the best choice. The GPU is also a good choice for handling numerically intensive tasks because of the many arithmetic units the GPU supports. Thus, a CPU-GPU computing system is needed to tackle the many tasks that are presented in the system and execution of an application.

The heterogeneous CPU-GPU system consists of the host, the CPU, and 1 or more GPU devices. To support the heterogeneous CPU-GPU execution of an application, NVIDIA developed CUDA as a generic data-parallel programming computation model for non-graphics applications. This facilitated the ease at which non-graphics programmers can take advantage of the GPU parallel computing capabilities.

### 1.2.1. Parallel Programming

Many modern applications process huge amounts of data. Much of the data is modeled on physical phenomena. Much of the data in these systems can be evaluated independently thus forming the basis for data parallelism. This data parallelism needs to be exploited by devices such as the GPU and more importantly, by languages such as CUDA that support massive parallelism and heterogeneous computing. CUDA C is a runtime system that is an extension of the C language and is a parallel computing platform for NVIDIA GPUs. This language supports many threads to exploit the data parallelism inherent in physical phenomena. OpenACC, is a standard for parallel computing using compiler directives to facilitate parallel programming of heterogeneous computing systems such as CPU-GPU systems.

### 1.3. Digital Watermark on H.264 Compressed Video

Digital watermarking is an image inserted into images or videos to protect IP and enforce copyright protection for businesses and industry [1]. Video watermarks tend to be used in video applications such as broadcast monitoring, source tracking, and copyright protection.

Digital watermarking is a form of information hiding related to steganography with the distinction being that digital watermarks are robust to malicious or accidental attacks. The three

aspects of information hiding are security, capacity, and robustness. Security deals with the detection of information, capacity deals with the amount of bits hidden, and robustness deals with resistance to accidental and malicious modifications. With robustness being desirable for copyright protection schemes, video watermarking algorithms normally prefer robustness. Removal of the watermark will introduce severe degradation.

H.264 is an industry standard video compression format (or specification) for reducing video capacity size for storage and/or transmission. It is useful for many applications dealing with recording, compression, and distribution such as Blu-ray disc, broadcast, mobile digital, and digital satellite TV, high definition recording formats, internet streaming video, video surveillance, and many more applications dealing with multimedia. H.264 is a specification only for encoding videos for video compression and decoding videos for decompression for storage and/or transmission. The video codec is the actual software or hardware implementation of a specific video compression format such as the H.264 format and once the video is encoded, it can be bundled with the compressed audio such as the advanced audio coding (AAC) in a multimedia container format such as MP4. The container format can then be used for playback in a software video player.

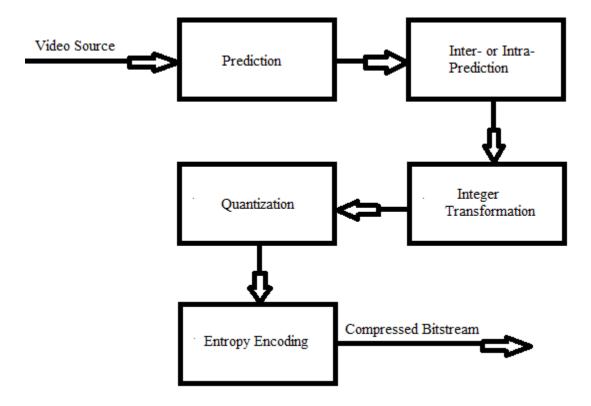

H.264 encoding involves many states: inter/intra prediction, calculating the residuals, transformation, quantization, and entropy coding. H.264 decoding contains the reverse operations: entropy decoding, rescaling, inverse transform, and reconstruction from the decoded residual macroblock (MB) and prediction MB. Video watermarking for the H.264 format can take place during the H.264 encoding stages and generally happens before or after quantization, which is of course, dependent on the algorithm. Other schemes decode and re-encode the video

for watermark embedding while other schemes embed the watermark in the compressed domain using techniques such as embedding the watermark in the residual of the I-frames.

### 1.3.1. Parallel Processing of Digital Watermarking and H.264 Operations

Digital watermarking and H.264 operations on video can be very computationally intensive depending on the application, the amount of spatial detail and motion in the video, and the length of the video. Real-time watermarking adds more complexity to this process and thus, it is difficult to achieve high quality video with a real-time watermark in a reasonable amount of time. H.264 encoding also aims to minimize the coded bitrates and maximize the decoded quality of the video and at the same time, the watermark tries to minimize the distortion introduced. This introduces computational complexity to the video encoding and decoding processes.

The CUDA C language enhances the programmability and flexibility of a GPGPU application, and being able to offload the H.264 coding and watermark process on the GPU would greatly increase the speed of the application. To accomplish this, the data itself would have to be parallelizable. Also, the data access to the global memory and memory transfers between the CPU and GPU would have to be reduced, thus increasing the usage of the shared memory in the SMs for the parallel algorithm to be of good use.

The algorithms for the H.264 compression and digital watermark are block-based and the key feature of these blocks is that they can be processed independently. This is a significant observation when considering computational complexities of the motion estimation, the evaluation of the rate-distortion modes, and integer transformations of the H.264 encoding process, to name a few. Also, considering the fact that the watermark has to be embedded during

one or more of these processes depending on the algorithm adds much computational complexity to the process. Being able to offload one or more processes to the GPU would be a significant step towards increasing the application speed and reducing the time to run the application.

### 1.4. Organization of This Thesis

The major objective of this thesis is to show the high performance that can be obtained on a CUDA-enabled GPU for general computation problems related to non-graphics applications. Two numerically intensive non-graphics applications, H.264 video compression and digital video watermarking, will be parallelized to demonstrate the power of GPU computing.

Chapter 2 covers previous works that are relevant to this thesis. It reviews the history of GPGPU and its present state. It then covers digital watermark parallelization and its hardware and software implementations on the GPU. The parallelization of the video coding process is also covered. Finally, the novel contributions of this thesis are presented.

In chapters 3 and 4, an overview of GPGPU and parallel computing and programming on a CUDA-enabled GPU are presented. Chapter 3 introduces the modern architectures of the CPU, GPU, and the heterogeneous CPU-GPU system. Concepts related to GPGPU are then covered next. Chapter 4 covers the different languages and libraries that can be written and run on a CUDA-enabled GPU. The hardware architecture and programming model of the CUDA-enabled GPU is presented. Finally, a summary of non-graphics applications that can be programmed to run on a CUDA-enabled GPU is presented.

Chapter 5 covers the details related to digital video watermarks. It presents an overview and covers details on video watermarks regarding embedding and detection, classification of

watermarking approaches, security, attacks, and H.264/MPEG-4 AVC watermarks. Finally, sequential and parallel digital video watermark implementation details are discussed.

Chapter 6 introduces the concepts of the H.264/MPEG-4 AVC video compression standard. The encoding and decoding process is discussed in detail. It then covers the sequential software and hardware implementations and the parallel hardware and software implementations.

Chapters 7-9 discuss the proposed algorithm, experimental setup, and conclusion and future research. Chapter 7 discusses the proposed video compression and watermark in GPU computing environment. It covers the details on the H.264 video compression, H.264 digital video watermark, the watermark embedding, and the implementation on the GPU. Chapter 8 covers the experimental setup, the benchmarks, the coding, and the results. Chapter 9 offers some concluding remarks and discusses directions for future research.

#### **CHAPTER 2**

#### RELATED PRIOR RESEARCH

### 2.1. General-Purpose Computing on Graphics Processing Units

Today's GPUs are characterized as massively parallel processors designed to perform a massive number of floating-point calculations and numerically intensive tasks. They are designed to complement the CPU for numerically intensive tasks and thus form the Heterogeneous CPU-GPU architecture. The GPU is considered the most powerful parallel computing system in the PC market, thus giving the GPU a very large installed base in the marketplace. Researchers and developers have took notice of the power of the GPU and thus, became interested in harnessing the power of the GPU for general purpose computation, otherwise known as general purpose computing on the GPU (GPGPU).

Today's GPUs allow the application developer and researcher to program the fully programmable unified processor using a generic parallel programming model with a hierarchy of parallel threads, barrier synchronization, and atomic operations though this was not the case at the beginning. In 2002, after the release of DirectX 9 by Microsoft, researchers took notice of the raw performance growth of the GPU but to access the performance on the GPU for general-purpose computation, the computation problem had to be mapped to the graphics hardware, or in other words, the computation problem had to be cast to graphics operations. This was a tedious task. Owens et al. [2] provide a good introduction and survey of GPGPU. It is a literature review of GPGPU and reviews many of the algorithms and techniques that were employed to map general computation to GPUs. Ian et al. [3] wrote an extension to the standard ANSI C to incorporate the stream processing paradigm with the focus on data parallelism and arithmetic intensity, operations on data to remove data requests to the host memory and maximize localized

computation. Brooks is also the precursor to CUDA [4]. BrooksGPU [5] is a runtime implementation of the Brooks programming language for the GPU. Mark et al. [6] wrote Cg, a C-like language, to program the programmable floating-point vertex and fragment stream processors. As part of Microsoft research in 2006, the Accelerator [7] was written to provide a general parallel programming model where the programmer can write in a conventional programming language without having to learn the graphics API.

With the advent of the Direct10 x specification, Nvidia [8] took the GPU programming model a step further and came out with a specification for non-graphics applications to support a data-parallel computation model for GPGPU, known as CUDA [9]. The CUDA programming language [9] is part of the CUDA toolkit [10] and is used as an extension to C, an imperative programming language, to enable programmers to construct data parallel applications without having to learn the constructs of the graphics API and to an extent, the graphics hardware. This has accelerated the use of GPGPU to solve general computations to many fields related to cryptography, watermarking, video coding, bioinformatics, computational chemistry, computational fluid dynamics, electronic design automation, and imaging and computer vision to name a few. Kronos Group, Inc. implemented the OpenCL language specification [11], which has similar constructs compared with CUDA. In addition, OpenCL is more general in the sense that it is cross platform, parallel programming language made to across different modern processors and is endorsed by Intel [12], AMD [13], and Nvidia [14].

Many books and articles have been written with regards GPU parallel computing. The CUDA specification [9] covers all the language constructs for CUDA. The OpenCL specification [11] covers all the language constructs for OpenCL. Kirk et al. [15] discuss programming massively parallel processors using programming tools such as CUDA, OpenACC,

C++ AMP, and OpenCL to demonstrate the data-parallel computation model and heterogeneous computing. Farber [16] show the use of the CUDA toolkit for application design and development for massive parallel processors on the GPU. Kim et al. [17] present a high-level overview of GPGPU and parallel programming models and provide detailed performance analysis and guide optimizations for GPGPU programming. The GPGPU [18] website is devoted to GPGPU as a whole and contains many articles written about the current and future trends of GPGPU.

### 2.2. Digital Watermark Parallelization

There is a plethora of articles dedicated to digital watermarking and video encoding on serial processors such as the CPU though much less has been written regarding GPU and heterogeneous CPU-GPU implementations. The literature that does exist, is mostly dedicated to video coding with very few works in image watermarking and video watermarking being almost non-existent.

Some of the initial watermark implementations for the GPU were implemented using hardware-assisted methods or the graphics API before the advent of CUDA. The two reasons for using hardware assisted methods is based on the fact that digital watermarking involves computationally intensive operations and that results need to be generated instantaneously, especially for digital TV broadcasting and video conferencing.

### 2.2.1. Hardware Implementation

Mohanty et al. [19] presented an invisible-robust image watermarking hardware solution on the GPU by using a dedicated processor chip as co-processor on the GPU to achieve an

efficient high performance, real-time, and low-cost watermarking-system. Mohanty et al. [20] designed a very-large-scale integration (VLSI) architecture for accelerating watermarking methods that perform invisible robust and fragile watermarking using a field-programmable gate array (FPGA) and custom integrated circuit (IC) implementations. Kougianos et al. [21] conduct a survey of hardware based watermarking systems on GPUs, FPGAs, and digital signal processors (DSP). The caveat for the above hardware assisted watermark implementations is that they require hardware design, thus putting a limit on programming and requiring changes in the hardware architecture.

Maes et al. [22] implemented a hardware real-time watermarking detector implementation for DVD applications on an FPGA board and a TriMedia processor (IC) board. The FPGA board shows better results in terms of implementation costs and relevancy.

The authors in [23] have implemented a spread spectrum-based watermark algorithm that can be used for real-time software or low-cost hardware implementations on low powered devices such as cellular phones and PDAs, thus making the algorithm very versatile. The software and hardware implementation can be combined to reduce the overall necessary gate count, on-chip memory, and system bandwidth of the underlying hardware.

### 2.2.2. Software Implementation

### 2.2.2.1. Digital Image Watermark

Lin et al. [24] have proposed a semi-fragile watermarking algorithm for image authentication using CUDA to accelerate the discrete cosine transformation (DCT) and watermark extracting and embedding operations. Compared to the CPU, a single GPU achieves a speed-up of 32x for a 1024×1024 image size while a dual GPU achieves a speed-up of 40x. In

both cases, the goal was to achieve an operational speed-up while maintaining authentication results.

Cano et al. [25] have implemented a blind image watermarking algorithm proposed by Shieh et al. [26] using a CUDA approach to parallelize the DCT and the watermark image insertion and extraction. The benchmarks obtained from the experiments show an improved speed-up from the localized computations in the GPU but modest results when considering the communication overhead between host and GPU. This was probably due to not accessing CUDA's different memories efficiently to reduce global memory traffic between host and CPU. Cano et al. [27] implement a particle swarm optimization algorithm to optimize the blind image watermarking algorithm presented in [26] using CUDA to speed-up the optimization and the watermark algorithm.

In [28] the authors have proposed a CUDA implementation of their image watermarking algorithm that uses Huffman coding for the compression of copyright data and the modified auxiliary carry watermarking method (MACW) for embedding. CUDA is used to improve the operation speed-up of the highly compute-intensive embedding and extraction operations while maintaining coding efficiency and picture quality.

### 2.2.2.2. Digital Video Watermark

Brunton and Zhao [29] implement an invisible-fragile real-time video watermarking algorithm on a GPU with the watermarking algorithm having to be cast to graphics operations. The real-time implementation on the GPU involves using the vertex shader for the insertion and extraction operations. The fragment shader generates the tiled watermark image from the input

video stream and performs exclusive OR operations for insertion of the results in a video stream and for an output signature image.

### 2.3. Video Coding on GPU

The H.264 coding process is a compute intensive process with the motion estimation (ME) unit in the encoding process being the most compute intensive operation, taking as much as 80% of the total encoding time. Several papers in the literature have been devoted to parallelizing the H.264 video coding process in the GPU with the majority focusing on the ME.

Youngsub et al. [30] proposed a parallel motion estimation algorithm that takes into account the inter-dependencies in the calculation of motion vector predictions in motion estimation. It uses a similar approach to the x264 encoder diamond search algorithm and hexagon search algorithm in that only a few macroblocks (MBs) are looked at compared to all MBs in a full search algorithm to determine the best candidate for motion estimation. The difference is that the GPU algorithm uses a different approach for calculating the MVPs among the MBs to remove the interdependencies and shows a 20% speedup compared with the x264 encoder diamond search algorithm. Chen and Hang [31] parallelize the variable block size ME with fractional pixel refinement using 5 steps to maximize localized computation and reduce communication overhead between the host and GPU. Rodriguez et al. [32] parallelize the H.264 inter prediction by using CUDA to accelerate the tree structured motion compensation algorithm to generate a memory matrix that can be read in parallel to construct an approximation of the optimal macroblock mode coded partition that is needed for interprediction. The algorithm does introduce a negligible rate distortion (RD) drop but the improved speedup is one step closer towards an efficient real time video encoder.

Lee and Oh [33] proposed a highly parallel variable block size full search ME algorithm with concurrent parallel reduction (CPR) using CUDA with the aim of maximizing the number of active threads and minimizing the number of synchronization points by using CPR over the conventional PR method. Hierarchical SAD computing is used for data reuse to reduce the computation time and the proposed algorithm efficiently uses on-chip memory of the GPU to minimize long-latency of the accessed data and instructions in memory.

Rodriguez-Sanchez et al. [34] present a CUDA-based ME implementation to reduce the H.264 inter prediction complexity using data structures that can be generated and read in parallel. The algorithm was also adapted for multiple-frame reference-based ME and high video resolution and the testing results show a 99% speedup with negligible coding efficiency penalty.

Wu et al. [35] proposed a multi-level parallel and memory efficient algorithm that maps the H.264 encoder that is based on the x264 reference code to the GPU using CUDA. Almost all the entire framework of the encoder is executed on the GPU to reduce memory transfers, exploit parallelism, and improve optimizations.

Liu and Chen [36] proposed an intra-prediction parallel algorithm for the decoding phase that takes advantage of multiple GPUs to decode 100 to 1000 videos per GPU using four different optimization techniques. The GPU's effectiveness fades as the video load increases and performs nearly the same as the original algorithm for 1000 videos. This could possibly be due to the proposed algorithm not being redesigned to support parallel structures efficiently and there may have been a large communication overhead among the threads.

NVIDIA [37] has proposed a H.264 hardware-accelerated video encoding that supersedes the previous NVIDIA CUDA video encoder and an NVIDIA CUDA video decoder (NVCUVID) API library for decoding video streams MPEG-2, VC-1, and H.264 on Video Processors or

CUDA-enabled GPUs. The former uses dedicated hardware on certain classes of GPUs and can be accessed by NVIDIA encoder (NVENC) API to encode H.264 videos. The latter is part of the GPU computing SDK provided by NVIDIA.

The authors in [38] show the applicability of parallel programming models to video processing for multi-core CPU and many-core GPU technologies. Case studies from three video processing domains are demonstrated to show different optimization strategies for the parallel programming models. The authors in [39] explore efficient implementations of video coding standards on the GPU focusing mostly on the H.264 standard. Datla and Gidijala [40] port the motion JPEG 2000 reference video encoder to a CUDA-enabled GPU to parallelize the video encoder using the CUDA model and show significant speedups of 20.7 compared to the CPU implementation.

Obukhov and Kharlamov [41] propose a discrete cosine transform (DCT) that operates on 8x8 blocks in the GPU and the GPU can process the 8x8 blocks independently. This DCT algorithm can be used in image and video coding.

Xiao and Baas [42] propose a 1080p H.264/AVC baseline residual encoder that exploits fine-grained and task-level parallelization in the integer transform, quantization, and context-based adaptive variable length coding functions and can run on a programmable many-core processor. This algorithm is designed to be independent application specific hardware such as a H.264 encoder being designed to run on a CUDA-enabled GPU.

#### 2.4. Novel Contributions of This Thesis

Most of the literature regarding the parallelization of the H.264 video compression focuses on parallelizing the ME unit in the encoding process because it is the most compute

intensive operation taking as much as 80% of the total encoding time. Many variations of parallelizing the ME unit are proposed. There is also literature regarding the parallelization of the integer transform process, an approximation to the DCT transformation process, for H.264 and generic DCT transformations that would apply to many block-based compression formats including H.264 [41].

The literature regarding parallelization of video watermarking on the GPU is virtually non-existent. There is some literature regarding parallelization of image watermarking on the GPU [24-28].

The contributions to this thesis will be parallelizing the digital video watermark in the H.264 compressed domain, where the literature is non-existent for this type of watermark on a CUDA-enabled GPU. In the H.264 compressed domain, the integer transform, an approximate form of the discrete cosine transform (DCT) during the encoding process, will be parallelized on the CUDA-enabled GPU. The visible watermark will be embedded in the integer transform coefficients during the H.264 integer transformation process and will also be parallelized. The execution time of this program will include the H.264 encoding and decoding process for the MP4 container format though no parallelization was introduced during the decoding process.

So to summarize, the contributions will include:

- Embedding a digital video watermark in the H.264 compressed domain using a CUDAenabled GPU

- Parallelizing the integer transform process in the H.264 encoding phase

- Parallelizing the visible watermark embedding in the integer transform coefficients

#### CHAPTER 3

#### GENERAL PURPOSE COMPUTING PROBLEM ON GPU

#### 3.1. Overview

Currently, the CPU multi-core architecture is a multi-core system designed to work on general computing of data that is serial in nature and maintain the execution speed of sequential programs. Most CPU systems have between two and eight cores, each core supporting two hardware threads to maximize the sequential program's execution speed. The CPU architecture supports out-of-order execution, multiple instruction stream, multiple data stream (MIMD). Though two or more cores allow data-parallelism in the sense that different parts of the program can run on different cores, the cores themselves are primarily serial based. Parallel languages such as OpenMP, MPI, and MCUDA take advantage of the parallelism supported by the CPU cores. The design style of the CPU is latency-oriented design to support the requirements of legacy operating systems, applications, and I/O devices, thus putting the CPU at a disadvantage in terms of parallelism. A software programmer trying to use a parallel programming model strictly on a CPU will be at a performance disadvantage compared to a CPU-GPU execution of an application.

Modern GPUs are many-core processors that are designed to support many threads and support a throughput-oriented style. They are massive parallel processors designed to perform a massive number of floating-point calculations. They are designed to complement the CPU for numerically intensive tasks, not replace it. The GPU uses a large number of parallel threads to execute kernels while hiding long-latency arithmetic operations or memory accesses compared to a CPU, which only executes a few threads at a time. Therefore, if a program does have data portions that can be parallelized and requires a large number of threads, using the GPU is a good

option to achieve higher performance compared to just running the application on a CPU by itself. There are several parallel languages such as CUDA, OpenACC, OpenCL, and C++ AMP.

### 3.2. Modern CPU Architecture

The multi-core CPU is a Von Neumann model that is designed to support multiple cores with two threads each. The CPU supports a memory hierarchy containing thousands of registers and multiple levels of on-chip caches, usually 3 levels of caches, with non-volatile memory being at the bottom of the hierarchy. The CPU is connected to input/output (I/O) devices such as a mouse, keyboard, monitor display, and printer that allow the user to interact with the CPU. The CPU is a latency-oriented design that supports large cache memories for short-latency cache accesses, low-latency arithmetic units, and sophisticated operand delivery logic. This design comes at the expense of the supporting features taking up more chip area and using more power as opposed to proving more arithmetic units and memory access channels.

The first level on-chip cache is the smallest in size and the fastest with the last level on-chip cache being the largest in size but the slowest. Cache uses SRAM chips that are much faster than DRAM chips. The last-level on-chip cache is designed to store frequently accessed data to reduce the long-latency of the accessed data when it is stored in the DRAM. L1 caches usually are directly attached to a processor core and thus, changes to their content are not reflected in the other processor cores. Thus, a cache coherence mechanism is put in place to ensure that any changes to the contents in one L1 cache, updates the L1 caches of the other processor cores.

The main memory is DRAM, is much larger in size compared to SRAM and is much slower. The memory hierarchy of the CPU is designed to reduce the long-latency data and

instruction accesses in memory for large complex applications. The DRAM is also used to transfer data to and from a GPU device and the bottleneck for parallel computing when a large number of data transfers take place.

Non-volatile memory is memory that retains its information when the CPU is powered down. Typical non-volatile memories include hard-disk drives (HDD), solid-state drives (SSD), optical disks, and flash memory to name a few. Data is transferred to and from the processor cores and non-volatile memories via the memory hierarchy. Non-volatile memories are the largest in size in the memory hierarchy but are also the slowest, thus they are the bottleneck and form the memory wall. Thus, it is important to use faster non-volatile memories such as SSDs to see an increase in speed in the overall system.

I/O devices are needed to allow the user to interact with the CPU. The devices are used to transfer data to and from the CPU using techniques such as polling and I/O interrupts. Figure 1 shows a typical example of a multi-core processor based off the Von Neumann model.

Figure 3.1: Multi-core chip with inter-core bus

#### 3.3. Modern GPU Architecture

The GPU is a massively parallel processor designed to support many processor cores with a large number of threads to achieve a high level of performance for floating-point calculations. The GPU is a throughput-oriented design to maximize the total execution throughput of a large number of threads with an increase in arithmetic units and memory access hardware for higher memory bandwidth. The GPU follows the SIMD model for execution for parallel execution among the threads.

The GPU was redesigned during the DirectX 10-generation graphics era to support graphics and non-graphics applications. Vertex shading, fragment processing, and geometry processing are integrated into a unified fully programmable processor.

The GPU is organized as an array of streaming multiprocessors (SMs) with two SMs forming a building block and each SM containing eight streaming processors (SP) or more. Each SP has its own set of registers, ALU, and FPU. The SPs in the SM share control logic and instruction cache such as shared memory and L1/L2 caches. The SM execution resources include registers, shared memory, thread block slots, and thread slots. Each SM can support a certain number of blocks and a large number of threads. Figure 2 shows an SM example and figure 3 an SP example.

Figure 3.2: CUDA GPU streaming multiprocessor (SM)

Figure 3.3: CUDA GPU streaming processor (SP)

The CUDA memory architecture includes global memory, registers, shared memory, caches, constant memory, and texture memory. The global memory, known as graphic double data rate (GDDR) DRAM, is designed to support a high bandwidth that hides long-latency instruction and data accesses. The global memory can be read and written by threads and it communicates with the host memory for data transfers. Registers are on-chip memory that is

designed to support short access latency and higher access bandwidth. Each SP has its own local registers for local storage. Shared memory is also on-chip memory that is shared by all SPs in the SM and supports lower latency and higher bandwidth than the global memory. Shared memory is slower than registers due to memory load operations. The GPU cache is on-chip memory designed to reduce the number of accesses to the DDRAM and automatically coalesces data access patterns though the GPU cache does not currently support a cache coherence mechanism. Constant memory is located in the DDRAM though since the memory cannot be modified during kernel execution, the constant memory is cached in the L1 cache and is broadcast to a large number of threads. Though constant memory cannot be modified by a kernel function, it can be modified by the host memory. Texture memory is a special type of device memory that is cached for data locality. Memory coalescing techniques are utilized to move data from the global memory into registers and shared memories more effectively.

### 3.4. Heterogeneous CPU-GPU Architecture

The GPU is designed to be a co-processor to the CPU, not replace it. This is because the GPUs do not perform well on serial executions that the CPU is designed to perform well on. The CPU is the best choice for application tasks that are low latency and only require a few threads. The GPU is the best choice for long latency, high throughput, and parallel executable application tasks. The GPU contains many arithmetic units for handling numerically intensive tasks and high floating point calculations. Thus, a CPU-GPU computing system is needed to tackle the many tasks that are presented in the system and application execution.

The CPU contains a host interface that is setup to allow communication between the CPU and GPU. CUDA-enabled GPUs communicate with the CPU via a PCI express connection to

the host. The new AMD "Kaveri" accelerated processing unit (APU) takes it a step further and merges the CPU and GPU on the same chip using the heterogeneous systems architecture (HSA) standard. The HSA standard allows different processors including a CPU, GPU, DSPs, and others in a system to work together. It uses a heterogeneous unified memory access (hUMA) to allow the GPU and CPU to access the same memory.

## 3.5. General-purpose Computing on Graphics Processor Units

#### 3.5.1. Overview

Today's GPUs are characterized as massively parallel processors designed to perform a massive number of floating-point calculations and numerically intensive tasks. They are designed to complement the CPU for numerically intensive tasks and thus form the heterogeneous CPU-GPU architecture. The GPU is considered the most powerful parallel computing system in the PC market, thus giving the GPU a very large installed base in the marketplace. Researchers and developers have took notice of the power of the GPU and thus, became interested in harnessing the power of the GPU for general purpose computation, otherwise known as general purpose computing on the GPU (GPGPU).

### 3.5.2. Concepts and Methods

GPGPU computing follows the SIMD, single instruction multiple threads (SIMT), and single program multiple data (SPMD) models for parallel computing. In the SIMD model, the processing sends out the same instruction, via the control signal, to many processing units. Each unit is executing the same instruction at the same time to process a different set of data. In the SPMD model, the processing units are executing the same program on different sets of data and

are not required to execute the same instruction at the same time. The SIMT model specifies the execution and branching behavior of a single thread and allows the programmer to write thread-level parallel code and data-parallel code.

Thread-level parallelism (otherwise known as task-level parallelism) decomposes an application into independent tasks. Each thread processes a task using its own sets of instructions and data. Data-level parallelism is where identical instructions are performed on different data.

Decomposition is the division of a computation into smaller and manageable tasks where some or all tasks can be executed in parallel. A task is a programmer defined unit of computation. The granularity of decomposition is the size and number of tasks of a decomposed computational problem. GPGPU supports two types of granularities: coarse-grained data-parallelism and fine-grained data-parallelism. Coarse-grained data-parallelism is a small number of large tasks such as thread blocks that are composed of threads. Fine-grained data-parallelism is a large number of small tasks such as CUDA threads.

Whether using parallel programming languages such as OpenMP, MPI, OpenCL, CUDA, or MCUDA to write applications on the GPU for GPGPU or the CPU, the languages contain a few important fundamental operations that are inherent in data-parallel processing. The methods include scan, map, reduce, stream filtering, scatter, gather, sort, search, and barrier synchronization. Scan, otherwise known as all-prefix-sums, is an exclusive scan where a sum S<sub>k</sub> is the sum for all k elements between 0 and p-1. The map operation applies a kernel to a set of data, known as a stream. Stream filtering is a non-uniform reduction in the sense that it uses a set of criteria to remove certain data from a stream. Reduce is the operation where all values are reduced to a single value such as calculating the maximum value. Gather is where a large

number of data items are read from given locations. Scatter is where a large number of data items are written to given locations. The sort operation uses a criterion to sort or rearrange data. The CUDA C++ template library, Thrust, is used to perform data parallel primitives such as sort, scan, and reduction. The search operation searches for one or more items based off some criterion. Barrier synchronization is a coordination mechanism that allows threads in the same block to coordinate their activities to ensure all threads finish executing one phase of a kernel function before moving on to the next phase. This ensures no data is corrupted or overwritten by threads that finish their activities first before others finish. The above operations are done in parallel to decrease the execution time of an application.

#### 3.5.3. Bottleneck

There are many potential performance bottlenecks and resource limitations and this is dependent on the particular use of resources in the application. The most looked at bottleneck is the communication that takes place between the CPU and GPU via the memory. There are other limitations such as registry, thread, and thread-block limitations. For example, declaring two additional automatic variables in a kernel function increases the registry count by two in every thread. If the registry count exceeds the maximum number of registries an SM may support, the CUDA runtime system reduces the number of blocks assigned to each SM and thus, reduces the thread count. This ultimately reduces parallelism and performance in an application. The performance cliff is where an increase in one resource has an unintended decrease in another resource, thus reducing the parallelism and performance in an application as described in the above example. Several tests will need to be performed to determine the application's

bottleneck. Using debugging and profiling tools such as NVIDIA visual profiler can be used to identify the bottlenecks and optimize the application

#### CHAPTER 4

#### PARALLEL COMPUTING AND PROGRAMMING ON A CUDA-ENABLED GPU

#### 4.1. Overview

Today's GPUs are fully programmable massively parallel processors designed to perform a massive number of floating-point calculations and achieve higher performance on non-graphics applications using parallel operations. Parallel computing solves a problem much quicker compared to sequential execution, assuming a large portion of data can be parallelized. Various languages including the CUDA language and libraries such as Thrust, have been developed to take advantage of the parallelism that is inherent in the multi-core CPUs and accelerative devices such as the GPU.

# 4.2. Languages and Libraries

Many parallel processing languages and libraries are designed to improve the performance of parallel computing in non-graphics applications. Programming the GPU just ten years ago required direct knowledge of the GPU architecture and low-level programming techniques. Languages such as CUDA have made it much easier for the non-graphics programmer because they abstract the hardware, alleviate having to learn the graphics API, and allow the programmer to focus on the application at hand. On the other hand, the programmer does have to write their code for parallel execution instead of sequential execution with the exception being OpenACC, a compiler directive language. Also, for the application developer to achieve a high-performance parallel program with an improved speedup, knowledge of the GPU hardware architecture is needed to make better use of the software programming tools such as CUDA.

# 4.2.1. CUDA

CUDA is a high-level language that is an extension to the C language and is used to program GPU-accelerated applications. It is a parallel computing platform and programming model designed to allow the non-graphics programmer to take advantage of the high performance of the GPU for parallel code execution. CUDA is used in many fields related to cryptography, watermarking, video coding, bioinformatics, computational chemistry, computational fluid dynamics, electronic design automation, and imaging and computer vision to name a few. CUDA is designed to work with GPU-accelerated libraries such as Thrust, a parallel algorithms library similar to the C++ standard template library (STL) for defining typegeneric parallel algorithms, and to work with GPU directives such as OpenACC, a programming standard that provides a collection of compiler directives to run parallel programs on accelerator devices such as APUs, GPUs, and many-core processors.

# 4.2.1.1. Scalability

As opposed to parallel programming for the CPU, parallel programming on the GPU using a parallel processing language is designed to allow scalability as the GPU core count increases. This is due to the design of the GPU parallel programming model.

For example, CUDA follows a GPU parallel programming model that uses fine-grained data parallelism techniques with efficient threading support for graphics and parallel computing. The CUDA threads allow the exploitation of data parallelism inherent in a program. Efficient thread scheduling in particular allows a much larger amount of data parallelism to be exploited than the underlying hardware resources would allow on the machine the software program is running on. This is important for CUDA software programs that run on many different types of

CUDA-enabled GPUs that have different amounts of hardware resources and will have a long software life cycle. Since the CUDA program is based on threads to expose the data parallelism inherent in a software program using fine-grain data-parallelism techniques, the CUDA program just needs to be written once and the software program will be able to take advantage of the hardware resources ranging from a few cores to hundreds of cores to a further increase of cores in the next generations to come in CUDA-enabled GPUs. This provides a form of transparent and portable scalability.

The CUDA parallel programming model is in contrast to the parallel programming models for the CPU that use course-grained data-parallelism to process application tasks. Currently, the CPU cores available in a consumer PC range between four to eight. The CPU-based parallel program is designed to assign application tasks to each core. As the core count increases during each new generation of CPU cores, the application needs to be rewritten to take advantage of the extra hardware resources. Also, if an application is designed to run on four CPU cores and the application will need to run on a CPU architecture with only two CPUs, the application will also need to be rewritten. Thus, the application using the current CPU parallel programming model is not scalable.

# 4.2.2. OpenACC

The OpenACC application program interface is a programming standard that provides a collection of compiler directives to run parallel programs on accelerator devices such as APUs, GPUs, and many-core processors and simplify parallel programming on heterogeneous CPU-GPU architectures. The standard is designed to support multiple levels of parallelism found in an accelerator such as a GPU. OpenACC is similar to OpenMPI with some of the OpenACC

members serving in the OpenMP standards group. The difference between OpenMPI and OpenACC is that OpenMPI is used to only specify directives for the CPU whereas OpenACC is for accelerative devices.

The simplicity of OpenACC is that programmers do not need to modify their existing code or learn a new syntax and style of programming to support a parallel application. The programmer simply adds compiler directives, known as #pragma directives, to their sequential code where the directives can be ignored if the program is run on a non-OpenACC compiler. The programmer does not need to specify the details of data transfer between host and accelerator memories, thread scheduling, kernel launching, and parallelism mapping since the OpenACC compiler and runtime handle these details.

In the OpenACC execution model, the target machine includes a host and an attached accelerator. There are multiple execution units at the outermost level and within each execution unit there are multiple threads, with each thread executing vector operations. The execution units and the threads within each execution unit run in parallel. Also, OpenACC is designed to work in conjunction with CUDA during program execution.

The OpenACC memory model treats the host memory and accelerator memory as separate with the assumption that each memory is not able to access the other directly. The model uses similar constructs from CUDA with regards to memory allocation, copying, and deallocation before kernel launches and transferred results from device to host. The difference is that in CUDA, this needs to be specified explicitly by the programmer whereas OpenACC does this automatically.

## 4.2.3. C++ AMP

The C++ accelerated massive parallelism (C++ AMP) parallel programming model is an open specification developed initially by Microsoft to allow software programmers to design applications to run on data-parallel hardware while hiding the system intricacies of the underlying hardware. This offers portability, better performance, and better productivity for the application as it can be run on different current hardware and future generation hardware from different manufactures without the application having to be rewritten. In certain cases, the application may need to take advantage of the system intricacies and C++ AMP has features to support this.

The C++ AMP model contains a rich subset of the C++ language for data parallel computations that run on the co-processor and the model works in conjunction with the C++ language that runs on the host. This allows for a small learning curve for software developers that are familiar with C++.

# 4.2.4. OpenCL

The open computing language (OpenCL) parallel programming model is an open specification designed to run on heterogeneous computing systems such as the CPU, GPU, digital signal processors (DSPs), field-programmable gate arrays (FPGAs), and other coprocessors as well. OpenCL is maintained by the non-profit Khronos Group and has been adopted by many organizations including NVIDIA, AMD, Intel, and Apple to name a few. The model is very similar to CUDA and the syntax and operations are very similar as well. One can learn CUDA and easily adopt the OpenCL language in a day or two.

## 4.3. Programming Model

CUDA is a parallel programming model designed to allow non-graphics software developers to write parallel applications for the heterogeneous CPU-GPU architecture. The model supports a hierarchy of threads, thread blocks, barrier synchronization, and atomic operations.

The programming unit in CUDA is the thread and all threads in a grid execute the same kernel function. Each thread is unique and a coordinate system is used to identify each thread so that the appropriate portion of data can be assigned to that particular thread. The thread organization supports a two-level hierarchy. The first level starts with a grid that is organized into thread blocks up to three dimensions. In the second level, each thread block is organized into threads up to three dimensions. The grid and blocks can have different dimensions. Each thread block contains x threads that are multiples of 32 and each thread block subdivided in warps, the unit of thread scheduling in an SM, with each warp containing 32 threads each. The warp uses the SIMD model and thus, all threads in a warp execute the same instruction. The threads within a thread block coordinate their execution using barrier synchronization so all threads finish their current phase before moving to the next phase. The threads can also share data using shared memory. Figure 4 shows an example of a CUDA 2-Dimensional (2,2,1) grid organization where the grid is organized as (x,y,z).

Figure 4.1: 2-Dimensional (2,2,1) grid organization

The kernel configuration is specified with the grid dimensions and block dimensions before execution. To execute, one or more thread blocks are assigned to each SM. Each SM has a limit on the available resources assigned to it. These limitations include thread blocks, threads, registers, and shared memory. Increasing usage on one resource such as the number of threads, will decrease the usage on another resource, such as thread blocks. Each SM is assigned multiple warps, though only a subset can be executed at any given time. The reasoning for this is to hide long latency operations. While a warp is waiting for a result, another warp can be scheduled to execute, thus hiding the long latency operation.

When writing CUDA applications, the programmer needs to be aware of the ratio of floating point calculations performed for each memory access, known as the compute to global memory access (CGMA) ratio. To increase this ratio and thus increase floating-point performance, a programmer needs to optimize the program using algorithmic techniques that make important use of the limited resources at hand.

# 4.4. Applications

Numerous non-graphics applications have been developed on CUDA-enabled GPUs in the academic and business world. Many of the applications being developed are used to showcase the power of the GPU while other applications being developed are to be used for the specific needs at hand. Fields that are utilizing the GPU for application purposes include cryptography, digital watermarking, video coding, bioinformatics, computational chemistry, computational fluid dynamics, electronic design automation, and imaging and computer vision. The Nvidia CUDA website showcases a number of applications ranging from different fields to show the usefulness and power of the GPU for these types of applications. Many researchers from academia have shown significant speedups across many of these applications when porting the compute intensive areas of these applications to the GPU.

#### CHAPTER 5

#### DIGITAL VIDEO WATERMARK

#### 5.1. Introduction

In today's world, there are many digital multimedia applications such as DVDs, TV broadcasting, video-based web applications, and recording to name a few. Today's digital technologies allow content sharing, lossless and high fidelity copying, ease of editing and modifications, and compression. These convenient technologies also introduce the need for digital rights management tools to provide copyright protection, content authentication, and integrity. Many content providers and copyright owners are leery of piracy of their digital products and hence are interested in protecting their IP and illegal copying of their digital products. One solution is the digital watermark, a process of embedding additional data into digital multimedia objects to produce a watermarked multimedia object for the purposes of copyright protection and content authentication. The watermark can later be detected or extracted to prove the content owner of the multimedia object. This technology is provided on top of data encryption.

Watermarking shares its roots in steganography, the art of hiding the existence a secret message to protect against detection. Watermarking has a clear distinction from steganography in that the hidden data is robust against removal techniques. These removal attacks can either be intentional or unintentional.

Various watermarking algorithms have been proposed in the literature for image, audio, video, and text multimedia objects. Since videos are used heavily in the entertainment industry and video surveillance, this thesis focuses on digital video watermarks. Video watermarking algorithms are the most challenging, computationally intensive, and time consuming

watermarking algorithms. Real-time encoding of video streams using a digital watermarking scheme is extremely computationally intensive. What complicates this matter even more is the video compression format of the video the digital watermark is being inserted into, such as the H.264/MPEG-4 AVC (or H2.64 for short). Video compression is needed for videos that involve storage and/or transmission such as movies and streaming video. Being able to support high video quality and high throughput while minimizing distortion with the embedded watermark in a reasonable amount of time is a daunting task. Fortunately, many of the operations of the digital video watermark do show a high degree of parallelism and hence these operations can be computed on a GPU.

## 5.2. Watermark Framework

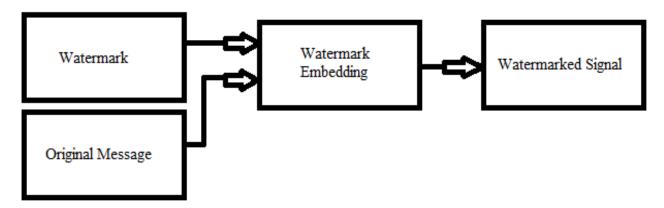

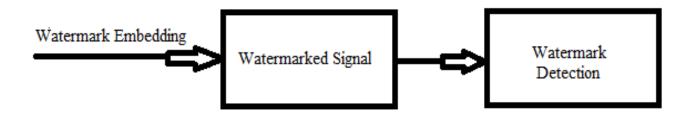

Watermark techniques can be classified using the criteria shown in figures 5.1, 5.2, 5.3, 5.4, and 5.5.

Figure 5.1: Human perception

Regarding figure 5.1, there are two types of watermarks based on human perception: visible and invisible watermarks. A visible watermark is an opaque monochrome or translucent

image embedded as an overlay on an image or video frame. This can be a company logo, copyright notice, or digital photo consisting of text. The more popular invisible watermark embeds a binary image, random or pseudorandom number into the image or video frame and shares the characteristic of being imperceptible to the human eye.

Figure 5.2: Robustness

A robust watermark's performance is determined by being able to withstand intentional and unintentional attacks such as processing techniques and manipulative processes. Robust watermarks are used in applications for copyright protection. A semi-fragile watermark is able to resist simple transformations such as compression that preserve the image or video contents while failing to resist malignant transformations that alter the image or video contents. Its applications involving image authentication are generally used in a court of law to determine if the image or video has been tampered. A fragile watermark fails even the slightest transformation and is used to determine tamper detection in a court of law. A fragile watermark is also another form of image authentication.

Figure 5.3: Watermark domain

The spatial domain involves slight modifications to the values of the pixels. This is the least computationally intensive of the two and is easier to implement. The caveat is that it is less robust to attacks. In the frequency domain, the multimedia object goes through a transformation, DCT for example, and the watermark is embedded in the transform coefficients by modifying them slightly to represent the watermark.

Figure 5.4: Watermark extraction and detection process

A blind (or public) watermarking extraction scheme is the most challenging but most popular type of watermarking scheme. It requires neither the original data nor the original watermark to extract the watermark from the watermarked object. A semi-blind (or semi-private) watermarking detection scheme does not require the original multimedia object but does use the watermarked multimedia object and original watermark for detection of the watermark in the watermarked multimedia object. A non-blind (or private) watermarking scheme is the most robust but has limited application use. These systems require at least the original multimedia object and they consist of two types. Type I systems use the original multimedia object and watermarked multimedia object to determine where the watermark is hidden at so it can be extracted. Type II systems use the original multimedia object, watermarked multimedia object, and the original watermark for detection of the watermark in the watermarked multimedia object. The limited applications for semi-blind and blind schemes include copyright protection in a court of law setting and copy-control.

a) Watermark Encoder: Watermark Embedding

## b) Watermark Decoder: Watermark Detection

c) Watermark Decoder: Watermark Extraction

Figure 5.5: Watermark encoder and decoder

The encoder is a function that embeds the watermark data into the host multimedia object. The type and location of the data is dependent on whether the watermark is visible or invisible, whether the host object is audio, text, image, or video, and what compression scheme if any is used for the host object. For example, an invisible-robust watermark for an H.264 compression format may include a copyright message watermark embedded in the luminance DCT coefficients before the quantization phase. The decoder function is the opposite of the encoder and it can used for detection or extraction. An extraction scheme will extract the watermark bits from the watermarked object, such as a robust watermark. A detection scheme will detect if a watermark is present, such as a fragile watermark.

# 5.3. Security and Attacks

Intentional or unintentional modifications to the watermarked object have the potential to remove the watermark or obscure the watermark data, and thus make it difficult for the watermark to be successfully extracted or detected. Any modification to a watermarked object is known as an attack, whether it is intentional or unintentional. There are many forms of attacks such as geometric, signal processing, specialized attacks, cryptographic attacks, and system-

based attacks. The security of the watermark embedding algorithm depends on the watermark being able to withstand the attack either by making it too computationally difficult to remove or the removal causes too much distortion in the audio, image, or video. In the case of fragile or semi-fragile watermarks, being able to defend against watermark counterfeit attacks is another security measure to be considered.

Geometric attacks include rotation, scaling, translation, cropping, affine transforms, mosaicing, and other related image and video editing operations. These types of attacks are specifically for image and video watermarks. These attacks are meant to cause distortion in the watermarked object and thus, make it very difficult for the watermark to be detected or extracted.

Signal processing attacks include lossy compression, quantization, requantization, dithering, adaptive filtering, denoising, collusion attacks, and stochastic attacks involving watermark estimation and noise addition. These types of attacks either attempt to remove the watermark such as stochastic attacks or attempt to add additional signal noise to the watermarked object such as lossy compression.

A specialized attack requires direct knowledge of the watermark method. Desynchronization, luminance, and chrominance attacks are two such specialized attack methods. Cryptographic attacks use similar attacks in cryptography to breach the security of the watermarked object. A system based attack would be a watermark counterfeit attack.

## 5.4. Video Watermarking

#### 5.4.1. Overview

Several papers in the literature have proposed many video watermarking methods for various video formats and video compression schemes. Many of the algorithms proposed center

around invisible watermarks since these types of watermarks deal with copyright protection and image authentication. Video watermarks have some similarities with image watermarks in that the watermark bits are embedded in an image. Though in the case of video watermarks, there are multiple images represented as frames that are sampled over different time periods. Thus, this adds additional computational complexity as watermark bits must be computed for different frames or in some cases in block-oriented compression schemes, different blocks. The additional computational complexity also increases the time it takes to embed and extract (or detect) the watermark.

#### 5.4.2. H.264/MPEG-4 AVC

H.264/MPEG-4 AVC is the industry standard for video compression in many multimedia applications and thus, it is essential to provide copyright protection and protect intellectual property (IP) in H.264 compressed videos. Many watermarks in the literature have been proposed for the H.264 video compression. This remains a challenging task because of the high-coding efficiency and the redundancy removal during the encoding process. Robust video watermark data is generally embedded in redundant data that minimizes distortion and is robust against attacks. The efficient removal of the redundant data in the H.264 video compression makes this a challenging task.

## 5.4.2.1. Watermark Embedding and Extraction and Detection

Digital video watermarking methods for the H.264 compression format is classified into four methods depending on where the watermark is placed during video compression: before compression, before quantization, after quantization, and during entropy encoding. Also, any of

the four groups can take place on a video bit stream, during the decoding and encoding of a compressed stream, or on the compressed stream itself. Embedding the watermark in a video bit stream before compression can make the digital watermark itself sensitive to video compression and thus, cause distortion to the compressed video. Many of H.264 watermarking algorithms presented in the literature take place before quantization. The general structure involves embedding the watermark in the DCT coefficients in the luma and chroma components of the macroblock. This is the structure that will be used in this thesis. Embedding watermark data after quantization entails embedding the watermark data in the quantized transform coefficients. Watermarks can also be embedded during the entropy coding phase in the Context-adaptive variable length coding (CAVLC) mode or context-adaptive binary arithmetic coding (CABAC) mode.

Watermark extraction and detection take place after the video has been decompressed. Watermark detection involves detecting whether the watermark bits are present are not in a secret location using an optional key if one was used in the original embedding algorithm. Watermark extraction requires locating the watermark secret location and extracting the watermarked bits from the watermarked object.

## 5.4.2.2. Security and Attacks

The H.264 video watermark is designed to be robust against signal processing and hostile attacks. It is also designed to be hidden in a secret location that can only be accessible by authorized parties and it is generally designed to be imperceptible (invisible watermark). There is a large literature detailing various signal processing attacks such as the Gaussian noise, bit-rate reduction, contrast enhancement, frequency filtering, and non-linear filtering attacks that the