# SECURE AND ENERGY EFFICIENT EXECUTION FRAMEWORKS USING VIRTUALIZATION AND LIGHT-WEIGHT CRYPTOGRAPHIC COMPONENTS

Satyajeet Nimgaonkar

Dissertation Prepared for the Degree of DOCTOR OF PHILOSOPHY

# UNIVERSITY OF NORTH TEXAS

August 2014

APPROVED:

Mahadevan Gomathisankaran, Major Professor Saraju P. Mohanty, Co-Major Professor Krishna Kavi, Committee Member Song Fu, Committee Member Barrett Bryant, Chair of the Department of Computer Science and Engineering Costas Tsatsoulis, Dean of the College of Engineering Mark Wardell, Dean of the Toulouse Graduate School Nimgaonkar, Satyajeet. <u>Secure and Energy Efficient Execution Frameworks</u> <u>Using Virtualization and Light-Weight Cryptographic Components</u>. Doctor of Philosophy (Computer Sciences and Engineering), August 2014, 108 pp., 16 tables, 28 figures, 78 numbered references.

Security is a primary concern in this era of pervasive computing. Hardware based security mechanisms facilitate the construction of trustworthy secure systems; however, existing hardware security approaches require modifications to the micro-architecture of the processor and such changes are extremely time consuming and expensive to test and implement. Additionally, they incorporate cryptographic security mechanisms that are computationally intensive and account for excessive energy consumption, which significantly degrades the performance of the system.

In this dissertation, I explore the domain of hardware based security approaches with an objective to overcome the issues that impede their usability. I have proposed viable solutions to successfully test and implement hardware security mechanisms in real world computing systems. Moreover, with an emphasis on cryptographic memory integrity verification technique and embedded systems as the target application, I have presented energy efficient architectures that considerably reduce the energy consumption of the security mechanisms, thereby improving the performance of the system. The detailed simulation results show that the average energy savings are in the range of 36% to 99% during the memory integrity verification phase, whereas the total power savings of the entire embedded processor are approximately 57%. Copyright 2014

by

Satyajeet Nimgaonkar

## ACKNOWLEDGMENTS

This doctoral research would not have been possible without the contributions of a number of people, to whom I am greatly indebted.

To my major professor, Dr. Mahadevan Gomathisankaran for his guidance, support, and patience throughout this research. He provided an exceptional environment for research and the endless brainstorming sessions helped me sharpen my analytic skills. His motivation, enthusiasm and immense knowledge are the driving force behind the successful completion of this research.

I would also like to thank my co-major professor, Dr. Saraju P. Mohanty and rest of the committee members, Dr. Krishna Kavi and Dr. Song Fu for their encouragements, insightful comments and critiques.

To my wife and best friend Pooja, for her sustained support, encouragement, patience, unyielding love, and sacrifice. She has guided me through the highs and lows in life and her words have often motivated me to do better and achieve bigger things. She has been the rock upon which the foundation of my life is built. I thank her for gifting me our beautiful son Ishan, who has brought a sense of calm, stability, and good luck in our lives.

My parents and grand parents have been instrumental in my success in higher education. They inculcated in me the importance of education. Their prayers and blessings have been a great source of inspiration and motivation to me. To my sister for her love and support. To my mother-in-law for all her belief and support in me and my decisions.

Most of all, I would like to thank the almighty God for His grace, blessings, and guidance.

# TABLE OF CONTENTS

|        |        |                                                    | Page |

|--------|--------|----------------------------------------------------|------|

| ACKN   | OWLE   | DGMENTS                                            | iii  |

| LIST ( | OF TA  | BLES                                               | vii  |

| LIST ( | OF FIC | URES                                               | viii |

| CHAP   | TER 1  | OVERVIEW                                           | 1    |

|        | 1.1.   | Problem Statement and Motivation                   | 2    |

|        | 1.2.   | Novel Contributions of this Dissertation           | 3    |

|        | 1.3.   | Organization of this Dissertation                  | 4    |

| CHAP   | TER 2  | VIRTUALIZATION BASED SECURE FRAMEWORK (vBASE)      | 5    |

|        | 2.1.   | Introduction                                       | 5    |

|        | 2.2.   | vBASE Testing Framework                            | 6    |

|        |        | 2.2.1. Secure Architecture Plugin Interface (SAPI) | 7    |

|        |        | 2.2.2. Secure Application                          | 8    |

|        |        | 2.2.3. Event Trigger Mechanism                     | 8    |

|        |        | 2.2.4. Monitor                                     | 9    |

|        |        | 2.2.5. Controller                                  | 9    |

|        |        | 2.2.6. Framework Functioning                       | 10   |

|        | 2.3.   | vBASE Execution Frameworks - SecHYPE and CTrust    | 11   |

|        |        | 2.3.1. Introduction                                | 11   |

|        |        | 2.3.2. SecHYPE Framework                           | 12   |

|        |        | 2.3.3. CTrust Framework                            | 13   |

|        | 2.4.   | vBASE Prototype Implementation                     | 15   |

|        | 2.5.   | vBASE Analysis                                     | 20   |

|      |        | 2.5.1. Security Analysis                                 | 20 |

|------|--------|----------------------------------------------------------|----|

|      |        | 2.5.2. Performance Analysis                              | 21 |

|      | 2.6.   | Previous Related Research                                | 24 |

|      |        | 2.6.1. Virtualization-Based Security Approaches          | 24 |

|      |        | 2.6.2. Cloud-Based Security Approaches                   | 28 |

|      |        | 2.6.3. Software Security Approaches                      | 31 |

|      | 2.7.   | Conclusion                                               | 32 |

| CHAI | PTER 3 | MEMORY INTEGRITY VERIFICATION IN EMBEDDED SYSTEMS        | 34 |

|      | 3.1.   | Introduction                                             | 34 |

|      | 3.2.   | Memory Integrity Property                                | 36 |

|      | 3.3.   | Attacks on Memory Integrity                              | 37 |

|      | 3.4.   | Verification Mechanisms                                  | 38 |

|      | 3.5.   | Proposed Memory Integrity Verification Framework         | 39 |

|      | 3.6.   | Related Previous Research                                | 43 |

|      | 3.7.   | Conclusion                                               | 46 |

| CHAI | PTER 4 | MEM-DnP: DETECT AND PROTECT MECHANISM                    | 47 |

|      | 4.1.   | Introduction                                             | 47 |

|      | 4.2.   | MEM-DnP Architecture                                     | 48 |

|      | 4.3.   | Disjoint Hash Trees                                      | 50 |

|      | 4.4.   | Relation between Process Variations in Sensors and $V_T$ | 51 |

|      | 4.5.   | Experimental Evaluation                                  | 57 |

|      |        | 4.5.1. Simulation Framework                              | 57 |

|      |        | 4.5.2. Baseline Energy Consumption                       | 58 |

|      |        | 4.5.3. MEM-DnP Energy Consumption                        | 60 |

|      | 4.6.   | Conclusion                                               | 62 |

| CHAI | PTER 5 | TSV: TIMESTAMPS VERIFICATION MECHANISM                   | 69 |

|      | 5.1.   | Introduction                                             | 69 |

|      |        |                                                          |    |

|                                                            | 5.2.   | TSV A                   | rchitecture                                      | 70 |

|------------------------------------------------------------|--------|-------------------------|--------------------------------------------------|----|

| 5.3. Experimental Evaluation                               |        | mental Evaluation       | 72                                               |    |

|                                                            |        | 5.3.1.                  | Simulation Framework                             | 72 |

|                                                            |        | 5.3.2.                  | Baseline Energy Consumption                      | 73 |

|                                                            |        | 5.3.3.                  | TSV Energy Consumption                           | 75 |

|                                                            |        | 5.3.4.                  | Theoretical Evaluation for TSV Mechanism         | 80 |

|                                                            |        | 5.3.5.                  | Overhead Evaluation of TSV Mechanism             | 82 |

|                                                            | 5.4.   | Conclu                  | sions                                            | 86 |

| CHAPTER 6 HASH FUNCTION-LESS MEMORY INTEGRITY VERIFICATION |        |                         | 88                                               |    |

|                                                            | 6.1.   | Introdu                 | action                                           | 88 |

|                                                            | 6.2.   | Hash F                  | unction-Less MIV Architecture                    | 88 |

|                                                            | 6.3.   | Experimental Evaluation |                                                  | 92 |

|                                                            |        | 6.3.1.                  | Simulation Framework                             | 92 |

|                                                            |        | 6.3.2.                  | Power Dissipation in MIV                         | 94 |

|                                                            |        | 6.3.3.                  | Power Savings in Hash Function-Less Verification | 95 |

|                                                            | 6.4.   | Conclu                  | sion                                             | 97 |

| CHAF                                                       | PTER 7 | CONC                    | LUSION                                           | 98 |

| BIBLIOGRAPHY                                               |        |                         | 100                                              |    |

# LIST OF TABLES

| Table 3.1. | Energy Consumption of Encryption Algorithms [53]                      | 36 |

|------------|-----------------------------------------------------------------------|----|

| Table 3.2. | Energy Consumption of Hashing Algorithms [53]                         | 36 |

| Table 4.1. | Cache Configurations                                                  | 58 |

| Table 4.2. | Baseline Simulations showing Total Hash Invocations and the Average   |    |

|            | Hash Rate                                                             | 59 |

| Table 4.3. | Average Energy Savings for Disjoint Tree $= 16$                       | 66 |

| Table 4.4. | Average Energy Savings for Disjoint Tree $= 64$                       | 67 |

| Table 4.5. | Average Energy Savings for Disjoint Tree $= 128$                      | 68 |

| Table 5.1. | Cache Configurations                                                  | 73 |

| Table 5.2. | Hash Accesses at different Levels                                     | 74 |

| Table 5.3. | TS Cache Configurations                                               | 76 |

| Table 5.4. | Geometric Mean of Weighted Averages of Hash Invocations               | 80 |

| Table 5.5. | Energy Savings in Timestamps Approach                                 | 80 |

| Table 5.6. | Energy Savings vs. Area Overhead in TS Cache                          | 83 |

| Table 5.7. | Energy Savings/Area Overhead (E/O) factor for TS Cache Configurations | 85 |

| Table 6.1. | Embedded Processor Specifications                                     | 93 |

| Table 6.2. | Total Power savings in an Embedded Processor                          | 97 |

# LIST OF FIGURES

| Figure 2.1. | vBASE Testing Framework                                      | 7  |

|-------------|--------------------------------------------------------------|----|

| Figure 2.2. | SecHYPE Framework                                            | 13 |

| Figure 2.3. | CTrust Architecture                                          | 14 |

| Figure 2.4. | Time required for Secure Channel Invocations                 | 23 |

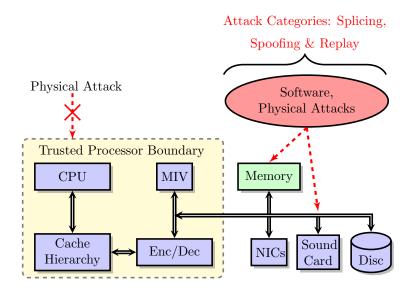

| Figure 3.1. | Attacks on Memory Integrity                                  | 37 |

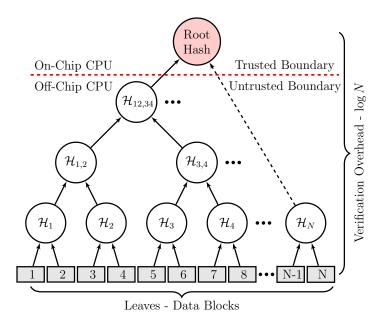

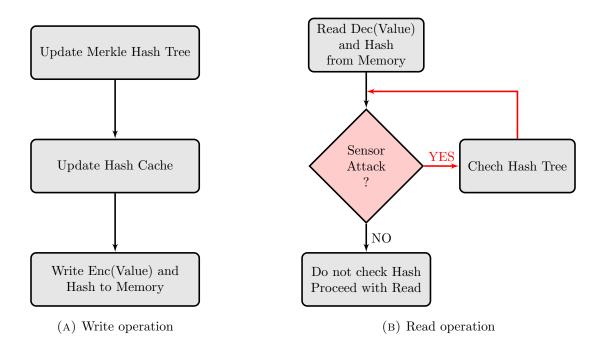

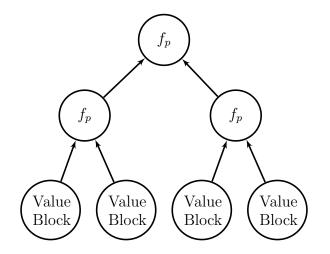

| Figure 3.2. | Merkle Hash Tree                                             | 39 |

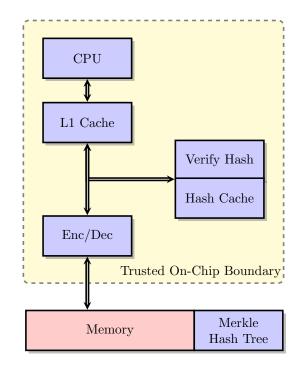

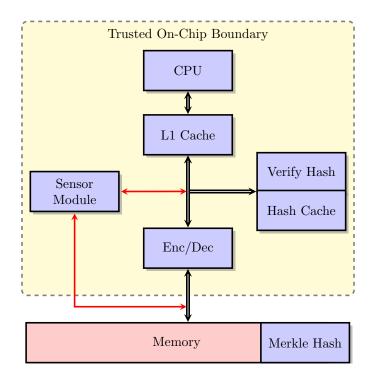

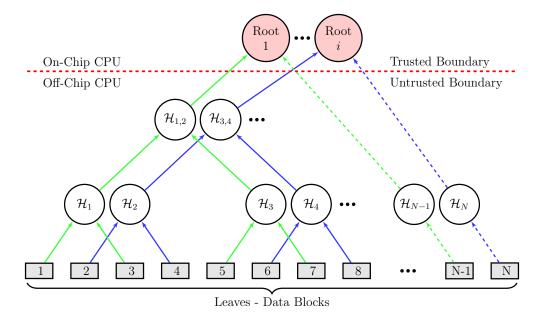

| Figure 3.3. | Memory Integrity Verification Framework                      | 40 |

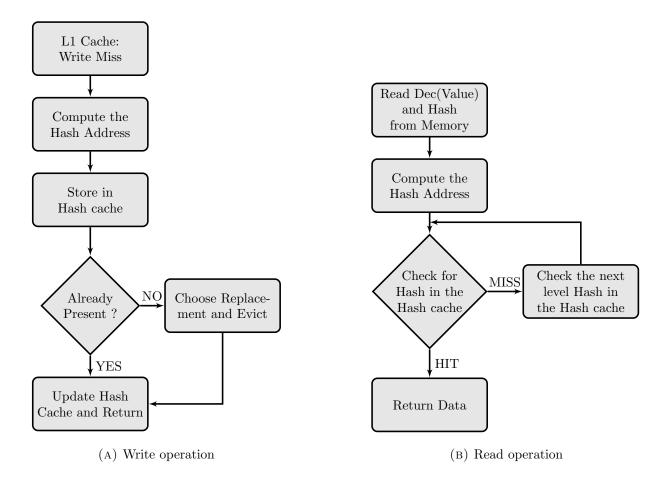

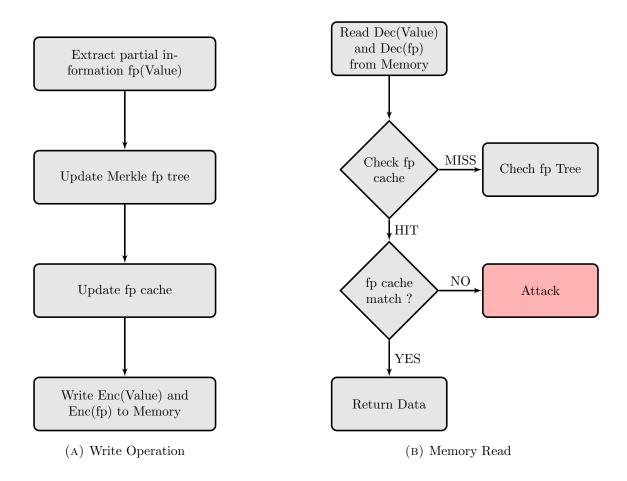

| Figure 3.4. | Memory Integrity Verification Operations                     | 41 |

| Figure 4.1. | MEM-DnP Architecture                                         | 49 |

| Figure 4.2. | Memory Operations in MEM-DnP Architecture                    | 50 |

| Figure 4.3. | Disjoint Hash Tree                                           | 51 |

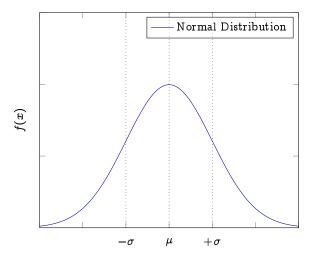

| Figure 4.4. | Gaussian Distribution Curve                                  | 53 |

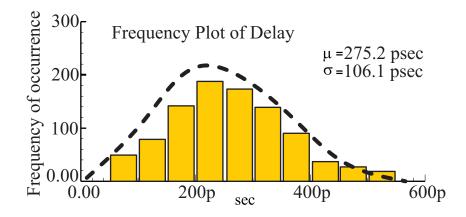

| Figure 4.5. | Example: Propagation Delay PDF in a 2-input NAND Gate        | 55 |

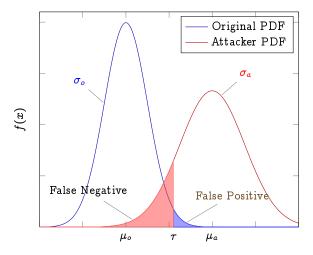

| Figure 4.6. | Tolerance of Sensor as compared to Attacker PDF              | 57 |

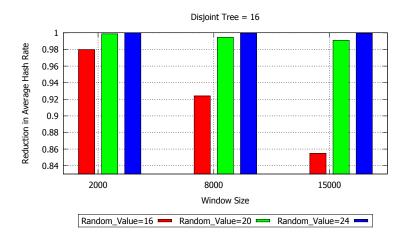

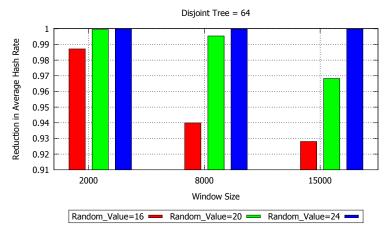

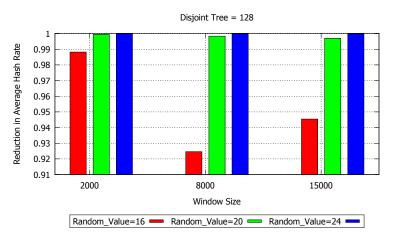

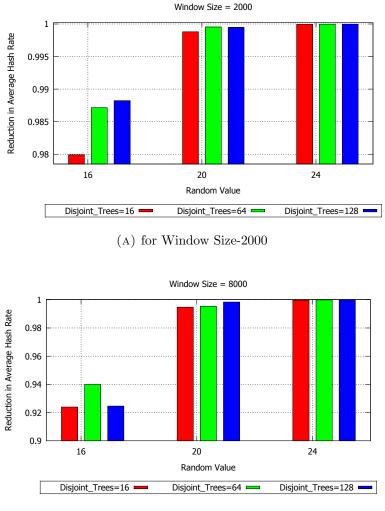

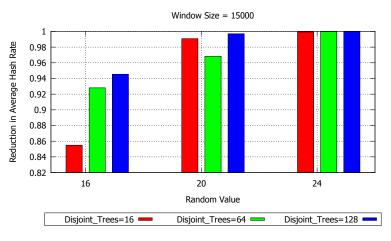

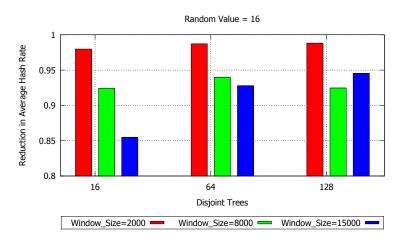

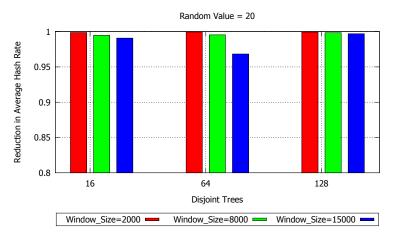

| Figure 4.7. | Reduction in Average Hash Rate for different Disjoint Trees. | 63 |

| Figure 4.8. | Reduction in Average Hash Rate for different Window Sizes.   | 64 |

| Figure 4.9. | Reduction in Average Hash Rate for different Random Value.   | 65 |

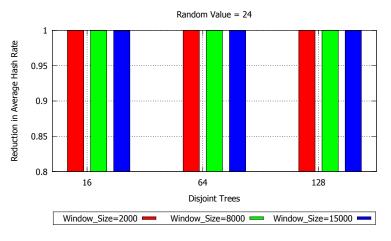

| Figure 5.1. | Timestamp Verification Architecture (TSV)                    | 70 |

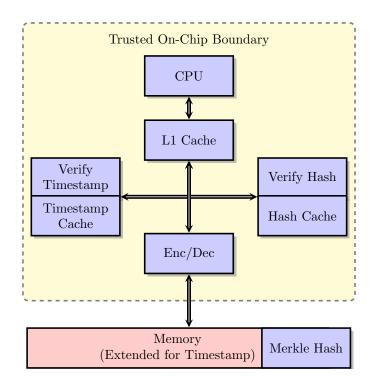

| Figure 5.2. | Memory Operations in TSV Architecture                        | 71 |

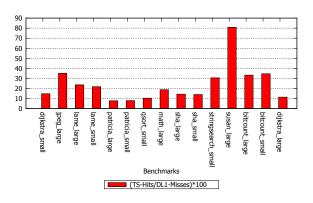

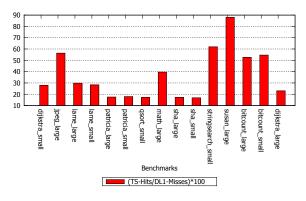

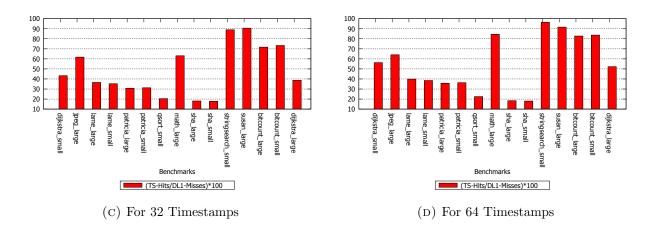

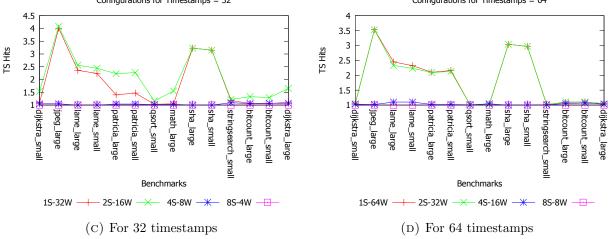

| Figure 5.3. | Average percentage of TS Hits                                | 77 |

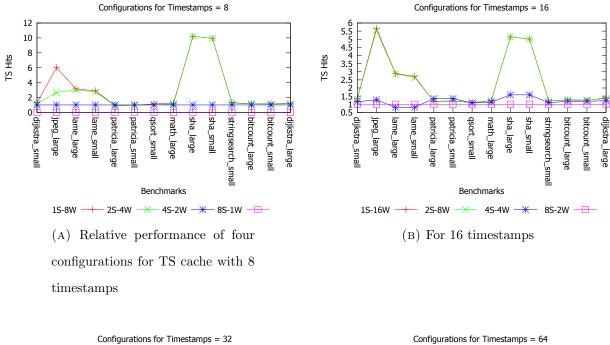

| Figure 5.4. | Relative performance of various TS cache configurations      | 78 |

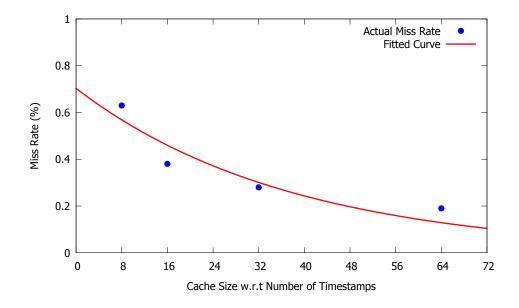

| Figure 5.5. | Miss Rate vs. TS Cache Size in terms of Number of Timestamps | 82 |

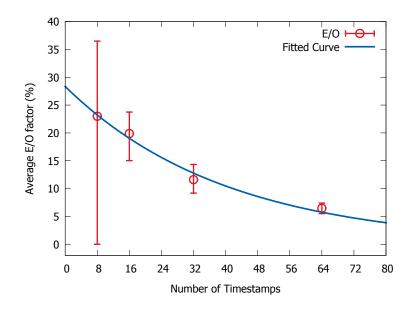

| Figure 5.6. | Average E/O factor for each TS cache                         | 86 |

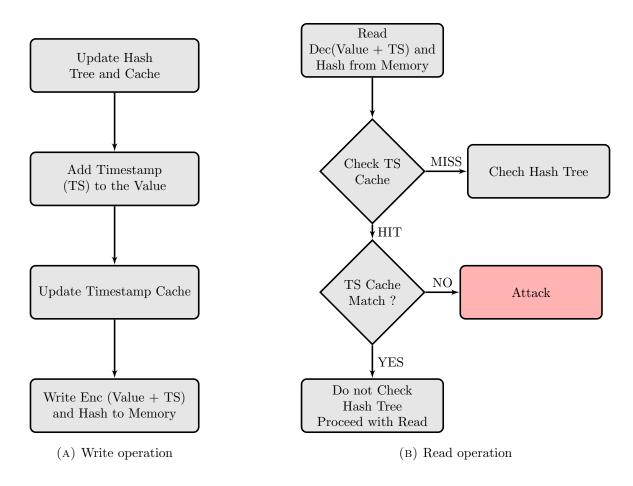

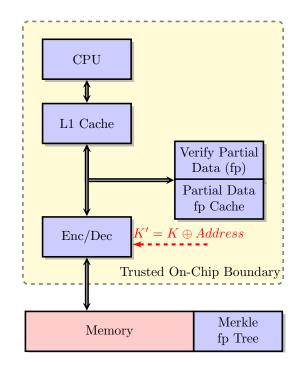

| Figure 6.1. | Hash Function-Less Verification Architecture                 | 89 |

| Figure 6.2. | Memory Operations in Hash Function-Less Verification Architecture | 90 |

|-------------|-------------------------------------------------------------------|----|

| Figure 6.3. | Merkle $f_p$ Tree                                                 | 90 |

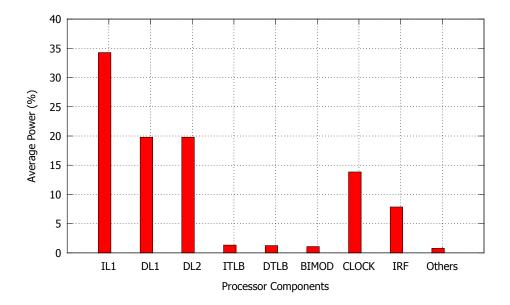

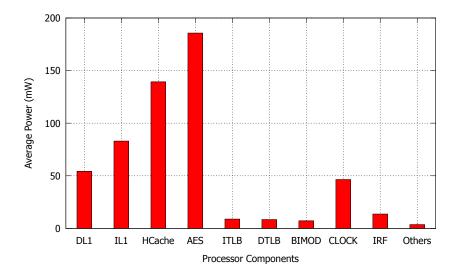

| Figure 6.4. | Power consumption in various components of a Processor            | 93 |

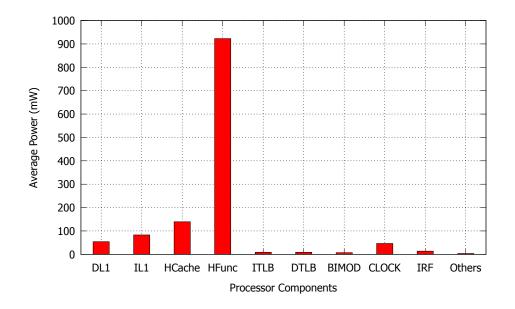

| Figure 6.5. | Power consumption of Hash Cache and Hash Function in a Processor  | 95 |

| Figure 6.6. | Power consumption of AES-128 Encryption Function in a Processor   | 96 |

#### CHAPTER 1

#### **OVERVIEW**

The current trends in technology have allowed computing systems to evolve into complex forms. Personal computers, smart-phones, PDAs, network sensors, and network routers etc., have become ubiquitous in this era of computing. As the dependence on these systems increase, so also does the sensitivity of information stored in them. This information may include confidential personal data like secret passwords, credit card numbers and bank account numbers etc. Thus information security has now become imperative so as to prevent these systems from leaking out this critical information to unauthorized entities.

In general, computer security aims at providing confidentiality, integrity, and availability to computing systems. Confidentiality is breached when information is accessible to an unwanted and unauthorized entity. This entity could be a human, a software program or another computing system. Similarly, integrity is infringed when information is modified by such an entity and availability is broken when this entity succeeds in making the host computing system not serve legitimate user requests.

There are two approaches to provide security in a computing system. The first is to include software protection mechanisms like software obfuscation, watermarking, encryption, isolation, and so forth. The root of trust is entrusted in the security of the operating system (OS). However commodity OS are significantly large with huge code base and are often prone to security vulnerabilities. The most common software attack that exploits the software vulnerabilities in application code and OS is the Buffer Overflow Attack [11]. Software solutions share their memory with other softwares and the OS that could potentially contain a vulnerability and hence provide an entry point to an attack. Moreover, this kind of security cannot protect a system from a physical attack. Thus the security they provide is inadequate. The second solution is more effective. The idea is to add some hardware security mechanisms that can provide tamper evident and tamper resistant environment [44, 35]. These include secure processor architectures like ABYSS [71], AEGIS [67], Arc3D [22], XOM [38], and

HIDE [78] that propose modifications to the processor architecture. Typically they employ hardware Encryption/Decryption and Memory Integrity Verification (MIV) mechanisms to protect the confidentiality and preserve the integrity of the applications. Thus the root of trust is delegated in the security provided by the secure hardware architectures. Hardware support for security facilitates the construction of trustworthy secure systems. However, there are two significant issues that hinder the adoption of secure hardware architectures. These issues are described in Section 1.1 and form the crux of this research in terms of problem definition and motivation.

#### 1.1. Problem Statement and Motivation

- The secure hardware architectures require changes to the micro-architecture of the processor and such changes are extremely time consuming and expensive to test and implement. This is where, we derive our first motivation. A virtualization layer can be used to test the security of an architecture. This provides a time and performance efficient alternative to actual hardware testing. Also, once an architecture is successfully tested for its security, the entire virtualized setup can be used to secure applications running on a cloud service platform.

- The second issue with these architectures is that they incorporate cryptographic security mechanisms that are computationally intensive and account for excessive energy consumption. While this may not be a big issue in desktop computers and large servers, it certainly becomes a huge problem in embedded systems. Embedded systems are highly resource constrained. Most of these devices are battery powered and it is essential to have minimal energy consumption in-order to achieve high speed and performance. Therefore, the motivation is to propose secure but light weight cryptographic alternatives so that the energy overhead imposed is minimal. In this research, the emphasis is specifically on reducing the energy overhead imposed by the MIV mechanism in embedded processors.

1.2. Novel Contributions of this Dissertation

The major contributions of this dissertation are as follows.

- The first contribution is to provide a platform to test the hardware security mechanisms in a time and cost effective manner. For this, we have proposed the Virtualization Based Secure Framework (vBASE) that leverages the power of virtualization technology to realize hardware security mechanisms inside the virtualization layer. This makes the testing process flexible, time & cost efficient and comparatively easy as against actual hardware testing. This is demonstrated in the proposed vBASE Testing framework.

- We then present the vBASE Execution framework SecHYPE and CTrust with a primary goal to prove the practicality of secure hardware architectures, once they are thoroughly tested. The inclusion of hardware security inside the hypervisor leads to the design of a secure hypervisor framework SecHYPE. With cloud computing as the target application, we propose the Cloud Trust architecture CTrust that deploys the SecHYPE framework to provide root of trust and security to the applications running in the cloud.

- The focus of the research then shift towards the performance overhead imposed by the hardware security mechanisms. We have concentrated specifically on reducing the energy consumption of the cryptographic MIV mechanism. The first technique that we have proposed is the Memory Detect and Protect mechanism (MEM-DnP), which relies on a sensor module to detect any memory based attack on the system. The MIV operation is only carried out in an event of an anomaly i.e., when the fluctuations exceed the threshold value  $V_T$ . The simulation results show that the average energy savings are in the range of 85.5% to 99.998% during the integrity verification phase.

- The second technique is the Timestamps Verification (TSV) mechanism. This scheme is based on the principle of locality and uses timestamps to uniquely identify the memory block written to the memory. The simulation results show that the

energy savings are in the range from 36% to 81% during the integrity verification phase.

- Finally, we present the Hash Function-Less Verification mechanism to completely eliminate the performance cost of invoking a Hash Function during the MIV. The simulation results prove that this mechanism reduces the power consumption of an embedded processor by 57.24%. This is a significant improvement considering most embedded devices are battery powered.

- 1.3. Organization of this Dissertation

The rest of this dissertation is organized as follows. Chapter 2 presents our proposed Virtualization Based Secure Framework (vBASE). There are two flavors of vBASE framework — Testing framework that is used to test the security of a given secure hardware architecture and an Execution framework that constitutes the SecHYPE and CTrust, which are used for secure and trustworthy application execution in cloud computing platforms. Chapter 3 briefly discusses the cryptographic memory integrity verification (MIV) mechanism and describes the proposed MIV architecture and an algorithm to calculate total number of hash invocation required during the execution of a program. Chapter 4 describes our first energy efficient MIV solution known as the Memory Detect and Protect (MEM-DnP). Here, we have demonstrated how on-chip sensors can be used to detect a memory based attack on an embedded system. The MIV is executed only when there is an attack on the system. This leads to significant energy savings as exhibited in the simulation results. Chapter 5 presents our second energy efficient MIV solution, called the Timestamps Verification (TSV) mechanism. This scheme exploits the principle of locality to reduce the number MIV invocations, thereby reducing the energy consumption of the processor. Finally, Chapter 6 describes the Hash Function-Less Verification mechanism, where the aim is to completely eliminate the cost of invoking a hash function during the MIV process, thus significantly reducing the power consumption of the processor. Chapter 7 presents the conclusion of this dissertation.

#### CHAPTER 2

## VIRTUALIZATION BASED SECURE FRAMEWORK (VBASE)<sup>1</sup>

#### 2.1. Introduction

The recent years have seen a wide scale growth, adoption, and popularity of the virtualization technology (VT) [68], to provide efficient and cost-effective usage of expensive hardware. VT not only increases hardware utilization through server consolidation but also provides benefits for application development and testing [70]. VT introduces a software abstraction layer or virtualization layer (virtualization software) between the hardware and the operating system, thus decoupling them from each other. This software abstraction layer is known as the virtual machine monitor (VMM) [61] or the hypervisor. A VMM/hypervisor allows the user to create multiple virtual machines (VMs) on a single physical hardware platform, each capable of running an OS and its applications. A virtualization software emulates the underlying hardware to provide a known interface for the OS and applications to run on. The virtual CPU, memory, storage, and the introspection APIs in a VMM/hypervisor can be modified to mimic any given secure hardware architecture. This makes it easier, time, and cost efficient to test the security of a hardware architecture as compared to on-chip testing. Besides, the combination of hardware secure architectures with the virtualization software can strengthen the security of the hypervisors. They can then be used to provide trust and security to the applications running in cloud computing systems. With this motivation, we have presented two different designs of the vBASE framework: vBASE Testing and vBASE Execution framework.

The vBASE framework is implemented on top of the XEN VMM/hypervisor [5], an open-source virtualization software. Therefore our framework uses some of the components already provided by XEN. However, it is important to stress that the security mechanisms implemented in the vBASE framework are generic to any virtualization software and so the

<sup>&</sup>lt;sup>1</sup>Parts of this chapter have been previously published, either in part or in full, from [34] with permission from IASTED and Actpress, [50] with permission from IEEE and [51] with permission from Academy of Science.

vBASE framework can be easily ported to another VMM/hypervisor. Since vBASE adheres to the structure of XEN VMM, it is worthwhile to discuss briefly, the architecture of XEN before presenting the vBASE framework. The XEN VMM/hypervisor is the basic abstraction layer (virtualization software) that resides directly on the hardware below the OS. It emulates the underlying hardware and is responsible for CPU scheduling and memory partitioning in order to allow multiple VMs to run on a single hardware platform. XEN controls the execution of all the VMs running on it, however it has no knowledge of networking, external storage devices, video, or any other common I/O functions found in a computing system. The XEN structure defines two types of VMs: Domain 0 (DOM 0) and Domain U (DOM U). Domain 0 is a privileged VM that has the capability to access physical I/O resources and communicate with other VMs running on the system. In its simplest form, a Domain 0 is a modified Linux kernel, that must be running on all XEN platforms before any other VM could be started. Domain U is an unprivileged VM that is provided to the users to host their applications.

The rest of this chapter is organized as follows. Section 2.2 describes the vBASE Testing framework and its core software components. Section 2.3 presents the vBASE Execution framework that constitutes the secure hypervisor framework - SecHYPE and the cloud trust architecture - CTrust. The prototype implementation of vBASE framework is presented in Section 2.4 followed by detailed analysis in Section 2.5. Section 2.6 details the previous related research. Finally Section 2.7 presents the conclusion of the vBASE research project.

#### 2.2. vBASE Testing Framework

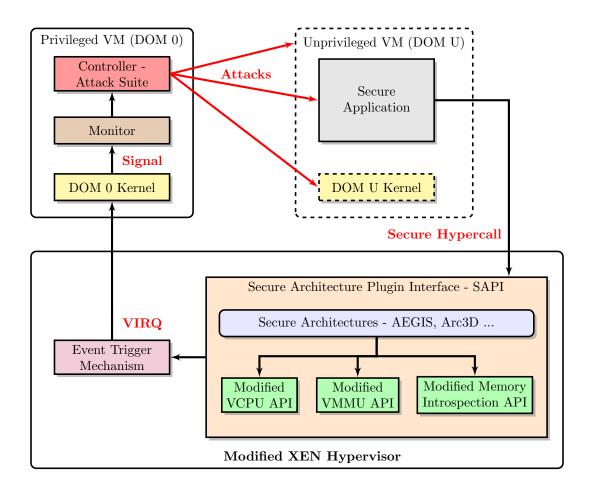

The primary goal of the proposed vBASE Testing framework is to provide a test bench to evaluate the security capabilities of given hardware architecture. This provides a time and cost efficient alternative to on-chip hardware testing. The framework is shown in Figure 2.1. The main components of this framework are - secure architecture plugin interface (SAPI), secure application, event trigger mechanism, monitor and the controller.

FIGURE 2.1. vBASE Testing Framework

### 2.2.1. Secure Architecture Plugin Interface (SAPI)

The SAPI is a generic interface exposed by the vBASE framework to embed any secure architecture within the XEN VMM. SAPI is a collection of APIs which are used to modify the virtual CPU (VCPU), virtual memory management unit (VMMU) and provide memory introspection functions into the modified components of XEN. Secure architectures are typically changes to the CPU and memory of the hardware which facilitates secure execution and isolation of a process. These components are available as software modules in XEN. These modules are modified to resemble a particular secure architecture. As shown in Figure 2.1, the SAPI primarily has three components: modified VCPU API, modified VMMU API and modified memory introspection API. The modified VCPU API has all the set of functions which modifies the Virtual CPU provided by XEN. These modifications include providing encryption and decryption capabilities to the processor, add additional secure registers, modify or implement new cache memories etc. The modified VMMU has set of functions which enhance the existing virtual memory management unit provided by XEN. These changes include switching on/off the conventional virtual memory layout of the OS, encryption and decryption functions for main memory and adding additional access restrictions to the secure process memory pages. The modified memory introspection API enhances the memory monitoring features provided by XEN.

#### 2.2.2. Secure Application

This is a special process whose data needs to be protected from attacks on the system. This process is aware of the security mechanisms provided by the secure architecture plugged in to the vBASE framework. Secure applications or processes protect their confidential data by storing them in specialized protected memory regions.

#### 2.2.3. Event Trigger Mechanism

Event trigger provides a mechanism to initiate inter-VM communication. Traditionally, XEN provides some mechanisms and tools like split device driver, xenstore, grant tables, and ring buffers to carry out inter-VM communication. However the primary drawback of these mechanisms and tools is that they need the support from DOM U kernel to initiate communication. The vBASE framework assumes all DOM U kernels to be untrustworthy and vulnerable to attacks. Hence instead of using the traditional mechanisms, a new hypercall mechanism independent of the DOM U kernel, has been developed. A hypercall works similar to a system call in an OS. It is an interrupt, INT 82h in XEN that is used to switch the control between the kernel and the XEN hypervisor. The hypercall interrupts the processor and is trapped in XEN using the hypercall handler functions. A new mechanism was developed to interrupt the processor from ring-3 of a DOM U VM. This is developed by using the CPUID instruction. The CPUID is meant to report processor features to userlevel applications. A custom code — 0x92h was developed as an argument for the CPUID instruction that can trap into the XEN VMM from DOM U user-space. At that point, the control is transferred to the hypercall handler which will issue a virtual interrupt (VIRQ) to the DOM 0. VIRQ is a software interrupt, notified by setting up a bit in the Virtual CPU data structure present in XEN. It is used for communication from XEN to the VM kernel.

#### 2.2.4. Monitor

It is a program running in the DOM 0 that receives notifications about the secure application, through the Event Trigger mechanism. It is responsible for monitoring critical events pertaining to the secure application and detect any possible attacks on it. It contains a monitoring script, which is a collection of watch events and actions to be performed when a particular event occurs. During secure execution, monitoring is carried out at multiple layers such as, application layer: secure and normal applications, OS layer, hypervisor layer and the secure architecture layer. In the application layer, common events that are monitored are API function calls, library calls, network API calls and messages encapsulating secret keys etc. At the OS layer, monitoring is done for software interrupt handlers, virtual memory mappings, memory accesses, I/O accesses, process scheduling and so on. At the hypervisor layer, common events are instruction execution, interrupt handlers, memory translations, page fault mechanism and so forth. Finally, the events monitored at the secure architecture layer are secure instruction entry and exit points, secure page fault mechanism, accesses to secure memory locations and registers etc.

#### 2.2.5. Controller

The secure hardware architectures must be rigorously tested against various attacks. The Controller is a comprehensive attack suite made up of host and network based attacks. During the execution of the secure application, the controller mounts attacks on different layers of the system stack. A vulnerability at any layer in the stack is exploited to generate an attack scenario. At the application layer, an attack is attempted to breach the confidentiality and integrity of process's code and data, inject malicious code during function calls, exploit library calls, intercepting network traffic etc. At the OS layer, attacks attempt to modify the virtual memory mappings, values passed to software interrupts and system calls, kernel level data structures, I/O messages and so forth. At the hypervisor layer, attacks are aimed to tweak the inter-VM memory mappings, parameters passed to hypercalls and interrupts and I/O data packets etc. Finally, the plugged-in secure architecture is also attacked by trying to read/modify its secure registers, modifying its essential data structures, attempt to leak its cryptographic keys and so on.

#### 2.2.6. Framework Functioning

The first step of the functioning is to plug-in a secure architecture by using the generic interface provided by the SAPI. Once this is done, the VCPU, VMMU and virtual memory introspection functions are appropriately modified to align with the plugged-in secure architecture. All the information pertaining to the security mechanisms provided by the secure architecture is then reported to the Monitor through the Event Trigger mechanism. The Monitor, thus now has complete visibility and understanding of the secure regions within the secure architecture. The secure application can then start executing in an unprivileged VM. A secure application identifies its critical confidential data and then transitions to secure execution state. In the proposed framework, this is achieved by invoking a secure hypercall enter\_vbase. Once the secure application invokes this hypercall, the secure architecture and the Monitor are informed about the secure execution of the application. Its now the responsibility of the secure architecture to protect the confidential data of the application, while the Monitor is responsible for tracking all the necessary events related to the application. While the application is executing securely, the Monitor informs the Controller to conduct a series of attacks on the secure application. The secure application can exit secure execution by invoking the exit\_vbase hypercall. At this instant, the Monitor stops tracking the events while the Controller suspends its attacks. Once the secure application terminates, all the events recorded by the Monitor are logged. This log serves as a benchmark to judge the effectiveness of the security mechanisms provided by the secure architectures.

#### 2.3. vBASE Execution Frameworks - SecHYPE and CTrust

This Section presents the second type of vBASE framework called the Execution framework. The target application of this framework is cloud computing. It has been designed and developed with an intention to provide trust and security to the applications executing in cloud computing platforms.

### 2.3.1. Introduction

Cloud computing [46], envisions universal access to a shared pool of configurable resources such as compute, storage, network, and software. In the recent years, cloud computing platforms have procured great success due to its cost effectiveness, flexibility, increased storage, and elasticity. It provides on-demand computing, where the customer has complete control on its services to the finest granularity and can tailor them based on their needs. Cloud computing allows consolidation of resources thus enabling new applications. Currently e-commerce, on-line auctioning companies, travel agencies and other such services use clouds to provide services to their users.

In-spite of several advantages, the adoption of cloud computing is impeded by critical security issues. The National Institute of Standards and Technology (NIST), has identified security as a primary concern in cloud computing. Security issues in cloud arise at different levels: infrastructure level, software service level and user level. Prior research [9, 64, 10, 56] exemplify how security vulnerabilities in cloud are exploited by motivated attackers. A recent global information security survey, Into the Cloud, Out of Fog [28] conducted by Ernst & Young in November 2011 states that 72% of respondents see an increasing level of risk due to increased external threats in cloud computing.

Cloud computing currently relies heavily on VT to virtualize the CPU and storage resources so as to meet its elastic demands. VT provides security by isolating the execution of each OS and its applications in a VM. Thus a security breach in one VM does not affect the working of other VMs. However, isolation security is inadequate to protect an application from a malicious OS or another application running in the same VM. Thus additional security measures have to be incorporated in the virtualization softwares to provide security in cloud computing platforms. The security challenges in cloud computing can be reduced to, how to establish root the trust and to protect the confidentiality and integrity of the applications in the cloud. A VMM can be used as the root of trust. Given a small footprint of the VMM, it would be reasonable to verify its correctness and thus the security of a VMM. As shown in Section 2.2, it is possible to plugin a secure hardware architecture inside a VMM and this modified secure VMM can be used to provide security to the applications executing in the cloud. Here, the VMs are run on top of the modified secure VMM. Thus the root of trust for the applications is relegated in the security of the VMM.

#### 2.3.2. SecHYPE Framework

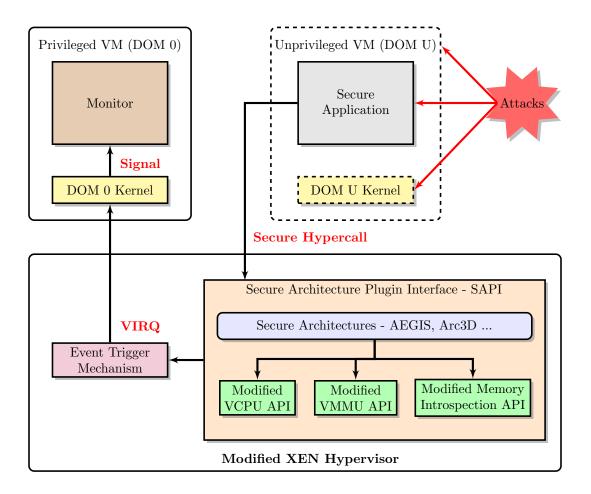

The idea behind the SecHYPE framework is to bolster the security features of a virtualization software, so that it can be used as a root of trust for user applications running in the cloud. The main advantage of this approach is that the underlying hardware need not be modified in order to accommodate additional security features. We have already demonstrated in Section 2.2 that it is feasible to realize and implement secure hardware architectures inside the XEN VMM. Once, a particular hardware architecture is thoroughly tested and proven to be secure, can be ported in cloud computing platforms to provide security to the applications. We call this secure hypervisor as the SecHYPE framework, shown in Figure 2.2.

The SecHYPE framework is very similar to the vBASE Testing framework in terms of its software components and overall operation. The only exception is the Controller component. The Controller is a software component of vBASE framework that is used to launch attacks on secure Applications during the testing phase. It is a consolidated attack suite that inter-operates with the Monitor program to thoroughly test the security features of the secure hardware architecture under test. However, there is no need to launch attacks on applications during the executon phase and therefore, the Controller is not present in the SecHYPE framework. The rest of the components and framework functioning remains the same as in the vBASE testing framework.

FIGURE 2.2. SecHYPE Framework

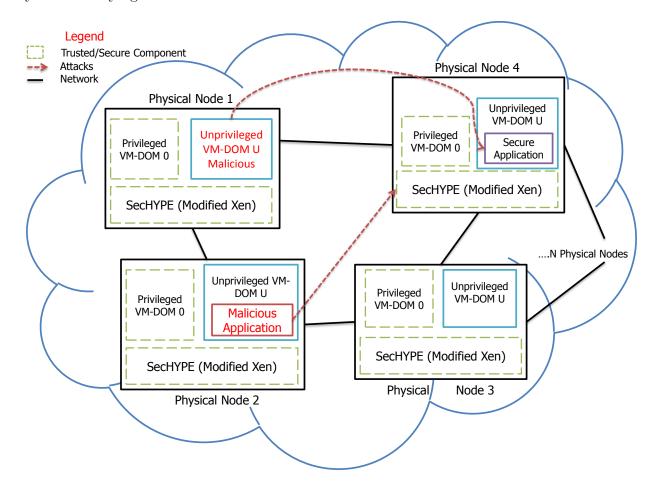

## 2.3.3. CTrust Framework

The intuition behind the CTrust architecture is to deploy the SecHYPE framework in a cloud environment to provide security and root of trust to the applications running in the cloud. Figure 2.3 shows the proposed CTrust architecture. This represents a prototype implementation of a private cloud built on top of the SecHYPE framework. In this architecture, the cloud is composed of a cluster of real computing machines known as the physical nodes. The nodes could be easily added to the cloud based on its load. Each node is connected to each other via a physical network. The CTrust architecture is implemented on XCP 1.0 [72] that contains XEN hypervisor version 3.4.x and CentOS with 2.6.32.x Linux kernel. Since the SecHYPE framework is developed by modifying the XEN hypervisor, it is possible to replace the original XEN hypervisor in XCP 1.0 with the SecHYPE framework. The CTrust architecture is implemented with one HVM unprivileged VM. A HVM domain is a type of XEN VM which is capable of running unmodified OS (e.g. Windows). The HVM domain has been chosen to implement CTrust for two reasons. The first reason was to present a solution which doesn't require changes to the OS. The second reason is that the HVM guests have great paging support available in XEN API. However, it is important to stress that the same solution would be easier to port to PV domains also. The primary reason for this is that a PV domain runs a modified OS which is aware of the changes done by the underlying VMM.

FIGURE 2.3. CTrust Architecture

A secure application can be under an attack from multiple avenues in a cloud environment. The attacks can be (but are not limited to) network based attacks, attacks from an external malicious VM or even parent VM and even attacks from applications running in the same VM. The secure hardware architecture inside the SecHYPE framework is responsible for protecting against these attacks. The security strength of the hardware architecture determines the overall security of the cloud platform. If an attack is beyond the security realms of the hardware architecture, then that particular attack would succeed. Hence it is the decision of the cloud provider to determine the level of security desired and to choose the most suitable hardware architecture. There are several advantages of the CTrust architecture: it does propose and enforce a new security mechanism, but instead empowers the cloud provider with the flexibility of choosing the most favorable security mechanism. It enables the cloud vendor to provide security assurance to its clients, thus honoring the service level agreements (SLAs). And finally, a client application can utilize the security mechanisms exposed by this architecture and achieve security during the epoch of application execution.

#### 2.4. vBASE Prototype Implementation

This section presents a prototype implementation of the vBASE framework. The overall process is described in Algorithm 1. It is important to emphasize that the prototype implemented is just a small instance of framework. This prototype serves as a proof of concept to prove the effectiveness of the framework. This implementation includes a very simple secure hardware architecture functionality and not a fully functional architecture. The implementation is not as powerful as the framework itself as its primary goal is to show the readers how the various components of vBASE work with each other during secure execution. The secure application runs in a HVM DOM U and once it begins execution, it allocates a chunk of memory for secure data/variables. Later the secure process allocates memory from this secure chunk, to the secure data/variables. The implemented secure architecture protects this chunk of memory from any memory based attacks. To achieve this, the secure process copies the virtual address of the secure chunk of memory and passes it to the hypervisor. The size of the secure chunk of memory is aligned with that of the memory pages. It is relatively easier to mark the pages read-only than making individual memory locations read-only.

#### Algorithm 1 Secure Process Execution

- 1: Secure application/process begins execution.

- 2: It allocates secure memory buffer.

- 3: Transmit virtual address (VA) of secure memory buffer through a ring3\_hypercall.

- 4: Receive VA in hypercall handler in the hypervisor.

- 5: Compute guest frame number (GFN) for the VA.

- 6: Compute machine frame number (MFN) for the GFN.

- 7: MFN is marked read-only.

- 8: Dispatch VIRQ to the DOM 0 kernel.

- 9: Dispatch a SIGNAL from DOM 0 kernel to the Monitor program.

- 10: Monitor prints the events to user.

The primary advantage of vBASE implementation is that, it eliminates the OS in making the secure process's memory read-only. To achieve this, it uses the CPUID instruction. All other instructions except CPUID are short circuited to the OS's interrupt table and do not directly trap in to the VMM. The CPUID, on the other hand, traps directly into the VMM. This instruction was originally intended to report processors features to ring-3 software applications. It takes various parameters and reports different features of the processor depending on those parameters. A custom parameter: 0x92, has been added to the CPUID instruction. This parameter is passed in the eax register and takes the virtual address of the secure memory in the ebx register. The secure application code containing the CPUID instruction is trapped in the VMM. The VMM recognizes the operand 0x92 and passes the virtual address to the SAPI component. In the SAPI component, the virtual address is translated into Guest Frame Number (GFN) and eventually into Machine Frame Number (MFN). This MFN is then made read-only and a Virtual Interrupt (VIRQ) is sent to the DOM 0. The VIRQ is handled by the kernel module in the DOM 0 and it notifies the Monitor through a Signal. The Monitor prints the confirmation message to the user and the secure process resumes its execution. Since the secure memory pages are protected by the VMM, even overwriting requests from OS will be ignored. The xm daemon will report

```

char secure_mem[PAGE_SIZE] secure_memory __attribute__((

__aligned__(PAGE_SIZE)));

```

LISTING 2.1. Secure Memory Allocation

```

long * secret_key=(long *) secret_mem;

*secret_key = 654321;

```

LISTING 2.2. Secret Key Linked to Secure Memory

if any such attempts to overwrite the read-only (secure) pages is done.

We now present the source code implementation of vBASE. In the listing 2.1, a chunk of memory: secure\_mem of PAGE\_SIZE is allocated and the beginning of the chunk of the memory is aligned to beginning of a page.

In listing 2.2 we have declared a long pointer - secret\_key and type casted the char buffer pointer to an long pointer (secret\_mem). The secret\_key is assigned the address of the secure\_memory. Now the contents of the address contained in secret\_key will be stored in the chunk of memory allocated in listing 2.1.

The address of the secret key is to be protected. To protect it we will make it read only. In listing 2.3, we pass the secret key to the hypervisor using ring3\_hypercall. The ring3\_hypercall is an assembly macro which takes the virtual address of the secure memory and a command integer as parameters. In the macro these parameters are passed as operands for the CPUID instruction. The CPUID instruction will then trap into the VMM. Along with the virtual address we send a command to the SAPI module in the hypervisor which decides the action to be performed on the virtual address. Initially we will send a PROTECT command. This will protect the virtual address by making the corresponding Machine Frame Number read-only. Originally XEN allows hypercalls to be done only through privileged interface in the OS. But we have solved this problem by using CPUID instruction. We call this mechanism as ring3\_hypercall, which stands for hypercalls made from ring3 of DOM U.

Hypercalls are trapped into the VMM, thus giving VMM control. The blocks of VMM

```

int ring3_hypercall(unsigned long gva, int cmd)

{

int ret;

__asm__ ___volatile__(

"cpuid"

: "=a"(ret)

: "a"(0x92), "b"(gva), "c"(cmd)

:"cc", "edx"

);

return ret;

}

unsigned long gva=(unsigned long) secret_key;

ret = ring3_hypercall(gva, PROTECT);

```

LISTING 2.3. Pass the virtual address to the VMM

where hypercalls are handled is called as hypercall handler. The Guest Virtual Address (GVA) is received in the hypercall handler and Machine Frame Number (MFN) is computed which is the hardware machine's RAM frame number. The function that computes MFN needs Guest Frame Number (GFN) as the argument. So first we computed GFN using paging\_gva\_to\_gfn() function. This GFN is then passed on to the gmfn\_to\_mfn where MFN is calculated. This MFN is marked read-only by the XEN's in built function. This function requires previous type (read-only, write-able) of the MFN. Hence we first invoke a function which returns the old type of the MFN. The MFN is passed along with the old type and new type (p2m\_ram\_ro). This will update the MFN type in XEN's tables. Any further requests to overwrite the pages identified by the MFN are dropped by XEN. Attempts for trying to write to the read-only MFN are reported to DOM 0 through Xend. This is shown in listing 2.4 below.

In listing 2.5 the code sends a global VIRQ to the DOM 0. In XEN VIRQ's are

```

struct vcpu *v=current;

struct domain *d=v->domain;

p2m_type_t old_type;

mfn_t mfn;

gfn=paging_gva_to_gfn(current, gva, &pfec)

mfn=gfn_to_mfn(d, gfn, &old_type);

p2m_change_type(d, gfn, ot,p2m_ram_ro);

```

LISTING 2.4. Translate GVA to MFN and mark MFN read-only

send\_guest\_global\_virq(dom0, VIRQ\_VBASE); bind\_virq\_to\_irqhandler(VIRQ\_VBASE,0,vbase\_handler,NULL,NULL, 0);

LISTING 2.5. Dispatch VIRQ from XEN

handled by the guests as interrupts. So we need to bind the VIRQ to an IRQ Handler. After the VIRQ is populated from the hypercall handler, the DOM 0 is resumed and an interrupt (dynamically bound by the kernel) is issued. This will trap the control into the IRQ handler bound earlier.

In listing 2.6 the task\_structure of the Monitor process is found using find\_task\_by\_pid function provided by the kernel (note that pid of the monitor can be sent through a system call or by writing to kernel filesystems). After finding the task\_struct a signal is issued to monitor process. This will notify that the virtual address of the secure process has been made read-only.

Therefore it is evident from the prototype implementation, that the vBASE frame-

# find\_task\_by\_pid\_type(PIDTYPE\_PID, monitor\_pid); send\_sig\_info(SIG\_VBASE, &info, task\_structure);

LISTING 2.6. Dispatch a SIGNAL to the Monitor

work detects any unwanted modification to the secure application memory. These modifications can result from malicious applications, VMs, vulnerable OS and network channels. The plugged-in secure hardware architecture, for implementation purposes, employs an encryption and integrity verification mechanism. This allows vBASE to detect malicious modifications and eventually discard them.

#### 2.5. vBASE Analysis

In this Section, we present a formal analysis of the vBASE framework in terms of its security and performance.

#### 2.5.1. Security Analysis

The vBASE framework is designed and implemented in XEN hypervisor. Therefore its architecture conforms to the overall structure of XEN. Nonetheless, the security mechanisms available in vBASE are developed using software and hardware utilities that are universal to any virtualization software. In XEN, the hypervisor layer and the Domain 0 (DOM 0) are at higher privilege level as compared to Domain U (DOM U), where user applications are executed. The vBASE framework exploits this design by placing the Monitor and Controller components inside the privileged DOM 0. The application that needs to be protected is run inside the DOM U. The first assumption in vBASE is that there are no preexisting vulnerabilities in the XEN hypervisor itself. The XEN hypervisor is shipped with a modified Linux kernel that is by default loaded at system. It is assumed that this Linux kernel does contain vulnerabilities that can be exploited by potential attackers. Though, in such scenarios it is reasonable to assume that a TPM can be used to verify the integrity of the XEN hypervisor. With regards to the execution frameworks – SecHYPE and CTrust, it is reasonably considered that the cloud provider itself is not malicious. Also, it is expected that the secure application that needs to be protected, is itself not malicious. It is important to emphasize that vBASE by its own does not propose any secure architecture. It is a reconfigurable framework to test the security of a hardware architecture and then export the most suitable hardware architecture into the cloud to provide root of trust to the applications running in the cloud.

Finally it is also essential to discuss about cryptographic key management in the vBASE framework. This may not be important in the testing framework, but certainly becomes crucial in the execution framework. The secure hardware architectures integrated within the SecHYPE framework typically include an Encryption and a Memory Integrity Verification security mechanisms to provide confidentiality and preserver integrity of the data. These mechanisms require cryptographic keys for computing cyphertexts. These keys must be kept secret and distributed to only trusted entities as leaking of keys would compromise security of the entire system. Thus the management of such keys becomes very important. The vBASE framework does not handle the process of cryptographic key management and instead relies on the hardware architecture vendor to define this process. There are multiple recommendations and best practices to securely and efficiently manage keys in cryptography. These can be found in NIST recommendations on key management [6].

#### 2.5.2. Performance Analysis

The current computing frameworks have been predominantly designed around the principle of resource sharing and performance. Be it the virtual memory in traditional computers, or a virtualized desktops or a cloud computing system, the primary goal is to improve resource utilization and enhance the performance of the system. However, security and performance are two sides of a coin and security implementations may often lead to severe performance bottlenecks. Since, the sole purpose of the vBASE testing framework is to test hardware security architectures, analyzing its performance is of no use. However, performance analysis becomes imperative in vBASE execution frameworks (SecHYPE and CTrust) as their main focus is cloud computing platforms. In cloud systems, performance is very important as multiple VMs and application are competing for shared hardware re-

sources. The security implementations in cloud computing can introduce severe performance trade-offs in the system. Furthermore, the backbone of vBASE security implementation is the embedded hardware secure architecture. A vital facet of hardware security mechanisms is that they require modifications to the internal design of the processor, so as to add new hardware components. This additional hardware consumes logic, memory and clock resources, thereby impacting the performance of the system. Thus analyzing the performance of vBASE becomes utmost important.

The performance of the vBASE framework is analyzed by measuring the total time it takes to complete the secure communication channel. This channel is composed of a secure hypercall, Event Trigger Mechanism and a SIGNAL. The communication channel contains the following intermediary steps.

- Secure process (in DOM U) invokes the hypercall.

- Hypercall gets trapped in the VMM.

- Hypercall handler in VMM issues a VIRQ.

- The VIRQ gets trapped in the DOM 0 kernel.

- VIRQ handler in DOM 0 issues a SIGNAL to Monitor in DOM 0 userspace.

- Monitor receives and prints appropriate notification to user.

- Control goes back to DOM 0 kernel.

- Control goes back to VMM.

- Control gets back to DOM U secure process.

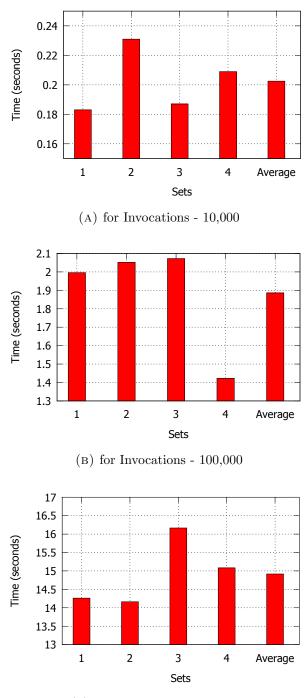

For each of the steps mentioned above, time has been measured from user-space, by using the time utility provided by the Linux kernel. In reality, multiple VMs run simultaneously in a cloud system. Each VM is in-turn capable of running multiple applications that may require secure execution. Hence the secure execution channel may be invoked several times at any given instant of time. This may introduce unwanted and unavoidable latency in the system. To simulate the effect of simultaneous secure channel invocations, the performance of the vBASE is measured for three values: 10,000, 100,000 and 1,000,000 invocations. These invocations are introduced at the same time and the corresponding time required to serve these requests is measured.

(C) for Invocations - 1,000,000

FIGURE 2.4. Time required for Secure Channel Invocations

The Figures 2.4a 2.4b 2.4c show the total time required for 10,000, 100,000 and

1,000,000 secure channel invocations respectively. For each type, four sets of reading are presented along with an average reading. The average reading for 10,000 invocations is approximately 0.2 seconds, while for 100,000 invocations is approximately 1.9 seconds and finally for 1,000,000 invocations is approximately 15 seconds. The measured time increases at lower rate from 10,000 invocations to 100,000 invocations but rises steeply from 100,000 invocations to 1,000,000 invocations. These readings are further used to estimate the average amount of time it takes to serve a single secure channel. The average time is 20  $\mu$ s (Average = 0.2/10,000) during 10,000 invocations, 19  $\mu$ s during 100,000 invocations and 15  $\mu$ s during 1,000,000 invocations. This indicates that the performance overhead imposed by the security mechanisms implemented in vBASE is significantly low and hence it does not degrade the overall performance of the cloud system.

#### 2.6. Previous Related Research

This Section provides a detailed description of the previous related research to the vBASE project. This literature survey is segregated in three categories - virtualizationbased security approaches, cloud-based security security approaches and software security approaches.

#### 2.6.1. Virtualization-Based Security Approaches

A lot of research has been focused towards the design and implementation of new and secure hypervisors. Some of these solutions are described in this section.

Overshadow [73] is a virtual machine based system that protects the privacy and integrity of application data even in an event of total OS compromise. This approach is designed and built on the concept of multi-shadowing — a mechanism that presents different views of physical memory, depending on the context performing the access. In a virtualized system, there are 2 levels of memory translations. A VMM/hypervisor maps the machine page number (MPN) to a guest physical page number (GPPN). This gives a VM an illusion that the entire memory is available for it to use. The OS in each VM translates each GPPN to a guest virtual page number (GVPN) to support multiple application execution. In this case, multi-shadowing is a mechanism that supports context dependent, one-to-many GPPN-to-MPN mappings. Memory cloaking combines multi-shadowing with encryption, thus presenting different views of memory plaintext and encrypted to different guest contexts. Overshadow provides and efficient and reliable solution for securing applications against a malicious guest OS. Its primary disadvantage is that all its security mechanisms are built around assuring application security against malicious guest OS. However, there is no consideration made for attacks originating from malicious application running in the same VM.

TrustVisor [40] is a specialty hypervisor that furnishes code/data integrity and secrecy for applications, permitting certain parts of an application to run fortified with security, by being in isolation, from OS and DMA capable devices. These security sensitive codeblocks are known and names as Pieces of application Logic (PALs). What serves to safeguard the memory, are 3 basic operating modes: Host, legacy, and secure. Host mode allows for TrustVisor code execution at the highest level of privileges. Host mode subsequently supports the two other modes of legacy guest and secure guest. In legacy guest mode, an OS and its applications can execute free from the adjacency and collaboration of TrustVisor's presence. This is not so far for secure guest mode, for which a PAL executes separately from legacy OS and its applications, eliminating any party's presence. TrustVisor relies upon available hardware virtualization support to offer memory isolation and DMA protection for each PAL. The authors have devised a mechanism called the TrustVisor Root of Trust for Measurement (TRTM) for applicable conductings of PALs. The TRTM is actualized by including a TrustVisor-managed, software micro TPM ( $\mu$ TPM) instance to be associated with each PAL. The TRTM and its microchip safekeeps sensitive code at a very fine granularity and also has a very small code base (approximately 6K lines of code) that makes its verification realistically possible and duplicable. TrustVisor can also establish the existence of execution running in isolation to an external entity. This specialized hypervisor imposes less than 7% overhead on the legacy OS and its applications, in most typical conditions.

sHype [54] is a secure hypervisor architecture, independent of an OS, to control in-

formation flow between the OS and the shared hardware platform. This approach is an extension of full-isolation hypervisor with security mechanisms that enable controlled resource sharing among VMs. it deploys a reference monitor interface inside the hypervisor to enforce information flow constraints between partitions. This reference monitor is implemented by using Enforcement hooks. These hooks retrieve access control decisions from the access control module (ACM). The ACM applies access rules based on security information stored in security labels attached to logical partitions. The ACM stores all the security policy information in the hypervisor and supports efficient policy management through a privileged H\_Security hypervisor call. sHype is build on top of vHype, which utilizes CPU protection rings to ensure that the partitions cannot execute privileged instructions. The protection mechanisms in sHype only talk about access control and privilege separation. It has been shown in the past that only employing these mechanisms are not adequate to protect against a more powerful and resourceful attack. The information about the logical partitions is reported to the ACM by the means of a secure H\_Security hypervisor call. Traditional hypercall mechanisms depend on guest OS functions and so the authors have assumed the guest OS to trustworthy. There have been a lot of research depicting the vulnerabilities in commodity OS due to their bulky codebase and hence these OS cannot be considered untrustworthy.

VMInsight [37] is a hardware-virtualization-based security monitor system, which can supply load-time and run-time monitoring for processes and can intercept system calls and process behaviors by observing changes in the VM CPU register. VMInsight is transparent to the softwares and OS running in the VM, because it is implemented in the hypervisor. VMInsight has 3 modules: information obtaining module, monitoring analysis module and information display module. The information obtaining, monitoring analysis, and information demonstration. The information obtaining module, being within the KVM module, possesses 3 functions: register reading, memory reading and PageFault. The monitoring analysis module is managed by the Linux system driver module method and able to load and unload per requirements. It obtains two callback interfaces of module: writeCr3Handle() and pageFaultHandle(). Finally the information demonstration module provides ioctl interface through the monitoring analysis module, obtains the process security monitoring information of virtual machine, saves to the security event database and finally demonstrates the information using the WEB method. It also collects user control information and sends its feedback to the monitoring analysis module, to handle the operation of processes. What the experimental results reveal is that the performance overhead of VMInsight comes at less than 10%, which makes it feasible to join into application for third-party security monitoring. The drawback to this approach is that the monitoring process functions at the granularity of a VM but yet not so for specific processes contained inside the VM. Consequently, the monitoring that would be needed could be an extortionately unwieldy amount. This bulkiness can markedly degrade the performance when more than one VM is in operation on just one sole hardware platform. The monitoring module is entirely constructed inside the kernel and relies on the kernel drivers to garner monitoring information. Inasmuch, the kernel becomes integral to the TCB, which can open back doors for determined attackers to exploit current security vulnerabilities in kernel code.

VASP [42] is a hypervisor based monitor that allows a trusted execution environment to monitor various malicious behaviors in the OS. This approach leverages the features provided by x86 hardware virtualization and self-transparency technology to provide an unified security protection to unmodified OS such as Linux and Windows. The VASP hypervisor Layer exports 3 sets of interfaces - memory management interface, trap register interface and debugging interface. Memory management interface is used to realize the memory management of VASP itself. Trap register interface supports the extension usage of VASP and provides configurable interceptions. And finally the debugging interface is used for dynamic analysis when developing the hypervisor. The monitoring mechanism in VASP is implemented in the form of kernel module that can execute any special instruction with highest privileges. Thus it relies on the kernel which may introduce some security vulnerabilities. To close this vulnerability, the authors have implemented memory self-transparency in VASP. In this, a clone of OS page table is made and provided to the hypervisor while executing. Also, some spare memory space is used as pseudo memory space of the hypervisor and the physical address of hypervisor is modified. As a result, the application or kernel in the guest operating system can only access the physical address of pseudo memory when using the virtual address of hypervisor, but hypervisor can access its real physical address using the same virtual address when it executes in the root mode. A significant disadvantage of VASP is that it provides a monitoring mechanism to protect against an entire OS. This in itself is a rigorous task as every single access that goes through the OS has to be monitored. And even though the performance analysis in the paper, does not reflect this, the performance will degrade exponentially when multiple VMs run on the same hypervisor. Moreover since the monitoring mechanism is implemented as kernel module, it has to be pre-included in the VM image.

Finally authors Dwoskin et. al [14] have proposed a testing framework, which provides APIs for monitoring hardware and software events in the system under test. The testing framework is divided into two systems - the System Under Test (SUT) and the testing System (TS). The SUT is meant to behave as closely as possible to a real system which has the new security architecture. It runs a full commodity guest OS, which is vulnerable to attack and is untrusted. The TS machine simulates the attacker, who is trying to violate the security properties of the SUT. It is kept as a separate virtual machine so that the TS Controller can be outside of the SUT to launch hardware attacks. Attack Scripts reside on the TS and specify how particular attacks are executed on the SUT. Based on the requirements, the attack model and attack scripts can be elegantly modified.

## 2.6.2. Cloud-Based Security Approaches

This section emphasizes on research ideas that present consolidate frameworks/architectures to provide security in cloud computing environments.

NoHype [31] proposes the approach of removing the virtualization layer while retaining only its key features. The multi-tenant design of virtualization technology, though has several advantages, is a serious security concern in Cloud Computing. A motivated attacker can attack the virtual machines or the virtualization software and if successful it will compromise the confidentiality and integrity of the user applications and data in the cloud. In NoHype framework, only one VM is run on each processor core. This removes the need for active VM scheduling done by the hypervisor and protects against software cache based side channel attacks. Each guest OS has a view of memory where it has a dedicated and guaranteed fraction of physical memory. The guest operating system is assigned it own physical device and given direct access to it. The Ethernet switches in the data center network should perform the switching and security functions, not a software switch in the virtualization layer. Some of the drawbacks of NoHype are that it allocates each VM to a core. Such hard allocation of server resources can cause performance overheads and can be ineffective. The hardware memory is partitioned and each guest OS has the view of the entire memory. Here the authors are assuming that the OS itself is not malicious. Whereas it has been proved over and over again that OS can have a lot of vulnerabilities. In such cases , attackers could carry out memory based attacks thus compromising the confidentiality and integrity of data of all other VMs. The biggest disadvantage is that the OS is root of trust in this architecture.

CloudVisor [76] - In this paper, the authors propose a transparent, backward-compatible approach that protects the privacy and integrity of customer's VMs on commodity virtualized infrastructures, even facing a total compromise of the VMM and the management VM. The key feature of this approach is the separation of the resource management from security protection in the virtualization layer. A tiny security monitor is introduced underneath the commodity VMM using nested virtualization that provides protection to the hosted VMs. CloudVisor is an extremely lightweight security monitor that runs at the host mode i.e. highest privilege level in the system. The VMM is deprivileged to a lower privilege level. CloudVisor enforces the isolation and protection of resources used by each guest VM and ensures the isolation among the VMM and its guest VMs. The traditional virtualization functions such as resource management, VM management and scheduling etc. are still done by the VMM. CloudVisor transparently monitors how the VMM and the VMs use hardware resources to enforce protection and isolation of resources used by each guest VM. CloudVisor relies on TPM and trusted execution design for ensuring the security of a cloud system. This is a significant drawback as the TPM cannot protect against many of attacks that threaten privacy of users. Also the TPM does not reduce the threat from spywares that could monitor and profile user's activities, such as browsing habits, and send them to a remote party. It is also vulnerable to power analysis which can break tamper-evident property of the TPM by being able to extract information from protected storage without being detected. In Cloud-Visor, the security of the VMs and itself is tested at start up by comparing its current image to a know secure image stored in the TPM. This still does not protect from vulnerabilities and attacks introduced during the running of VM and CloudVisor. Since the VMM is now deprivileged but is still placed at a higher privilege level than the guest VMs, this introduces another level of paging within CloudVisor. This adds to complexity of the system.

CloudSec [27] is a virtualization-aware monitoring appliance that supplies active, transparent and real-time security monitoring for hosted VMs in the IaaS model. It relies on virtual machine introspection (VMI) techniques to supervise the physical memory of guest VMs at the hypervisor level. CloudSec externally reconstructs a high-level semantic picture of the running OS kernel data structures instances for the monitored VM's OS. The predominant concept here is to map with accuracy the underlying hardware memory layout as against the OS kernel structure. The VMI layer in CloudSec holds two components: the back-end component that enables the hypervisor to acquire control over the hosted VMs in order to, if necessary, delay any access to the physical memory and CPU, and the front-end component, which is comprised of APIs that enable attainment of data about the monitored VM's running OS from the hypervisor and the regulation of accesses to the physical memory and CPU registers. A proof-of-concept prototype has been developed using VMsafe libraries on a VM ware ESX platform. The primary preoccupation centers on the performance of CloudSec. Reconstructing the OS high level semantic view externally of all the VMs running in the cloud daunts as an especially costly process, time-intensive and performance-burdened, notwithstanding that a large pubic cloud could be occupied by thousands of VMs and thus the scalability of CloudSec at that dominates as an issue. No clarification exists on how this framework will be able to assure that its own execution is a secure one. If ever should occur an attack that succeeds on the CloudSec itself, the whole VMI will be rendered untrustworthy.

In [39], Lui et. al present a framework where a measurement module (MM) is added in each guest VM. It measures every running executable in that VM. The MM transfers new measurement values to the trusted VM via standard inter-VM communication mechanisms. The trusted VM stores those values in sequence in a measurement table (MT). At the same time, the system extends these measurement values into a specified platform configuration register (PCR). To ensure the measurement process's trustworthiness, a memory watcher (MW) module has been added to the VMM. The assumption that the guest OS is trustworthy is the biggest drawback on this framework. A lot of research has shown that the commodity OS can extremely vulnerable to attacks due to their code size and thus highly untrustworthy. The security measurement is only performed statically during boot up time. This does not account for attacks introduced while the executable is running. The inter-VM communication channel used for storing the executable measurement relies on kernel functions, which may be compromised themselves. The verification process only involves hash verification. This only guarantees the integrity of the executable. There is no verification like encryption to ensure the confidentiality of the executable is also intact.

### 2.6.3. Software Security Approaches

Some researchers are motivated to propose new software security solutions that deal with application level and OS level changes to provide trustworthy and secure execution in cloud computing. For instance, Ashish Thakwani has proposed dfork [1] to provide processlevel isolation using virtualization. dfork is a clone of posix fork where a separate kernel and file-system is allocated to every new process to isolate its operations and interactions from other processes. This method gives an ability to review the changes done by the application before committing to the underlying hardware, thus giving control to accept, isolate or discard some of these changes. Rutkowska et al. propose a new (modified Linux) operating system called Qubes OS [29]. It is very similar to dfork in a way that every process that is being secured gets its own kernel and environment in a virtualized container. Qubes OS provides security by isolating application execution in its own virtual machine. Finally, Microsoft OS research has proposed an approach called Singularity [26] to solve the process isolation problem by introducing a new concept of software assisted process isolation as opposed to widely accepted, de-facto, standard of hardware assisted process isolation.

### 2.7. Conclusion

Advances in computing power and constant inter-connectivity have made modern day attackers extremely powerful. Softwares are increasingly vulnerable to attacks originating from multiple sources and growing into various forms. Therefore, Software Protection is critical n this era of computing. The need for hardware assisted software security stems from the ever expanding worth of softwares. In addition to this, the security mechanisms implemented in softwares are inadequate and untrustworthy. Trust can be removed from the softwares by properly leveraging the hardware security mechanisms. However, the wide scale adoption of hardware security mechanisms has been impeded due to the emphasis given to performance over security during the design phase.

In an effort to answer this question, we have proposed the virtualization based secure (vBASE) framework. In the vBASE testing framework, we have successfully demonstrated how hardware secure architectures can be realized and tested in an efficient manner using the data structures provided by the virtualization technology. The mechanisms implemented in vBASE removes OS from the Trusted Computing Base (TCB), which has proved to be a big challenge for years.