# GENERAL PURPOSE PROGRAMMING ON MODERN GRAPHICS HARDWARE Robert Fleming, B.Sc.

Thesis Prepared for the Degree of MASTER OF SCIENCE

UNIVERSITY OF NORTH TEXAS

May 2008

# APPROVED:

Robert Renka, Major Professor

Armin Mikler, Committee Member

Tom Jacob, Committee Member

Krishna Kavi, Chair of the Department of

Computer Science and Engineering

Oscar Garcia, Dean of the College of

Engineering

Sandra L. Terrell, Dean of the Robert B.

Toulouse School of Graduate Studies

Fleming, Robert. <u>General Purpose Programming on Modern Graphics</u>

<u>Hardware</u>. Master of Science (Computer Science), May 2008, 90 pp., 1 table, 3 figures, references, 124 titles.

I start with a brief introduction to the graphics processing unit (GPU) as well as general-purpose computation on modern graphics hardware (GPGPU). Next, I explore the motivations for GPGPU programming, and the capabilities of modern GPUs (including advantages and disadvantages). Also, I give the background required for further exploring GPU programming, including the terminology used and the resources available. Finally, I include a comprehensive survey of previous and current GPGPU work, and end with a look at the future of GPU programming.

Copyright 2008

by

Robert Fleming

To Wanda and Cheesepuff, my partners in crime.

# TABLE OF CONTENTS

|            |      | F                                         | Page |

|------------|------|-------------------------------------------|------|

| LIST OF TA | BLES | AND ILLUSTRATIONS                         | vi   |

| Chapters   |      |                                           |      |

| 1.         | МОТ  | TIVATION                                  | 1    |

|            | 1.1  | What Kinds of Computation Suit the GPU?   | 2    |

|            | 1.2  | GPU Limitations                           |      |

|            | 1.3  | What This Document Contains               | 4    |

| 2.         | BACI | KGROUND MATERIAL                          | 5    |

|            | 2.1  | A Brief History of GPU Programmability    | 5    |

|            | 2.2  | The Graphics Pipeline                     |      |

|            | 2.3  | The GPU Programming Model                 | 11   |

|            |      | 2.3.1 Stream Processing Terminology       | 13   |

|            | 2.4  | Languages                                 | 14   |

|            | 2.5  | Debuggers, Profilers, and Authoring Tools | 16   |

|            | 2.6  | Matrix Multiplication Example             |      |

|            |      | 2.6.1 GLSL Impementation                  | 19   |

|            |      | 2.6.2 CUDA Implementation                 | 25   |

| 3.         | SUR' | VEY                                       | 31   |

|            | 3.1  | GPGPU Rendering                           | 31   |

|            |      | 3.1.1 Global Illumination                 | 32   |

|            | 3.2  | Image Processing                          | 36   |

|            |      | 3.2.1 Volume Reconstruction               |      |

|            | 3.3  | Audio                                     | 39   |

|            | 3.4  | Computational Geometry                    | 40   |

|            | 3.5  | GPU Algorithms and Data Structures        | 42   |

|            |      | 3.5.1 Mathematics                         | 43   |

|            |      | 3.5.2 Data Structures                     | 50   |

|            |      | 3.5.3 Sorting                             | 51   |

|          | 3.6    | Simulation           |                                                            | 53 |  |  |

|----------|--------|----------------------|------------------------------------------------------------|----|--|--|

|          |        | 3.6.1                | Cloth                                                      | 53 |  |  |

|          |        | 3.6.2                | Crowd                                                      | 54 |  |  |

|          |        | 3.6.3                | Fluid                                                      | 55 |  |  |

|          |        | 3.6.4                | Physics                                                    | 58 |  |  |

|          |        | 3.6.5                | GPUs in High-performance Computing, Networks, and Clusters | 63 |  |  |

|          |        | 3.6.6                | Bioinformatics                                             | 65 |  |  |

|          | 3.7    | Previo               | ous Work                                                   | 66 |  |  |

| 4.       | CON    | CLUSIC               | DN                                                         | 67 |  |  |

| NOTES    |        |                      |                                                            | 69 |  |  |

| Appendic | es     |                      |                                                            |    |  |  |

| A.       | matrix | matrixMul_glsl.cpp70 |                                                            |    |  |  |

| B.       | matrix | matrixMul_cuda.cu75  |                                                            |    |  |  |

| REFERE   | NCES   |                      |                                                            | 79 |  |  |

# LIST OF TABLES AND ILLUSTRATIONS

|     | Page                                           |

|-----|------------------------------------------------|

|     | Tables                                         |

| 2.1 | How Shader Models Relate to DirectX Versions   |

|     |                                                |

|     | Figures                                        |

| 2.1 | The OpenGL Graphics Rendering Pipeline         |

| 2.2 | Computation C = A * B                          |

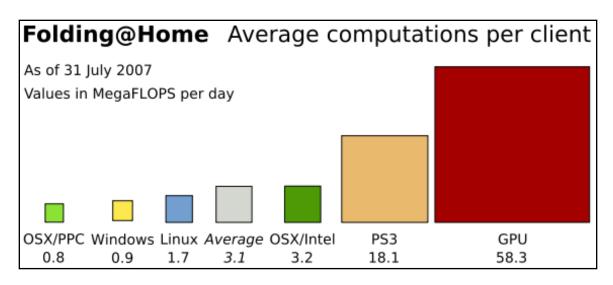

| 3.1 | Folding@Home Average Computations per Client65 |

#### **CHAPTER 1**

#### **MOTIVATION**

Early graphics processing units of the 1980s and 1990s were built as 2D accelerators. Common operations included bit blitting, which is a combination of two bit maps using a raster op (for example: AND, OR). Today, GPUs are a cheap commodity solution to having a data-parallel co-processor alongside the CPU. In their evolution as processors, they became fully programmable in three stages of the graphics pipeline (§ 2.2). In addition, they specialize in massively parallel scalar processing; modern GPUs have up to 128 independent processors (NVIDIA 2006), whereas CPUs have, at the desktop level, only reached 8 cores.

GPUs are also outpacing CPUs in terms of raw processing horsepower. At the time of this writing, Nvidia's G80 is capable of a theoretical peak performance of 340 Gflops, compared to the almost 40 Gflops of Intel's Core 2 Duo processor (NVIDIA 2008, NVIDIA CUDA). GPU pixel processing is increasing at a rate of 1.7 times per year, and vertex processing is increasing at a rate of 2.3 times per year, contrasted with a 1.4 multiplier for CPU performance (Owens et al. 2005).

Recently, there has been an increasing interest in *general purpose* computation on graphics hardware. The ability to work independently alongside the CPU as a coprocessor is interesting but not motivating enough to learn how to apply problems to the graphics domain. However, with full programmability and the computational power of GPUs outpacing CPUs (in terms of a price/performance ratio), the GPU has moved to a place of being the primary processing unit for certain applications, with the CPU managing data and direction of the GPU. This is motivation enough to learn how to

apply certain problems to the domain of computer graphics, thus we achieve general purpose computation on graphics hardware.

#### 1.1 What Kinds of Computation Suit the GPU?

GPUs were built primarily as graphics processing units, and so we know that they excel at computer graphics. To see what kinds of problems can be mapped well to GPUs, we simply abstract computer graphics computation. Two key ideas in graphics processing are data parallelism and independence. That is, GPUs efficiently operate on streams of data where different elements of the stream are processed simultaneously (parallelism). Also, each piece of data in the stream typically has little or no dependence upon other data elements in the stream. Any problem that benefits from parallelization and has mostly independent data would map well to GPU hardware.

We also know that GPUs operate almost exclusively on vectors of floating point numbers. Any arithmetically intense problems would do well to take advantage of the fact that the cost of GPU computation is decreasing more rapidly than the cost of communication (memory bandwidth, caches) (Harris 2005). A good example of this is finding the solution of a system of linear equations (Krüger and Westermann 2005). Solving systems of linear equations maps well to GPU hardware because the ratio of arithmetic operations to words transferred (where a word is the word-size of the architecture; i.e. typically 32 bits) is very high.

#### 1.2 GPU Limitations

Not all computation maps well to GPU programming, however. Until very recently, GPUs lacked integer operations such as bit-shifts and bitwise logical operations (AND, XOR). As a result they are not well-suited to fixed-point computation (though this is typically not a downside as floating-point computation is available) and other integer-heavy arithmetic. GPUs also lack efficient branching operations; only recently are they capable of branching in the fragment processor and previously the vertex processor. Typically, GPUs evaluate both sides of the branch and discard one (Owens et al 2005), whereas CPUs historically excel at branch prediction.

Caches are typically small on GPUs, and memory-intensive computation is not well-suited for mapping onto graphics hardware. While memory bandwidth may be high, GPU vertex processors can only cache approximately 24 vertices<sup>1</sup>, in constrast with the 1-2 megabyte caches of newer CPUs. This is not to say GPUs don't access large pieces of data in memory, but they typically don't read/write to memory in frequent iterations (in fact, typical GPU programs read several times and write only once at the end). The Nvidia Geforce 8800 GTX has 768 MB of on-card RAM and a peak memory bandwidth of 86.4 GBps (NVIDIA 2006), clearly demonstrating apt memory computation ability, but due to the structure of GPU programming, it is not suited for fast, successive read/writes.

GPUs are further limited in floating point precision, with only the most recent GPUs having full 32-bit IEEE 754 single-precision floats, whereas historically they have done computation in 16 or 24-bit precision. Double-precision 64-bit floats are rumored for an upcoming revision of Nvidia's Tesla line of GPUs, which will be built specifically to

address GPGPU (NVIDIA 2007). There is no indication of double-precision floats reaching commodity graphics hardware any time soon. The current lack of double-precision floats limits the adoption of GPU programming for many areas of scientific computing and numerical computation.

Lastly, GPU programming is limited in that the problem of interest must be mapped to the graphics programming model, with only a few abstractions available to programmers familiar with the CPU model. Achieving good performance in GPU programming requires in-depth knowledge of not only graphics programming, but also modern hardware trends. This further limits the adoption of general purpose GPU programming as new problem domains usually require an expert in the domain as well as an expert in graphics programming.

#### 1.3 What This Document Contains

This thesis introduces and covers all introductory aspects of general-purpose computation on modern graphics hardware and provide instructions on how to further obtain information on any specific or general sub-domain thereof. Chapter 1 provides the motivation and impetus for GPGPU, followed by Chapter 2, which covers the description and methodology for general-purpose computation on GPUs. Chapter 3 is a comprehensive look at all current and previous general-purpose work done on GPUs, with an emphasis on current work descriptions. Chapter 4 analyzes the future of the industry.

#### **CHAPTER 2**

#### BACKGROUND MATERIAL

As an introduction to general-purpose computation on graphics hardware, this section provides the necessary prerequisites. Section 2.1 is a quick history lesson, followed by Section 2.2, which details the traditional graphics pipeline. Section 2.3 introduces the GPU programming model. Section 2.4 is a current look at all the tools available for GPGPU programming. Finally, section 2.5 details an example GPGPU program.

# 2.1 A Brief History of GPU Programmability

The Nvidia Geforce 256 was the first card to offload vertex transform and lighting (T&L) from the CPU and onto the GPU<sup>2</sup>. This generation of card also introduced a programmable method of combining textures and colors by way of such OpenGL extensions as EXT\_texture\_env\_combine and NV\_register\_combiners. While this introduced greater flexibility than previous generations, it was not considered truly programmable, because the number of combinations remained limited.

The first true programmability arrived with the DirectX 8 generation of graphics cards. Cards in this generation include the Geforce 3, ATI Radeon 8500, and the Geforce 4. On the OpenGL side of things, the programmability was first exposed via vendor-specific extensions such as NV\_vertex\_program, but it was later available via the multi-vendor ARB\_vertex\_program. This extension allowed full control over the vertex transform stage of the graphics pipeline (§ 2.2). Around this time, the term *shader* became prevalent as a way of denoting a program that runs on the graphics card. A

pixel shader (or fragment program, in OpenGL) is a program that runs on each individual fragment processed, and a vertex shader (or vertex program) runs on each vertex processed.

From this generation on, the programmability of GPUs was denoted with what shader model they were capable of. The shader model is closely tied with what DirectX version the GPU is capable of rendering in full hardware mode (without CPU assistance), as shown in Table 2.1. Typically, with each generation of GPUs the two main independent hardware vendors (IHV), ATI and Nvidia, would release OpenGL extensions exposing the same functionality as DirectX.

With each shader model release, the programmability was typically increased by several factors. For example, the maximum number of instruction slots changed. In pixel shader 1.1 the maximum number of texture fetch instructions was 4, and the maximum number of arithmetic instructions was 8. In pixel shader 2.0 this was increased to 32 texture fetches and 64 arithmetic operations. Pixel shader 3.0 increased the instruction slots to a minimum of 512, and with loops and branching taken into account, the number of executed instructions can be as high as 2^16. Pixel shader 4.0 increased the available instruction slots to 2^16, with the executed instructions effectively unlimited. Each generation was a huge improvement over the previous generation. Also, new available registers and new instructions became available with every shader model release. For instance, vertex shader 3.0 introduced the ability to do texture fetches in the vertex shader, which enabled a whole range of new possibilities in GPGPU as memory fetches so early in the pipeline were previously impossible.

With the introduction of the Geforce 8 and shader model 4.0, the programmability of GPUs reached a whole new level with what is known as the unified shader model. Under shader model 4.0, all three shader types, pixel, vertex, geometry, (§ 2.2) enjoy the same instruction set. This is possible with the new scalar architecture of shader model 4.0 hardware, where there is no longer specialized processors for shading pixels and other processors for transforming vertices. Instead, there are general purpose processors that can be scheduled to run any type of shading program. In the past, when rendering a geometry-heavy scene, the pixel processors were mostly idle; likewise when rendering a heavily post-processed scene, the vertex processors were underutilized. Under the unified architecture, all resources can be used regardless of the type of scene. This is discussed extensively in (NVIDIA 2006). Shader model 4.0 also introduced geometry shaders, a previously nonprogrammable stage of the graphics pipeline, as well as true integer computation support on GPUs (including bitwise operations).

| DirectX<br>Version | Vertex<br>Shader<br>Version | Pixel Shader<br>Version | Geometry<br>Shader<br>Version |

|--------------------|-----------------------------|-------------------------|-------------------------------|

| 8.0                | 1.0 <sup>3</sup> , 1.1      | 1.0, 1.1                | n/a                           |

| 8.1                | 1.2, 1.3, 1.4               | 1.0, 1.1                | n/a                           |

| 9.0                | 2.0                         | 2.0                     | n/a                           |

| 9.0a               | 2a, 2b                      | 2.x                     | n/a                           |

| 9.0c               | 3.0                         | 3.0                     | n/a                           |

| 10.0               | 4.0                         | 4.0                     | 4.0                           |

| 10.1               | 4.1                         | 4.1                     | 4.1                           |

Table 2.1: How Shader Models Relate to DirectX Versions

#### 2.2 The Graphics Pipeline

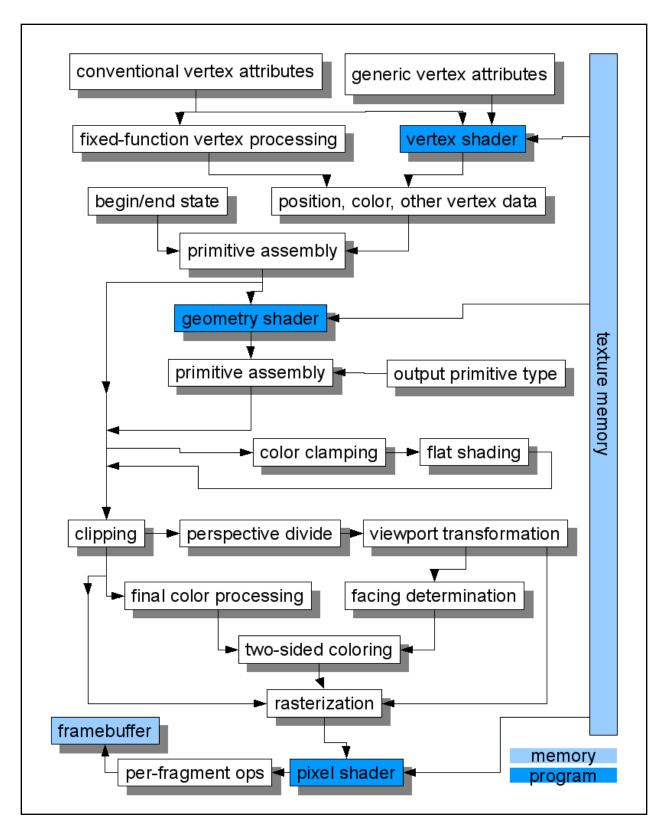

There are many resources available that explain the graphics rendering pipeline in more detail, such as (Akenine-Möller and Haines 2002) and (Shreiner et all 2007), but a brief explanation is included here for completeness. The following describes the graphics pipeline as implemented in the OpenGLAPI. Illustration 2.1 should be used as a guide when reading this section.

First, vertices are specified by the application, either with conventional attributes such as position, color, and texture coordinates or by generic numbered attributes. Next, they are transformed by either the fixed-function pipeline or by a vertex shader. Modern graphics drivers usually implement the fixed-function pipeline via a generated vertex shader. The fixed-function vertex transformation includes multiplying the vertex position by the modelview, and projection matrices, as well as texture coordinate generation and lighting calculations. A custom vertex shader has the option to do all or none of these calculations.

The next step is primitive assembly, where vertices are assembled into primitives specified by the application, such as triangles, points, or quads. If a geometry shader is specified, it is executed once on each input primitive. The geometry shader is specified with an output primitive type, which may or may not be different than the input primitives. The geometry shader can emit new vertices, which are then assembled into the output primitive type.

Optionally, the vertex colors are clamped to the range [0, 1], and flat shading can be applied. Flat shading applies just one color to the entire primitive, as opposed to smooth shading which interpolates the colors between each vertex.

Vertices are then clipped to the view volume in clip coordinates, and then perspective division converts them to normalized device coordinates. The viewport transformation step then converts vertices to window coordinates. Final color processing refers to converting color values to fixed-point values. See the OpenGL specification § 2.14.9 for further details (Segal and Akeley 2006). The primitive is determined to be either front or back facing, which determines whether the front or back color of a vertex is chosen.

Rasterization converts the primitive into a two-dimensional image, the output of which is a fragment and an associated depth value. The fragment can be thought of as a 'potential pixel,' as technically a pixel value is what gets written to the framebuffer, and a fragment may be killed before it reaches the framebuffer. A pixel shader, or fragment shader, is executed for each fragment generated. The shader may change any value associated with that fragment, such as color or depth, except the final position in the framebuffer is already determined at this point in the pipeline (final fragment position may be manipulated earlier in the pipeline indirectly such as via a vertex shader). Some final fragment operations such as the depth test, alpha test, stencil test, and blending are done before the fragment is finally written to the framebuffer. Also, it is worth noting that the "framebuffer" may or may not be the actual backbuffer (or frontbuffer, i.e. the visible window) of the application, and indeed, many GPGPU programs are run without rendering an image to the backbuffer. With modern hardware, it is possible to render directly to texture memory, the results of which may be used in subsequent rendering passes. This concept is critical to GPGPU programming.

Illustration 2.1: The OpenGL Graphics Rendering Pipeline

# 2.3 The Programming Model

The GPU programming model is a subset of a broader field called *stream* processing. In stream processing, a set of input data (called a stream) is applied to a series of operations (called a kernel), once for each element in the stream. The central idea is that each element in the stream is independent from every other element, allowing each element to be processed in parallel. When only one kernel at a time is applied to the entire stream, it is called uniform streaming, which is a form of singleinstruction-multiple-data (SIMD), as opposed to multiple-instruction-multiple-data (MIMD), or single-instruction-single-data (SISD), the latter of which is the execution model of a typical single-core CPU. Modern CPUs have vector processors that utilize the streaming SIMD extensions (SSE) instruction set, and are capable of, for example, multiplying four floating point numbers against another four floating point numbers in a single instruction. While this is SIMD, stream processing is the same concept at a much larger level, with typical streams being millions of elements large, and kernels consisting not just of a single multiply, but possibly hundreds of operations. For this reason, GPU programming is sometimes called single-program-multiple-data, or SPMD.

Stream processing is a data-parallel methodology, as opposed to a task-parallel methodology. An example of task parallelism is the CPU threading model: each task is broken up into a thread of execution which may have completely different instructions than any other thread, as well as possibly different data. In stream processing, the instructions for each element of the stream are fixed (branching and looping aside); only the data is different. Unlike task parallelism, which has the overhead of synchronization issues to deal with (race conditions, locks, etc.), it is easy to demonstrate that the

effectiveness of a data-parallel device like the GPU can be increased simply by adding more stream processing elements.

There are two important tenets in stream processing. First, compute intensity is the number of arithmetic operations per memory access. Second, data parallelism means that each stream element can be processed independent of any other. A high level of data parallelism and compute intensity both indicate a good match for GPU programming, because, as mentioned earlier, the cost of computation is decreasing more rapidly than the cost of communication.

On GPUs, input streams typically mean a set of vertices sent by the application. Output streams are usually 2D textures, or the framebuffer itself, which can be thought of as a 2D texture. Kernels can mean either the vertex shader, geometry shader, or pixel shader, depending on the desired number of output stream elements. The typical GPGPU setup involves drawing a fullscreen quad such that the number of pixels in the quad equals the number of desired times to execute the kernel body, which in this case is implemented via a pixel shader. Optionally rendering the result into a texture to save the results for future computations, it is possible to manipulate the viewport to ensure a one-to-one mapping of output pixels to texels. Alternatively, the quad could be rendered to the framebuffer and then copied to a texture, for architectures that do not support render-to-texture (RTT). Regardless of the destination, texture or framebuffer, it is essential to realize that, due to the structure of the graphics pipeline, the output memory is write-only, and all other texture memory is read-only. This has led to a technique called *ping-ponging*, where the result of one computation is used as the input for the

next computational pass, with the source and destination textures swapping at each iteration.

# 2.3.1 Stream Processing Technology

There are a few common techniques in stream processing, the simplest of which is called a *map* operation. A map simply applies the kernel function to each element in the stream. As before, using a pixel shader as the kernel, a pixel is generated for each element in the stream, producing the output stream.

A reduce operation produces a smaller output stream from a larger set. Typically, the larger set is input for the reduction kernel, where multiple elements are read, but only one element is written. This is usually implemented via a pixel shader that reads from multiple textures before writing a single value. A reduce operation can be repeated to condense a stream down to a desired size, potentially down to a single stream element.

The two methods of stream communication are *scatter* and *gather*. While the cost of communication is high compared to the cost of computation, not all algorithms are possible with pure computation, and sometimes communication is necessary.

Gather is basically a random-access read, which in our case is typically sampling a texture. Gather was previously only possible in the fragment processor, but in the most recent GPU architectures it is available in all programmable stages of the graphics pipeline (§ 2.2). Scatter is a random-access write into memory. The fragment processor is incapable of scatter, as the location in memory of the output pixel is fixed at the time

of the shader's execution. To implement scatter on the GPU, a vertex or geometry shader is written to manipulate the vertex's position, or generate new vertices on-the-fly.

### 2.4 Languages

The most important advancement towards GPGPU thus far has been the advent of high-level shading languages. Previously, shaders had to be written in assembly that, while standardized, still changed with each shading model iteration. High-level languages enabled more complex algorithms to be expressed in easier-to-understand syntax, just as in traditional CPU programming languages. The three primary high-level shading languages are the OpenGL Shading Language (GLSL), Nvidia's C for Graphics (Cg), and Microsoft's High Level Shading Language (HLSL). GLSL is OpenGL specific, and HLSL is Direct3D specific, but Nvidia's Cg can be used with either API. All three have slight syntactic differences, but with an understanding of one language, it is relatively easy to transition to another shading language, assuming an existing understanding of the API it is used in (either D3D or OGL). Indeed, Cg and HLSL were developed by close collaboration between Nvidia and Microsoft, and the languages remain nearly identical.

Emerging from the high-level shading languages, several efforts have been made to program GPUs without the need to learn a graphics API, but instead using traditional C or C++. While still in its infancy, these efforts, usually in the form of a library rather than a new language (to take advantage of existing tools and technologies), have come a long way towards making GPGPU programming more available and approachable. First, the IHV specific solutions are Nvidia's Compute Unified Device

Architecture (CUDA) (NVIDIA 2008, NVIDIA CUDA), and ATI/AMD's Close-to-Metal (CTM) (Advanced Micro Devices 2006). ATI is also releasing an evolution of CTM called Compute Abstraction Layer (CAL), which promises to be higher-level than CTM, which is a very low-level interface to the GPU. On the open-source side of things, there is BrookGPU (Standford University Graphics Lab 2008), or simply Brook, which is a combination of the Brook stream programming language, and the Brook runtime library. Programs written in the Brook language (which is very similar to ANSIC) can be compiled down to run on a number of backends, including Direct3D, OpenGL, and CTM. The Brook compiler takes Brook language files (\*.br) and compiles them into C++, which (after compiled) then calls into the Brook runtime. Another open-source project is LibSh (McCool and DuToit 2004), simply Sh, which embeds itself inside C++. Instead of compiling a stream programming language into C++, the GPU programs in Sh are simply C++ programs. These programs make calls into the Sh runtime, which then dynamically takes the Sh operations and compiles them down first into an intermediate language, then finally into GPU code that the Sh runtime handles transparently in the backend. Both Brook and Sh are exposed as C or C++ libraries that provide an abstraction to the GPU-specific languages. Brook has, until most recently, been an inactive project for several years, and LibSh was abandoned as of August 2006. Most development in GPGPU/stream programming languages (as opposed to GPU languages, such as Cg/GLSL) has been in vendor-specific solutions, such as CUDA and CTM, that are nevertheless available for free to encourage development. Commercial stream programming languages remain few, with PeakStream (a spinoff of Brook) acquired by Google in June 2007, and Rapidmind (RapidMind 2008, RapidMind

Homepage), a commercialization of LibSh. Rapidmind takes the idea of Sh even further, with the backend runtime capable of executing on not only GPUs but multi-core CPUs as well as STI's (an alliance of Sony, Toshiba, and IBM) Cell architecture. Lastly, it is worth noting other stream programming languages such as MIT's StreamIt and projects such as Intel's Ct that are built mainly for multi-core CPUs and do not seem to take advantage of the extreme parallelism available in GPUs.

# 2.5 Debuggers, Profilers, and Authoring Tools

While stream programming languages are still developing, high-level shading languages have been available and production-ready for years. What limits their adoption, however, is not only the need to utilize a graphics API alongside the shading language, to take advantage of the GPU, but also the availability of tools such as debuggers and profilers.

Microsoft provides PIX, which allows profiling, optimizing, and debugging Direct3D code. Unfortunately, when debugging vertex and pixel shaders, the code is executed on the Direct3D reference rasterizer, which executes on the CPU. This is not only slower but not the exact environment the shader code will eventually run under, and relies instead on the quality of the reference rasterizer.

On the OpenGL side of things, there are many projects designed to trace and log OpenGL calls, and generally intercept rendering commands and capture OpenGL state. Examples include BunGLe, Graphic Remedy's gDEBugger, GLIntercept, spyGLass, and Nvidia's GLExpert. While some of these, such as gDEBugger, allow setting b reakpoints and debugging, none of them allow debugging shaders, which is of primary interest to

GPGPU programming. Two projects, Shadesmith and glslDevil (Strengert, Klein, and Ertl 2007), allow debugging of shaders, and both execute on the target hardware instead of software emulation. Shadesmith, however, only debugs fragment programs. GlslDevil retrieves information directly from the hardware pipeline, and does so transparently to the application (in other words, it does not require recompilation or relinking of the executable being debugged). In addition, it supports geometry shaders as well as vertex and fragment shaders.

Profiling information is readily available from IHV's, with Nvidia's

PerfHUD/NVPerfGraph, and ATI's GPU PerfStudio. NV's PerfHUD only supports

Direct3D, while ATI's PerfStudio supports both OpenGL and Direct3D. There is also

Nvidia's ShaderPerf and ATI's GPU ShaderAnalyzer for profiling shaders specifically,

with the former also only supporting D3D and the latter supporting both API's. OpenGL

profiling information can be acquired through some of the previously mentioned

OpenGL debuggers, such as gDEBugger.

Tools written specifically to help author shaders include Apple's OpenGL Shader Builder, TyphoonLab's OpenGL Shader Designer, Nvidia's FX Composer, and ATI's Rendermonkey. These tools provide a closed environment where shaders can be applied to various geometries without the need to worry about the external API calls (such as OpenGL or Direct3D), allowing quick turn-around between editing a shader and seeing it's effects on the output. However, in the context of GPGPU programming, these tools are not ideal, as many GPGPU programs aren't necessarily interested in rendering output, and many require complicated setup aside from just rendering geometry with textures.

While the number of debuggers and profilers may seem numerous, many have shortcomings that show the immaturity of GPU and GPGPU programming tools. For instance, many profilers aren't available for both graphics API's, and many debuggers are not capable of debugging shaders, or are not capable of debugging on the actual hardware. In addition, the relative infancy of GPGPU and stream programming languages means that existing debuggers and profilers can not yet be taken advantage of. It is expected this will change rapidly with time, with the eventual sophistication of GPU programming tools reaching that of CPU programming tools.

# 2.6 Matrix Multiplication Example

As an example of GPGPU programming, we explain how to do matrix multiplication on the GPU using two sample implementations: one using the OpenGL shading language, GLSL, and another using Nvidia's CUDA. We define the product of two matrices **A** and **B**, where **A** is an m by n matrix, and **B** is a n by p matrix, to be **C** =  $\mathbf{A} * \mathbf{B}$ , where **C** is an m by p matrix. The entry  $\mathbf{c}_{i,j}$  denotes the value of **C** at position (i, j), where

$$C_{i,j} = \sum_{k=1}^{n} a_{i,k} b_{k,j} = a_{i,1} b_{1,j} + a_{i,2} b_{2,j} + \dots + a_{i,n} b_{n,j}$$

for each pair i, j where  $0 \le i \le m$  and  $0 \le j \le p$ . To simplify things, we assume square matrices of size [dim, dim], and therefore m = n = p = dim. Consider the following C++ code for computing  $\mathbf{C}$  on the CPU:

```

void matrixMul_cpu(float* C, float* A, float* B, const int dim) {

for (int i = 0; i < dim; ++i) {

for (int j = 0; j < dim; ++j) {

float sum = 0;

for (int k = 0; k < dim; ++k) {

sum += A[i * dim + k] * B[k * dim + j];

}

C[i * dim + j] = sum;

}

}

}</pre>

```

Here we store **A**, **B**, and **C** in one-dimensional arrays where the element  $c_{y,x}$  is accessed via C[y \* dim + x]. Now we demonstrate how to perform this same computation using the GPU.

# 2.6.1 GLSL Implementation

The prerequisite before any OpenGL commands can be passed to the GPU is, first, a valid OpenGL context must be acquired. This is window-system specific, but many libraries exist to program this in a cross-platform way; for our purposes we used the GLFW library (GLFW Project 2008). The full source code for our GLSL sample, including initialization code and any functions not explicitly defined here, can be found in Appendix A. Our GLSL implementation will compute  $\bf C$  on the GPU by storing  $\bf A$ ,  $\bf B$ , and  $\bf C$  as textures, and then render to  $\bf C$  with a GLSL fragment shader that computes each element  $\bf c_{i,j}$ . We first define our matrix dimensions and then allocate space on the GPU for  $\bf A$ ,  $\bf B$ , and  $\bf C$  as textures:

```

const int dim = 7;

GLuint A_gpu_data = createTexture(dim);

GLuint B_gpu_data = createTexture(dim);

GLuint C_gpu_data = createTexture(dim);

```

The function **createTexture()** returns a single-channel<sup>4</sup>, floating-point texture of size [dim, dim] that is suitable for storing our matrices. We use the variable **C\_gpu\_data** to refer to **C** in texture memory, and the variable **C\_cpu\_data** to refer to **C** in main memory. Next, we allocate space on the CPU for our matrices and randomly assign values to **A** and **B**:

```

float* A_cpu_data = (float*) malloc(dim * dim * sizeof(float));

float* B_cpu_data = (float*) malloc(dim * dim * sizeof(float));

float* C_cpu_data = (float*) malloc(dim * dim * sizeof(float));

random_fill(A_cpu_data, dim * dim);

random_fill(B_cpu_data, dim * dim);

```

We next transfer the data of **A** and **B** from main memory to texture memory:

```

glBindTexture(GL_TEXTURE_RECTANGLE_ARB, A_gpu_data);

glTexSubImage2D(GL_TEXTURE_RECTANGLE_ARB, 0, 0, 0, 0, dim, dim, GL_LUMINANCE,

GL_FLOAT, A_cpu_data);

glBindTexture(GL_TEXTURE_RECTANGLE_ARB, B_gpu_data);

glTexSubImage2D(GL_TEXTURE_RECTANGLE_ARB, 0, 0, 0, dim, dim, GL_LUMINANCE,

GL_FLOAT, B_cpu_data);

```

The zeros in the function <code>glTexSubImage2D()</code> refer to mipmap levels and x-, y-offsets within the array, which we would set if we did not want to transfer the entire array. For more details about this and any other OpenGL function refer to the OpenGL man pages (Khronos Group 2007). Note that <code>A\_cpu\_data</code> and <code>B\_cpu\_data</code> are no longer needed, and can be released using <code>free()</code> should we choose to. In order to render to the texture <code>C\_gpu\_data</code> we need to create a framebuffer object, which can be thought of as an offscreen window, and attach our texture as its main color buffer:

```

GLuint fbo = 0;

glGenFramebuffersEXT(1, &fbo);

glBindFramebufferEXT(GL_FRAMEBUFFER_EXT, fbo);

glFramebufferTexture2DEXT(GL_FRAMEBUFFER_EXT, GL_COLOR_ATTACHMENT0_EXT,

GL_TEXTURE_RECTANGLE_ARB, C_gpu_data, 0);

```

In the OpenGL shading language, shaders are created and attached to *program objects*, which can be thought of as containers for shader programs (for example, holding one of each of a vertex shader, and a fragment shader). In our case, we need only a single fragment shader, and opt to use the fixed-function vertex processing. Shaders are passed to OpenGL as text strings, which can be read from disk, or included in the source directly. We store our fragment shader source in the string **fShaderSource**, which we will discuss later.

```

const char* fShaderSource = //discussed later

GLuint fShader = glCreateShader(GL_FRAGMENT_SHADER);

glShaderSource(fShader, 1, &fShaderSource, NULL);

glCompileShader(fShader);

GLuint program = glCreateProgram();

glAttachShader(program, fShader);

glLinkProgram(program);

```

A key idea in GPGPU computing when rendering to textures is to spawn the fragment shader once for each destination element; in our case, once for each texel of **C**. Thus, since a fragment shader is executed once for each input pixel, we must generate one pixel per texel of **C**. The following code creates this 1:1 mapping:

```

glMatrixMode(GL_PROJECTION);

glLoad Identity();

gluOrtho2D(0.0, dim, 0.0, dim);

glMatrixMode(GL_MODELVIEW);

glLoad Identity();

glViewport(0, 0, dim, dim);

```

Next, we must tell OpenGL where we are rendering to (the framebuffer object we attached **C** to), what textures we would like access to while rendering, and what program object (that contains our fragment shader) we would like to be active. We also pass some information to our fragment shader; namely, *dim* and the locations of **A** and **B**, by specifying them as uniform parameters. In GLSL, uniform parameters are variables which do not change per primitive; in our case, they never change.

```

glBindFramebufferEXT(GL_FRAMEBUFFER_EXT, fbo);

glDrawBuffer(GL_COLOR_ATTACHMENTO_EXT);

glClear(GL_COLOR_BUFFER_BIT);

glActiveTexture(GL_TEXTURE0);

glBindTexture(GL_TEXTURE_RECTANGLE_ARB, A_gpu_data);

glActiveTexture(GL_TEXTURE1);

glBindTexture(GL_TEXTURE_RECTANGLE_ARB, B_gpu_data);

glUseProgram(program);

glUseProgram(program);

glUniform1i(glGetUniformLocation(program, "A"), 0);

glUniform1i(glGetUniformLocation(program, "B"), 1);

glUniform1i(glGetUniformLocation(program, "dim"), dim);

```

Finally, to invoke our fragment shader once for every texel in **C** we draw a screen-sized quad:

```

glBegin(GL_QUADS);

glTexCoord2f(0, 0); glVertex2f(0, 0);

glTexCoord2f(dim, 0); glVertex2f(dim, 0);

glTexCoord2f(dim, dim); glVertex2f(dim, dim);

glTexCoord2f(0, dim); glVertex2f(0, dim);

glEnd();

```

Our quad is of size [dim, dim] and is screen-sized due to the viewport specified above (which defines the size of our OpenGL screen). Note the texture coordinates of the quad are unnormalized and are of the range [0, dim]. Normalized texture coordinates are of the range [0, 1]. Now we examine our fragment shader, which we stored in **fShaderSource**, which performs the matrix multiplication:

```

#extension GL_ARB_texture_rectangle : enable

uniform sampler2DRect A;

uniform sampler2DRect B;

uniform int dim;

void main() {

float sum = 0.0;

for (int i = 0; i < dim; ++i) {

float a = texture2DRect(A, vec2(i, gl_TexCoord[0].t)).r;

float b = texture2DRect(B, vec2(gl_TexCoord[0].s, i)).r;

sum += a * b;

}

gl_FragColor.r = sum;

}</pre>

```

We used the OpenGL extension ARB texture rectangle to allow our matrices to be any dimension in size; usually, OpenGL texture sizes are required<sup>5</sup> to be a power of two. Another benefit of using texture rectangles is it allows us to sample textures using unnormalized texture coordinates. A and B are of type uniform sampler2DRect, which means they are two-dimensional texture rectangles whose values do not change. They are sampled (i.e. read from texture memory) via the function texture2DRect(), which takes as parameters the texture name, and, for two-dimensional textures, a floatingpoint pair (s, t). The function returns four floating-point numbers in the form of a **vec4** (a GLSL data type), from which we are only interested in the first element (accessed<sup>6</sup> with the .r). The texture2DRect() function always returns four floats; it is up to the user to access the valid members that are returned. In our case, since A and B are singlechannel textures, only the first element is valid; the rest are undefined. The texture coordinates that we generated for our guad are accessed natively in the shader via the variable **gl\_TexCoord[0]**. These coordinates are automatically interpolated across the face of the quad, with **gl\_TexCoord[0].s** varying in the x direction of the texture, and **gl\_TexCoord[0].t** varying in the y direction. Our fragment shader calculates a single

value of **C**; namely, **c**<sub>i,j</sub> where (i, j) is (s, t). Our loop runs from 0 to dim and sums the products of the elements of **A** and **B**, with **A** being sampled along the current row, and **B** being sampled along the current column. Note that the shader is executed once per pixel, with the current pixel in column s and row t. Therefore, the variable **gl\_TexCoord[0].st** is a constant unique to each pixel during the shader's execution. Our resultant texture, **C**, is also a single-channel texture; therefore we store the result in the first channel of the output color (indicated by **gl\_FragColor.r**).

We usually wish to access the results of our computations back on the CPU in main memory. In order to transfer **C** back to the CPU we do the following:

```

glReadBuffer(GL_COLOR_ATTACHMENT0_EXT);

glReadPixels(0, 0, dim, dim, GL_LUMINANCE, GL_FLOAT, C_cpu_data);

```

The result of the matrix multiplication can be indexed at (y, x) via the array  $\mathbf{C}_{\mathbf{cpu}}$  data[y \* dim + x].

Our implementation has a few limitations; namely, it is limited in that dim \* dim must be a valid texture size. On current hardware, this limits us to matrices of size 8192 by 8192. Also, our implementation rendered to a single-channel floating-point texture (specifically, a GL\_LUMINANCE texture, see Appendix A for details), which must be a valid render target under both the video card and the driver in order to work. This is not widely supported (our test system used an Nvidia 8800 GT under Linux). Fortunately, rendering to a four-channel floating-point texture is more widely supported, and our matrix multiplication example can be optimized by packing two by two submatrices of **A** and **B** into the four color channels red, green, blue, alpha (RGBA) of their respective textures. This approach and more optimizations can be found in the work of Hall et al.

(Hall, Carr, and Hart 2003). Our implementation is intended for didactic purposes only. The full listing can be found in Appendix A.

# 2.6.2 CUDA Implementation

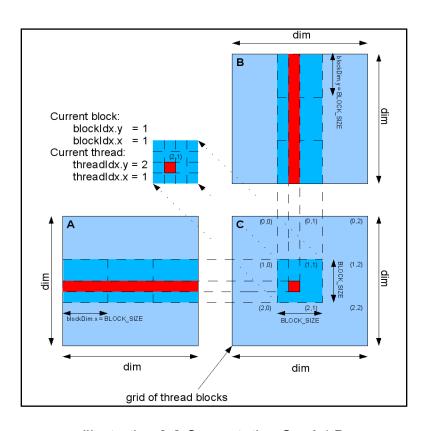

Our CUDA implementation performs the same computation as our GLSL implementation: C = A \* B, for matrices of size [dim, dim]. CUDA introduces some new terminology: the host is referring to the CPU, and host memory refers to main memory, or RAM. The device refers to the GPU, and device memory refers to texture memory, or sometimes called global memory when using CUDA<sup>7</sup>. Instead of a fragment shader performing the multiplication, our kernel is written in a dialect of C++. Each kernel invocation is executed over a grid, which can be thought of as our computational domain and range. This maps well to our example, which has both a domain and range of size dim. The grid is broken up into blocks, sometimes called thread blocks, because each block is further broken up into threads. Each thread can be thought of as a pixel, on each of which our fragment shader executed on. In this case, each thread calculates an element  $c_{i,i}$  of C. We refer to the size of each block as **BLOCK\_SIZE**, which is optimally chosen to be a multiple of the number of symmetric multiprocessors (SM) on the GPU<sup>8</sup>. By breaking up our computational domain into a multiple of the number of multiprocessors, we ensure that each SM is utilized; splitting it up less, for instance, would not utilize the full capability of the GPU.

We start by defining our matrix dimensions, the size in memory of a matrix, and allocating space on the GPU for each matrix:

```

const int BLOCK_SIZE = 14;

const int dim = BLOCK_SIZE;

const int mem_size = dim * dim * sizeof(float);

float *A_gpu_data, *B_gpu_data, *C_gpu_data;

cudaMalloc((void**) &A_gpu_data, mem_size);

cudaMalloc((void**) &B_gpu_data, mem_size);

cudaMalloc((void**) &C_gpu_data, mem_size);

```

Note that **C\_gpu\_data** is not a texture in this example, but simply a one-dimensional array of floats, exactly like its CPU counterpart. Next, we allocate space on the CPU for our matrices and randomly assign values to **A** and **B**:

```

float* A_cpu_data = (float*) malloc(mem_size);

float* B_cpu_data = (float*) malloc(mem_size);

float* C_cpu_data = (float*) malloc(mem_size);

random_fill(A_cpu_data, dim * dim);

random_fill(B_cpu_data, dim * dim);

```

We upload **A** and **B** to the GPU:

```

cudaMemcpy(A_gpu_data, A_cpu_data, mem_size, cudaMemcpyHostToDevice);

cudaMemcpy(B_gpu_data, B_cpu_data, mem_size, cudaMemcpyHostToDevice);

```

Before we execute our kernel, we need to specify the number of threads per block, and the number of blocks to split our grid into. This is done using a CUDA-specific datatype called **dim3**. One approach might be to just execute one block with *dim* by *dim* threads:

```

dim3 threadsPerBlock( dim, dim );

dim3 blocksPerGrid( 1, 1 );

```

Note that the third component of a **dim3** is not used in our case. This does not take advantage of all the multiprocessors we have available, however, as each block is executed on one SM. Luckily, CUDA limits the number of threads per block to 512,

which would limit us to matrices of size 512 by 512, which we would rather avoid.

Alternatively, we could execute *dim* by *dim* blocks each with one thread:

```

dim3 threadsPerBlock( 1, 1 );

dim3 blocksPerGrid( dim, dim );

```

This relieves the 512 by 512 limitation, and allows us to implement matrix multiplication on the GPU using the exact same syntax as the CPU implementation:

```

__global__ void matrixMul_gpu(float* C, float* A, float* B, const int dim) {

for (int i = 0; i < dim; ++i) {

for (int j = 0; j < dim; ++j) {

float sum = 0;

for (int k = 0; k < dim; ++k) {

sum += A[i * dim + k] * B[k * dim + j];

}

C[i * dim + j] = sum;

}

}

}

```

The keyword \_\_global\_\_ refers to a function which is *called* from the host, but *executed* on the device. This function is called using the following syntax:

Unfortunately, by only using one thread per block, we are not utilizing all 8 stream processors available to each symmetric multiprocessor. In order to take full advantage of the hardware we need to break up the problem into appropriate chunks for each SM as well as each of the stream processors available per SM. We choose the number of threads to be a multiple of the number of SM, which we indicated earlier as

**BLOCK\_SIZE**, and we choose the number of blocks by dividing our computational domain by the size of each block:

```

dim3 threadsPerBlock( BLOCK_SIZE, BLOCK_SIZE );

dim3 blocksPerGrid( dim/BLOCK_SIZE, dim/BLOCK_SIZE );

```

We execute our kernel with the same syntax as above (we have only changed threadsPerBlock and blocksPerGrid) with the following function call:

Using the same syntax as the CPU implementation for our GPU implementation no longer works. Instead, we define it as follows:

The keyword \_\_global\_\_ indicates this function is executed on the device, which means the one-dimensional arrays C, A, and B are actually in GPU memory. The variable blockDim refers to the dimensions of the block, and is a special variable accessible inside CUDA kernels (much like the aforementioned gl\_TexCoord[0] accessed inside our fragment shader). In our case, blockDim.x and blockDim.y are both of size BLOCK\_SIZE. The variable blockIdx refers to the index of the current block being

executed; similarly, the variable **threadIdx** refers to the current thread being executed. Our loop sums the products of **a** and **b** by indexing **A** along the current row and **B** along the current column. Unlike our GLSL sample which indexed into **A** and **B** using texture coordinates we passed to the shader, we have full access to these two-dimensional matrices stored in one-dimensional arrays. We also have full write access to global memory; although we don't utilize it, it is possible to write to **A** and **B** just as we write to **C**. Note the only difference between **C** and the other two matrices is the assignment of random values before launching the kernel; no special setup was required to write to **C**. In our GLSL sample, both **A** and **B** were read-only. Illustration 2.2 shows the computation for a single thread block and a single thread.

Illustration 2.2 Computation C = A \* B

Our CUDA implementation also faces several limitations. Matrix dimensions are required to be a multiple of **BLOCK\_SIZE** in order for our algorithm to work.

Necessarily, it also requires the latest Nvidia hardware (G80+), as CUDA was just released within the last year. Our implementation does not take advantage of the 16kb shared memory available to each block (which is faster than accessing global memory); however, an example in the CUDA SDK does so, and it also extends to non-square matrices. This shared memory is only exposed via CUDA; it is not available to the graphics AP is. Just as with our GLSL implementation, this example is for illustration purposes only. For high-performance matrix multiplication, Nvidia provides CUBLAS: an implementation of the Basic Linear Algebra Subprograms (BLAS) on top of CUDA. More information on CUBLAS, the CUDA SDK, and the CUDA toolkit can be found on Nvidia's website (NVIDIA 2008, Nvidia Cuda Zone), and the CUDA programming guide (NVIDIA 2008, NVIDIA CUDA). The full listing for our CUDA example can be found in Appendix B.

#### CHAPTER 3

### SURVEY

In this section we provide a comprehensive overview of all current work in general-purpose computation on graphics hardware. In section 3.1 we take a look at the classic GPGPU problem: real-time rendering and visualization. In section 3.2 we look at image processing algorithms which naturally map to the GPU. In section 3.3 we find some unusual uses of the GPU with audio processing, and in section 3.4 we look at computational geometry. Section 3.5 is a combination of both low-level mathematical methods used in general-purpose GPU programming as well as high-level data structures, the combination of which provides a solid algorithmic background for many of the other applications in this survey. Section 3.6 explores many simulations currently being done on graphics cards, some but not all of which also have a visual component. In section 3.7 we finish the survey with directions to more information that this paper might not have covered, as well as previous surveys conducted.

## 3.1 GPGPU Rendering

It seems odd to generalize computation on graphics hardware and then turn around and use it for real-time rendering, but that's exactly what some of the earliest GPGPU applications did. As rendering became more sophisticated the necessity to model reality more exactly became computationally costly. Utilizing the GPU's stream processing power to do expensive lighting and shadowing calculations became an obvious evolutionary step. The closeness of the simulation and the rendering, in that they are both on the GPU, became an advantage as well. As GPGPU languages evolve

and they become capable of accessing the hardware in more efficient ways than the traditional graphics pipeline (at least when it comes to general computation), it is expected that graphics APIs will be relegated to rendering the result of more expensive computations done by more suitable, more general languages.

### 3.1.1 Global Illumination

Global illumination refers to a group of methods used to simulate realistic lighting effects. It usually refers to a combination of direct illumination and indirect illumination, where the former is the contribution of light coming directly from a light source, and the latter taking into account light which has been reflected from other objects in the scene. There are many algorithms that can be used to approximate global illumination; of notable interest are those approximations which can be computed in real-time on the GPU.

# 3.1.1.1 Radiosity

In traditional radiosity as described in computer graphics, the scene is broken up into patches, each with coefficients (called form factors) describing how well each patch can see each other patch. These coefficients are used in a series of linear equations which, when solved, describe the diffuse energy leaving each patch. Radiosity is view-independent and does not describe effects such as specular lighting and reflections, which depend on the viewer's position. Once the energy (or resultant color, if visualized) is calculated, the scene may be viewed from any position without the need to recalculate the radiosity. An introduction to radiosity can be found in (Goral et al. 1984).

Coombe et al. (Coombe, Harris, and Lastra 2004) were the first to implement the entire radiosity algorithm on the GPU. Utilizing a progressive radiosity solution, which computes the coefficients on the fly to avoid O(n²) storage space of the equations, Coombe et al. modify the traditional radiosity algorithm in a few subtle ways to make it suitable for the SIMD nature of GPU computing. The scene is not subdivided into patches, but instead textures are used to store the radiosity component for each piece of geometry. Normally, in a subdivided scene the patches would be tested for visibility and radiosity (effectively the diffuse energy of the surface) would be assigned to each visible polygon. Instead, the texels of each polygon are tested for visibility, thus mapping well to a fragment program on the GPU.

In addition, a company called Geomerics claims to have an implementation of a real-time radiosity simulation on the GPU that includes not just a model of diffuse energy off of surfaces but also bounced specular highlights (Geometrics 2007).

## 3.1.1.2 Ray-tracing

While radiosity is a view-independent algorithm that models diffuse energy, ray-tracing is very much view-dependent. Classical Whitted ray-tracing is an extension of ray-casting, where rays are cast from the eye-point into the scene, one per pixel, and, once intersected with an object, the shading of that pixel is determined by the interaction between the surface material and the lights in the scene. Whitted ray-tracing extends the algorithm by casting three additional types of rays once they hit an object in the scene: refraction, reflection, and shadow rays. Since the primary rays originate from the viewer's position, ray-tracing is not a view-independent algorithm, and the shading

of each pixel must be recalculated if the view changes. This is made up for by the fact that shadows, reflections, and refractions are much easier to calculate than with other rendering methods.

Ray-tracing on the GPU has been a difficult topic to implement, as typically it is very branch-heavy computation, and also the classic algorithm is presented using recursion, which is not possible on modern GPUs. Purcell was the first to implement a ray-tracer entirely on the GPU, with no part of the algorithm done by the host processor (Purcell 2004). Purcell accelerated the ray intersection computations by utilizing a uniform 3D grid. Each ray was tested for intersection only against geometry in its current grid cell, before being extended to the next, nearby cell. This model was later followed by Christen (Christen 2005), and Karlsson & Ljungstedt (Karlsson and Ljungstedt 2004). Both Christen and Karlsson & Ljungstedt found their GPU implementations to be comparable but not yet faster than professional CPU implementations, such as Mental Images' "Mental Ray," now owned by Nvidia. Christen notes, at the time of his writing, the limited total memory available on graphics cards might have been a limiting factor.

In an attempt to improve the GPU ray-tracing algorithm, Thrane and Simonsen (Thrane and Simonsen 2005) investigated alternatives to the uniform 3D grid partitioning scheme. They tested the uniform grid, kd-tree, and BVH (bounding-volume hierarchy) implementations. They found that the traditional uniform grid was the slowest, with the kd-tree showing some improvement, but the BVH proving the fastest when all three are traversed on the GPU. The reason for this is because the BVH traversal is simpler than the others, as it contains only one branch (and GPUs were not very

efficient at branches at the time), and that this promotes low divergence in the execution paths of the various kernels (fragment programs), and therefore has good cache utilization.

Building upon Thrane and Simonsen's BVH work, Carr et al. (Carr et al. 2006) rebuild the threaded hierarchy for each frame entirely on the GPU, thus allowing for dynamic geometry and dynamic level-of-detail (LOD). The term threaded hierarchy refers to a technique in which two pointers are added to each node: a hit pointer referring to the first child, and a miss pointer referring to the next sibling. This avoids the traditional traversal reliance on branches and a stack, allowing it to be efficiently streamed to the GPU. Carr et al. conclude that their BVH stored in a geometry image accelerates GPU-based ray-tracing to where it is competitive with other high-performance ray-tracers.

Recent work by Robert et al. (Robert, Schoepke, and Bieri 2007) shows a performance increase of almost a factor of two compared to a CPU-based kd-tree accelerated ray-tracer by utilizing a hybrid technique combining the GPU and CPU. They introduce the *object intersection buffer* (OIB) which circumvents the need for an acceleration structure (such as the aforementioned BVH or uniform grid) for reducing the number of intersection tests for primary rays. Secondary rays such as reflection and refraction rays are computed on the CPU which exploits the parallelism between the GPU acting as a co-processor and the CPU. Shadow rays are avoided altogether and shadow mapping, commonly used in non-ray-traced rendering, is used as an alternative.

Szirmay-Kalos et al. (Szirmay-Kalos et al. 2005) approximate reflection and refraction rays by utilizing the distance stored in the texels of an environment map, and thus are able to simulate ray-tracing without actually tracing rays. The results produce multiple reflections and refractions comparable to ray-traced scenes, and the implementation is suitable for real-time simulations such as games. Additional information can be found in (Szirmay-Kalos, Aszodi, and Lazányi 2006).

# 3.2 Image Processing

Image processing in our context refers to digital image processing, and can involve simple operations such as image resizing and scaling, or more complicated algorithms such as principle components analysis (PCA). Digital image processing techniques are used for a variety of things such as image classification, pattern recognition, and feature extraction. Recent work involves utilizing the GPU for real-time video image processing, but the speedup provided by hardware-acceleration is also helpful in offline computations, particularly for large data sets.

An example of such real-time video processing is the work by Fischer (Fischer 2006), whose dissertation contributes to the area of augmented reality in three specific ways. Augmented reality systems display computer-generated information on top of images from the real world, likely captured by a camera or webcam. The *ARGUS* framework is an augmented reality system used in the medical field for surgical navigation. Fischer extends this framework with a hybrid tracking system, a user interaction library, and a method for calculating the occlusion of rendered objects by a patients' anatomy. Using this extension, it is possible to render a virtual chair partially

occluded by a real-world table in front of it. The second contribution involves something coined *stylized* augmented reality, in which, after the real-world scene is rendered, optionally with virtual objects next to real objects (hence augmented), the scene is post-processed on the GPU to create effects such as cartoon rendering, or the impression that the scene was painted with a paint brush. Edge detection filters are also possible as a post-process. The third contribution involves a new rendering method for the display of hidden structures in iso-surfaces and polygonal models.

Static image processing remains an important topic, with one of the oldest possibly being image denoising. In (Kharlamov and Podlozhnyuk 2007), Kharlamov & Podlozhnyuk utilize Nvidia's GPGPU language CUDA to implement two popular denoising algorithms: K Nearest Neighbors (KNN) and Non Local Means (NLM). They found that while KNN maps well to GPU hardware, NLM is memory-bound where memory accesses are typically implemented as texture fetches on GPUs. They propose a solution that utilizes CUDA's shared memory model that assumes weights within blocks of pixels are constant, for small pixel blocks (such as 8x8). This reduces the number of texture fetches so that (modified) NLM approaches the speed of KNN, and can actually be combined with KNN to achieve even better visual results. Even despite the decreased performance of the original NLM, all three algorithms are capable of running as a real-time filter (used on video, for example) on modern graphics hardware, specifically Nvidia's Geforce 8.

Mathematically, a convolution is an operator that takes two functions and returns the amount of overlap. In image processing, convolutions are useful for certain algorithms such as edge detection, image smoothing, or image blurring. Podlozhnyuk

(Podlozhnyuk 2007, *Image Convolution with CUDA*) implements a separable convolution filter, also using CUDA. The results show that by utilizing CUDA's shared memory, they achieve twice the performance versus an implementation using standard texture fetches. This is a good example of GPGPU languages advancing past general-purpose GPU processing done using traditional GPU languages. For 2D convolution kernels, a separable approach tends to be less than optimal. Instead, FFTs are used to calculate the discrete fourier transformation more efficiently in (Podlozhnyuk 2007, *FFT-based 2D Convolution*). An additional implementation of FFTs on GPUs can be found in (Marichal-Hernandez, Rodriguez-Ramos, and Rosa 2007), where Marichal-Hernandez et al. use FFTs for wave-front reconstruction in adaptive optics systems.

Another possible filtering kernel is the Gaussian, which is computed on the GPU in (Turkowski 2007). Turkowski's implementation is analogous to polynomial forward differencing as he computes the polynomial coefficients on the fly and incrementally. With each state update the coefficients are recalculated with just one vector instruction.

#### 3.2.1 Volume Reconstruction

Volumetric reconstruction involves the creation of 3D models from 2D source material, such as images or pictures. Hornung & Kobbelt introduce a GPU-based reconstruction method (Hornung and Kobbelt 2006) that solves many of the restrictions of previous methods, such as the matching of surface patches, and biased consistency estimation. The improvement over a CPU-based software approach is massive, with an example 126 image set with 16 million voxels reconstructed in 856 minutes on the CPU compared to just 82 minutes on the GPU. The results showed that the data transfer to

and from the GPU was the main bottleneck, and predicted an estimated four times performance increase for texture sizes of 4096<sup>2</sup>, with the maximum available at the time being only 2048<sup>2</sup>. Since then, the current maximum texture size has increased to 8192<sup>2</sup>. For comparison, a recent CPU-based approach is explained in (Habbecke and Kobbelt 2007).

### 3.3 Audio

Sound cards have transformed from external plug-in cards to being integrated into most modern motherboards, and have not followed the exponential growth curve that graphics cards have enjoyed. Yet, processing the acoustics of a complex virtual 3D scene remains computationally expensive. A few novel approaches using the GPU for audio processing and acoustic simulations have emerged.

Audio processing is a specialized form of digital signal processing (DSP), and using the GPU as a digital signal processor to process audio was seen in Gallo & Tsingos (Gallo and Tsingos 2004) and Whalen (Whalen 2005). Whalen notes that many audio processing algorithms, such as bandpass, multi-tap delay, and reverb are iterative methods that require output from previous computation, and are therefore unsuitable for parallelization, or at the very least must be implemented using multiple passes.

Ray-tracing techniques have been adopted for computing room acoustics and sound wave propagation, as seen in Jedrzejewski (Jedrzejewski and Marasek 2004) and Röber et al. (Röber, Kaminski, and Masuch 2007). Jedrzejewski traced 2<sup>14</sup> rays uniformly distributed on the source sphere with all rays propagating until reaching 10 reflections. The CPU implementation took 0.5 seconds to compute, whereas the GPU

implementation took only 32 milliseconds, with half of the time spent uploading transferring textures to the GPU. Röber et al. subdivided the scene into a uniform 3D grid to reduce the number of sound ray-object intersections. They note future improvements could possibly include different acceleration structures to reduce the number of intersections even further. Techniques involving different acceleration structures for GPU-based ray-tracing can be found in § 3.1.1.2.

# 3.4 Computational Geometry

Computational geometry is the study of problems stated in terms of geometry (i.e. points, lines, etc) and can be divided into two main categories: combinatorial computational geometry, sometimes called algorithmic geometry, and numerical computational geometry, sometimes called geometric modeling. Problems in combinatorial computational geometry are many; some examples include convex hull calculation, Delaunay triangulation, line segment intersection, and point-in-polygon tests. Geometric modeling is also called computer-aided geometric design (CAGD), and involves curve and surface modeling. Since many applications of computational geometry involve visualizing the result of computation, it is only natural to attempt to move that computation over to the GPU where it is closer to being rendered, and to benefit from the extreme parallelism available.

Early GPU work in computational geometry involved mesh tessellation.

Boubekeur & Schlick (Boubekeur and Schlick 2005) implement an on-the-fly tesselator by linearly interpolating between three vertices. Their implementation of the curved point-normal (PN) triangle involves a constant amount of data to be transferred to the

GPU, regardless of the target refinement. The main impetus for their algorithm is the lack of dynamically generated vertices on the GPU. Since then, with the introduction of the geometry shader, that is no longer the case. However, the geometry shader is not primarily a tessellation unit, with the maximum number of floating-point dynamic outputs at the time of this writing being only 1024 (with 8 bytes per vertex this only allows 128 vertices generated) per geometry shader invocation. In the future, it is expected that dedicated tessellation hardware will allow much more dynamic output generated entirely on the GPU.

Rong & Tan (Rong and Tan 2006) compute an approximation to the Voronoi diagram of a set of two-dimensional seeds and claim the difference is hardly visible to the naked eye. They implement an algorithm called *jump flooding* on the GPU which they use to compute the Voronoi diagram approximation, as well as an approximation to the distance transform of a set of 2D seeds, in constant time. They give a CPU implementation of their jump flooding algorithm for higher dimensions, with the reason given that the GPU cannot render into 3D textures. Since then, with the advent of shader model 4 and Direct3D 10, this has also changed. This makes a jump flooding in three dimensions implementation on the GPU likely with future work.

Real-time surface deformation and manipulation remains a difficult problem that has recently seen progress thanks to modern GPU technology. Marinov et al (Marinov, Botsch, Kobbelt 2007) perform multiresolution deformations of large meshes almost completely independent of CPU performance, thus taking advantage of the faster advancement of GPUs in relation to CPUs. The method involves approximating the normal field of the deformed mesh using a small number of attributes passed per vertex.

It is stated that simple recomputation of vertex normals by local averaging is impossible due to lack of neighboring vertex information, but with the advent of the geometry shader this approach is possible. In Zhou et al. (Zhou et al. 2007) a solution is proposed for interactive manipulation of subdivision surfaces, including surfaces with geometric textures and displaced subdivision surfaces. The heart of their algorithm involves a shell deformation solver, which replaces the common iterative solver for handling the highly nonlinear data of deformed subdivision surfaces. The algorithm is stable and uses only local operations, making it suitable for GPU implementation. The accompanying video demonstrates the instability of previous solvers, and shows the GPU algorithm being fed motion-capture data that dynamically deforms the models in real-time.

Aiger & Kedem (Aiger and Kedem 2008) set out to solve a geometric pattern matching problem called the *largest common pointset* (LCP) problem. The LCP problem reduces to searching for the depth in a polytopes arrangement, which they compute using depth peeling on the GPU. They demonstrate an application of the algorithm with real-time object recognition in which a given geometry model can be detected in a gray-scale image regardless of translation and scaling of the model.

# 3.5 GPU Algorithms and Data Structures

Many GPGPU techniques are attempts at mapping traditional algorithms and data structures to GPUs so that the computational horsepower and extreme parallelism can be taken advantage of. In section 3.5.1 we take a look at general mathematical problems as well as specific subdomains like cryptography and financial calculations. In section 3.5.2 we touch upon higher-level data structures being mapped to the GPU, as

opposed to low level data structures such as arrays (textures). Section 3.5.3 looks at sorting structures on GPUs.

#### 3.5.1 Mathematics

General mathematics on the GPU covers a wide range, from abstract computation to more practical computation. Banterle & Giacobazzi (Banterle and Giacobazzi 2007) implement the octagon abstract domain efficiently on the GPU, which they then used to create an abstract program analyzer. The octagon abstract domain provides a way to represent a system of inequalities of the form  $\pm x \pm y \le c$ , where x and y are program variables and c is a constant (which can be real, rational, or integer) automatically inferred. Their implementation involves difference bound matrices (DBM) which map one-to-one with 2D textures. The static analyzer performs many operators on the GPU, including union, intersection, assignment, widening, test guard operator, and emptiness test. Many tests see a speedup compared to the CPU implementation, but they state their main bottleneck is the reduction check when performing a widening or emptiness test operation. They state this bottleneck could be alleviated with random writes, which (scatter) can be done with the vertex processor or with a GPGPU language such as CUDA or CAL. Another optimization desired is to increase the size of octagons by using hierarchal techniques such as page textures, which can be implemented using a dependent texture lookup.

In (Harris, Sengupta, and Owens 2007), Harris et al. present a parallel implementation of the *all-prefix-sums* operation, commonly known as *scan*. The all-prefix-sums operation takes a binary associative operator  $\otimes$  with identity I, and an array

of n elements  $[x_0, x_1, ..., x_{(n-1)}]$  and returns the array

$[I,x_0,(x_0\otimes x_1),...,(x_0\otimes x_1\otimes...\otimes x_{(n-2)})]$ . For example, with  $\otimes$  being multiplication, a scan on the array [2,5,3,1,8] would return [0,2,10,30,30]. It is said that there are many applications for scan, including sorting, polynomial evaluation, lexical analysis, and building histograms. In particular, Harris et al. demonstrate scan in use for summed-area tables, stream compaction, and radix sort. Their parallel algorithm is work-efficient in that it does asymptotically no more work than a sequential scan. They benchmark several implementations of the parallel scan, and aside from the GPU speedup over the CPU implementation, the CUDA version outperforms the OpenGL version by up to a factor of seven. This is because CUDA exposes on-chip shared memory, thread synchronization, and scatter writes into memory which are not available in fragment programs (though scatter is at least possible in a vertex program).

Another application of scan is seen in (Lessig 2007), where Lessig computes eigenvalues of a tridiagonal symmetric matrix using a bisection algorithm. Lessig pays particularly close attention to which areas of memory certain operations take place in with two different implementations for different sized matrices: one for matrices of size 512<sup>2</sup> which can fit entirely into CUDA's shared memory cache of 16 KB (for the G80 series), and one for arbitrarily large matrices.

### 3.5.1.1 Random Number Generation

There are many types of pseudo-random number generators (PRNG) and distributions on which to generate the numbers, the classical combination being the linear congruential generator (LCG) on a uniform distribution. Many PRNGs require

high-precision integer arithmetic which, up until recently, GPUs have lacked (usually only obtaining 24 bits of integer precision in a 32 bit floating point number, because integers were not natively supported). Thus, Pang et al. (Pang, Wong, and Heng 2006) proposed a cellular automata (CA) based PRNG that does not require high-precision integer arithmetic or bitwise operations. Testing their CA based PRNG on the GPU against an LCG PRNG on the CPU they achieved on average a ten times speedup, with better results when more numbers are generated (due to GPU-CPU bandwidth, a single random number generated is less efficient than a CPU approach).