# ASYNCHRONOUS LEVEL CROSSING ADC FOR BIOMEDICAL

# RECORDING APPLICATIONS

Kieren Pae

Thesis Prepared for the Degree of

# MASTER OF SCIENCE

# UNIVERSITY OF NORTH TEXAS

August 2021

# APPROVED:

Ifana Mahbub, Major Professor Gayatri Mehta, Committee Member Xinrong Li, Committee Member Shengli Fu, Chair of the Department of Electrical Engineering Hanchen Huang, Dean of the College of Engineering Victor Prybutok, Dean of the Toulouse Graduate School Pae, Kieren. Asynchronous Level Crossing ADC for Biomedical Recording Applications. Master of Science (Electrical Engineering), August 2021, 78 pp., 6 tables, 31 figures, 3 appendices, 51 numbered references.

This thesis focuses on the recording challenges faced in biomedical systems. More specifically, the challenges in neural signal recording are explored. Instead of the typical synchronous ADC system, a level crossing ADC is detailed as it has gained recent interest for low-power biomedical systems. These systems take advantage of the time-sparse nature of the signals found in this application. A 10-bit design is presented to help capture the lower amplitude action potentials (APs) in neural signals. The design also achieves a fullscale bandwidth of 1.2 kHz, an ENOB of 9.81, a power consumption of 13.5 microwatts, operating at a supply voltage of 1.8 V. This design was simulated in Cadence using 180 nm CMOS technology. Copyright 2021 by Kieren Pae

## ACKNOWLEDGEMENTS

This work is based upon work supported by the National Science Foundation (NSF) under grant No. ECCS 1943990.

I would like to thank my major professor Dr. Ifana Mahbub for all of her help and guidance through this project. Her insight was invaluable during my work on this thesis. I would also like to thank Dr. Gayatri Mehta and Dr. Xinrong Li for taking the time to serve on this thesis committee.

Lastly, I would like to thank my friends and family for helping make this possible. Their encouragement and support through this entire process has helped me accomplish this goal of attaining a Master's degree in Electrical Engineering.

# TABLE OF CONTENTS

|            |                                      | Page |

|------------|--------------------------------------|------|

| ACKNOWL    | EDGEMENTS                            | iii  |

| LIST OF TA | ABLES                                | vi   |

| LIST OF FI | GURES                                | vii  |

| CHAPTER    | 1 INTRODUCTION                       | 1    |

| 1.1.       | Biomedical Sensing Constraints       | 1    |

| 1.2.       | Original Contributions               | 2    |

| 1.3.       | Outline of Thesis                    | 2    |

| CHAPTER    | 2 OVERVIEW OF ADC ARCHITECTURES      | 3    |

| 2.1.       | Architectures                        | 8    |

|            | 2.1.1. SAR                           | 9    |

|            | 2.1.2. Pipeline                      | 10   |

|            | 2.1.3. Flash                         | 11   |

|            | 2.1.4. $\Sigma$ - $\Delta$ ADC       | 12   |

| 2.2.       | Synchronous vs. Asynchronous         | 14   |

| 2.3.       | Performance Metrics                  | 18   |

| CHAPTER    | 3 ASYNCHRONOUS ADC DESIGN            | 26   |

| 3.1.       | DAC Design                           | 26   |

| 3.2.       | Comparator Design                    | 27   |

| 3.3.       | Digital Logic                        | 28   |

| 3.4.       | Simulation Results                   | 38   |

| 3.5.       | Comparison With the State-of-the-Art | 46   |

| 3.6.       | Future Work                          | 48   |

| CHAPTER    | 4 CONCLUSION                         | 49   |

| APPENDIX A VERILOGA CODE                     | 50 |

|----------------------------------------------|----|

| APPENDIX B MATLAB CODE FOR DATA MANIPULATION | 53 |

| APPENDIX C MATLAB CODE FOR RMSE ANALYSIS     | 70 |

| REFERENCES                                   | 73 |

# LIST OF TABLES

| 2.1 | Signal Definitions         | 16 |

|-----|----------------------------|----|

| 3.1 | Comparator Summary         | 29 |

| 3.2 | Inputs to Add/Sub Circuits | 33 |

| 3.3 | Ring Oscillator Summary    | 38 |

| 3.4 | DAC Results                | 40 |

| 3.5 | Performance Summary        | 47 |

# LIST OF FIGURES

|      |                                                                            | Page  |

|------|----------------------------------------------------------------------------|-------|

| 2.1  | ADC Block Diagram                                                          | 3     |

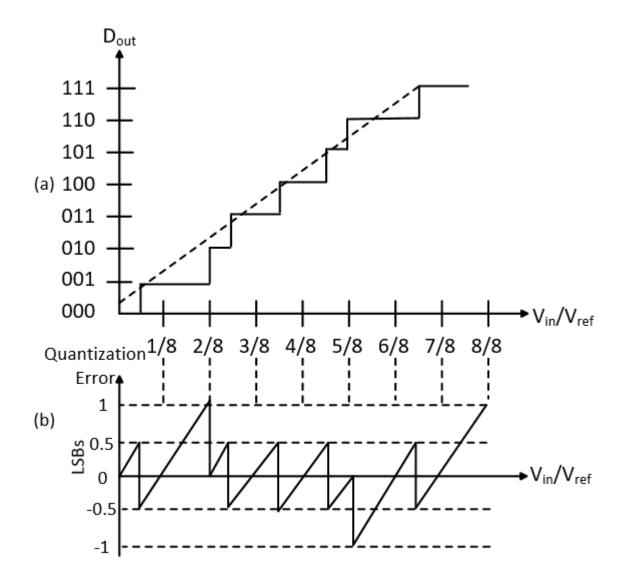

| 2.2  | Ideal ADC example(a) Ideal ADC graph (b) Quantization error                | 5     |

| 2.3  | Explaining the effects of aliasing. (a) Input analog signal (b) Samplin    | ıg    |

|      | function (c) Overall signal (d) Aliasing example                           | 7     |

| 2.4  | Demonstrating the effects of an anti-aliasing filter. (a) Input signal (b) | b)    |

|      | Filtered signal (c) The effect of the filter                               | 9     |

| 2.5  | SAR ADC Architecture                                                       | 10    |

| 2.6  | Pipeline ADC Architecture                                                  | 11    |

| 2.7  | Pipeline Stage Block Diagram                                               | 12    |

| 2.8  | Flash ADC Architecture                                                     | 13    |

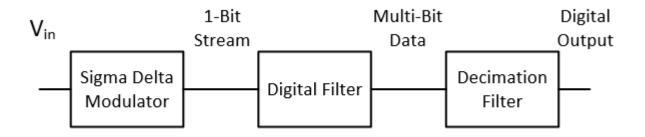

| 2.9  | $\Sigma$ - $\Delta$ ADC Architecture                                       | 13    |

| 2.10 | 2.10 Synchronous vs. Asynchronous(a) Uniform sampling (b) Asynchronous     |       |

|      | level-crossing sampling                                                    | 15    |

| 2.11 | Asynchronous ADC architecture                                              | 16    |

| 2.12 | Demonstrating DNL (a) Nonideal 3-bit ADC (b) DNL illustrated wit           | h     |

|      | quantization error                                                         | 20    |

| 2.13 | Demonstrating INL (a) Nonideal 3-bit ADC (b) INL illustrated with          |       |

|      | quantization error                                                         | 22    |

| 3.1  | DAC block diagram                                                          | 27    |

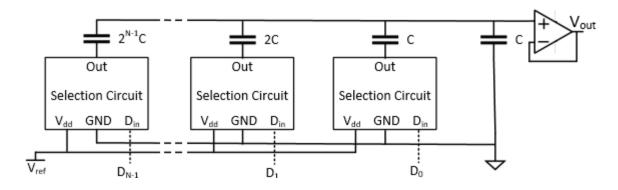

| 3.2  | DAC selection circuit                                                      | 28    |

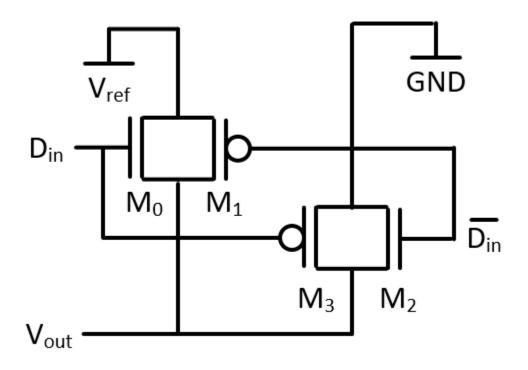

| 3.3  | CT Comparator                                                              | 29    |

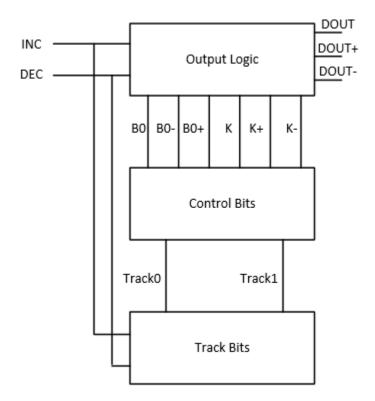

| 3.4  | Digital logic block diagram                                                | 30    |

| 3.5  | Output logic block                                                         | 30    |

| 3.6  | Level crossings in the ADC. Consecutive level crossing (CLC) shown w       | vith  |

|      | black circles. Repeated level crossings (RLC) shown with white circles     | s. 31 |

| 3.7  | Track bits block                                                           | 32    |

| 3.8  | Keeping track of the level crossings. DOUTp = DOUT+, DOUTm = |    |

|------|--------------------------------------------------------------|----|

|      | DOUT-, and DOUT' = new value of DOUT                         | 34 |

| 3.9  | Control bits block                                           | 35 |

| 3.10 | Traditional ring oscillator                                  | 36 |

| 3.11 | Current starved ring oscillator                              | 37 |

| 3.12 | Comparator simulation results                                | 39 |

| 3.13 | DAC simulation results                                       | 40 |

| 3.14 | Ring oscillator simulation results                           | 41 |

| 3.15 | Digital logic simulation results 1                           | 42 |

| 3.16 | Digital logic simulation results 2                           | 43 |

| 3.17 | ADC simulation 1                                             | 44 |

| 3.18 | ADC simulation 2                                             | 46 |

#### CHAPTER 1

# INTRODUCTION

The amount of information being recorded and processed in today's world has never been higher. That amount of information also continues to grow with each passing year. Computers and other digital devices handle the bulk of these processing requirements. Unfortunately for these devices, we live in an analog world, and that fact has led to the analogto-digital converter (ADC) being one of the most important building blocks in today's technology. ADCs take continuous-time (CT) signals and convert them into a form that digital devices can take as an input. The basic operating principle behind this is that the ADC samples the CT signal and outputs the data as bits, which is what the digital devices are looking for as an input to be able to process the information.

ADCs are found in a wide range of devices, including wireless sensors, cameras, audio devices, cell phones, and televisions. Another application for these circuits are found in portable and implantable medical devices. These devices help medical personnel have the information they need to properly diagnose and treat various diseases. The ADCs required for these biomedical devices will be the main focus of this thesis. The following section will continue with a more in-depth look at the requirements for these devices.

#### 1.1. Biomedical Sensing Constraints

As the medical science field grows and evolves, it is only natural for the devices used by medical personnel to also grow and evolve. One great asset already mentioned in this thesis can be found with portable and implantable devices. These allow for a level of information available to doctors that was not possible for most of human history. The designs for these systems, however, are required to be extremely power efficient and have a low silicon footprint [1].

One of the areas that has developed over the recent decades is neurological signal acquisition. These signals can be classified into local field potential (LFP) and action potentials (APs) [2]. APs are the result of activity for a single neuron. LFPs, on the other hand, are generated by superimposition of electrical activity of neurons in the region. The signal characteristics of LFPs are typically in the frequency range of 0.1-250 Hz with a peak amplitude of several mV. For APs, the peak amplitude can be about a few  $\mu$ V and be found in the 0.25-5 kHz bandwidth [3]. A low-power ADC is required to digitize these signals. The typical choice for this process is an SAR ADC with a resolution ranging from 8-10 bits [4]. The SAR architecture is popular because it can meet the demands of biopotential sampling, including low power, low sampling rate, and the resolution criteria. However, due to the time sparse nature of biomedical signals, level crossing ADCs have gained attention as an alternative method [5]. Since this architecture only samples when the signal is active, it has been shown to save power for signals such as this [6].

#### 1.2. Original Contributions

A unique design for a 10-bit level crossing ADC is presented in this thesis. The design utilizes concepts found in literature to reliably process both LFP and APs in neuropotential signals. This architecture uses the concept of level crossings to facilitate a low power design that can still accurately reconstruct the signal. Designs for the digital to analog converter (DAC), comparators, and digital logic are to be presented and discussed.

## 1.3. Outline of Thesis

This thesis is organized as follows. Chapter 2 starts with an exploration of synchronous ADC principles along with some sample architectures in that space. Then a discussion on how asynchronous ADCs are defined followed by a literature review on the work being done in biomedical asynchronous ADCs. After that Chapter 2 wraps up with a discussion of various performance metrics found in the literature. Chapter 3 begins with the discussion on the design for this thesis. Then simulation results are shown with a comparison with the state-of-the-art. The future work that is planned on this project is found at the end of this chapter. Finally, this thesis wraps up in Chapter 4 with the conclusion.

#### CHAPTER 2

# OVERVIEW OF ADC ARCHITECTURES

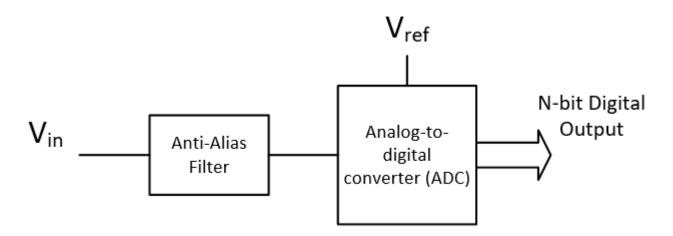

As was briefly mentioned in the introduction to this thesis, an ADC takes a CT analog signal and converts it into a sequence of digital values proportional to the input signal's magnitude [7]. This process is generally much more difficult than the reverse process of taking a digital signal and converting it into analog form [8]. Fig. 2.1 shows a very basic block level diagram of an ADC. The input signal,  $V_{in}$ , is fed into an anti-aliasing filter, which leads to the ADC block with the N-bit digital output. This anti-aliasing filter is not always necessary, and it's function will be discussed later in this section.

FIGURE 2.1. ADC Block Diagram

The N-bit digital output consists of N-bits labeled as  $D_0$  to  $D_{N-1}$ .  $D_0$  corresponds to the least significant bit (LSB) while  $D_{N-1}$  represents the most significant bit (MSB). A typical digital output code is shown in Eqn. 2.1.

$$D_{\rm out} = D_{\rm N-1}...D_1 D_0 \tag{2.1}$$

This digital output that is delivered at the output of the ADC is useless without knowing the code and conversion relationship that is being used in the architecture [7]. The most commonly used code is straight binary (base 2). This results in the LSB having a value weight of  $2^0$ , the next bit's weight is  $2^1$ , up until the MSB value whose weight is given as  $2^{N-1}$ .

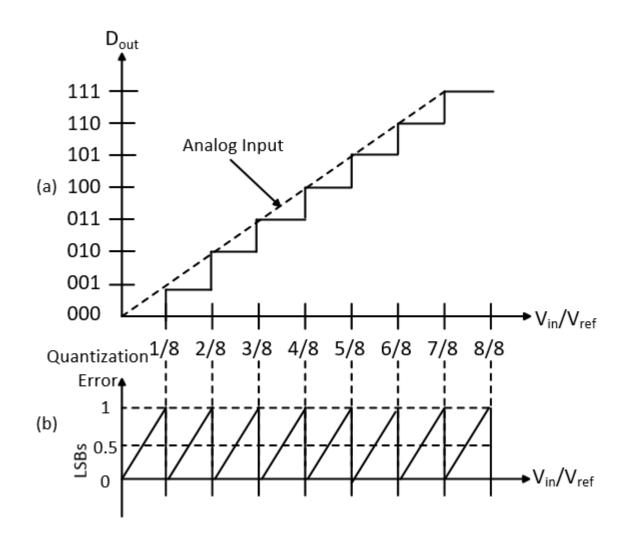

The value of N for the ADC determines the resolution, or in other words how many quantization levels the component will have. The ADC will split the  $V_{ref}$  voltage shown in Fig 2.1 into 2<sup>N</sup> equal parts. As an example to help better explain this concept as well as the digital code discussed earlier an example of a  $V_{ref}$  value of 1.8 V and N being equal to 3 will be used. Now since the reference voltage is split into 2<sup>N</sup> equal parts the value of a change in 1 LSB is  $V_{ref}/2^N$ . Plugging in the values for our example gives us the simple arithmetic of 1.8/8 = 0.225 V. Now that we have our conversion relationship mentioned in [7] as 1 LSB = 0.225 V the binary output code can now be converted to a voltage value. The code to be used in this example is  $D_{out} = 110$ .

Now we take the value of  $D_{out}$  and multiply it by the value of 1 LSB in volts. This is given by  $(110)_2 0.225 \text{ V} = (6)_{10} 0.225 \text{ V} = 1.35 \text{ V}$ . Now this example is admittedly a little misleading because it doesn't take into account the quantization error that arises from this operation. What is meant by this statement is that the actual value of the analog input signal is in the range of 1.35 V to the next quantization value, which is 1.575 V for this system. 1.575 V corresponds to a digital code of  $(111)_2 = (7)_{10}$ . To put it more concisely, with an output code of  $(110)_2 = (6)_{10}$  the real analog input voltage value will be in the range of 1.35 V  $\leq V_{in} < 1.575 \text{ V}$ . Fig. 2.2 will help to further explain this concept.

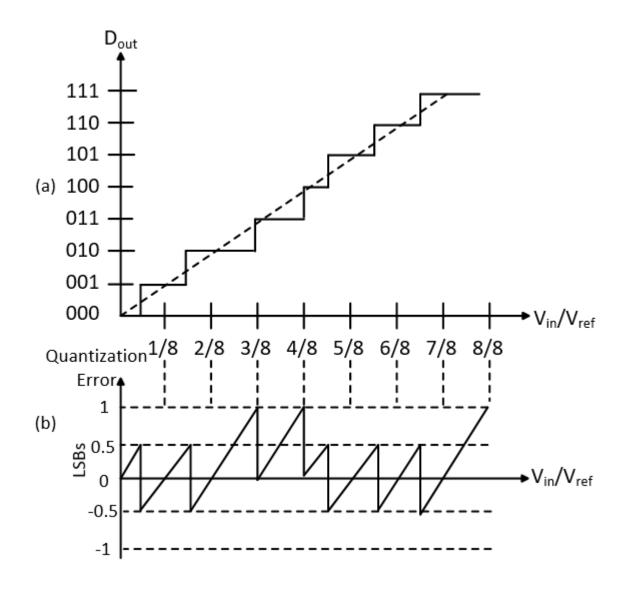

Fig. 2.2(a) shows  $D_{out}$ , digital output, of an ideal 3-bit ADC [8]. The dashed line represents a ramp input from an analog signal while the staircase plot shows how the digital output changes with the aforementioned analog input. The x-axis has been normalized to  $V_{ref}$ . This means that at the ADC's maximum output, corresponding to  $111_2(2^{N}-1)$ , will represent a value of  $V_{in}/V_{ref} \geq 7/8$ .

Fig. 2.2(b) shows how the quantization error changes as the analog input increases [8]. The way to look at quantization error is that it naturally arises due to the differences between analog and digital systems. Digital systems only have a finite number of available outputs, 8 in this case, while the analog input shown theoretically has an infinite number of points on that line. To better explain the quantization concept the part of Fig. 2.2 where  $1/8 \leq V_{in}/V_{ref} \leq 2/8$  will be used as an example. The first points to look at are the edges of this boundary. When  $V_{in}/V_{ref}$  are equal to 1/8 and 2/8 there is a discontinuity in the quantization error graph where it goes from 1 to 0 bits. It can be seen that this discontinuity happens at every boundary for the  $D_{out}$  values. This is simply representing the fact that at exactly those values of the boundaries the digital and analog signals are in complete agreement. Thus the bit error is 0. However, if the signal is below or above the boundaries respectively, then the bit error is almost 1 bit showing that the system is losing almost that entire bits worth of information due to the digitization process.

FIGURE 2.2. Ideal ADC example(a) Ideal ADC graph (b) Quantization error

One of the most important details of synchronous ADC's is the sampling rate the ADC will operate at. This determines how often the ADC samples the CT analog signal and transforms it into the corresponding digital code. The sampling rate,  $f_s$ , will largely be application dependent, but there is one condition that must be met that is well known in literature. Eqn. 2.2 shows the *Nyquist Criterion*. The equation reads that the sampling frequency,  $f_s$ , must be more than two times of the highest frequency found in the analog signal,  $f_0$  [8].

$$f_{\rm s} > 2f_0 \tag{2.2}$$

If this condition is met than there will be no aliasing in the frequency domain of the sampled signal. There will be no way to restore the signal from digital to analog without distortion if the condition in Eqn. 2.2 is not met without using other techniques [9]. One such way to subvert the *Nyquist Criterion* is by using compressive sensing (CS) algorithms. These methods allow the sampling rate to be determined by the signals sparsity instead of it's highest frequency content [10]. This can facilitate a reduction of data rate and power savings for the circuits processing the information [11].

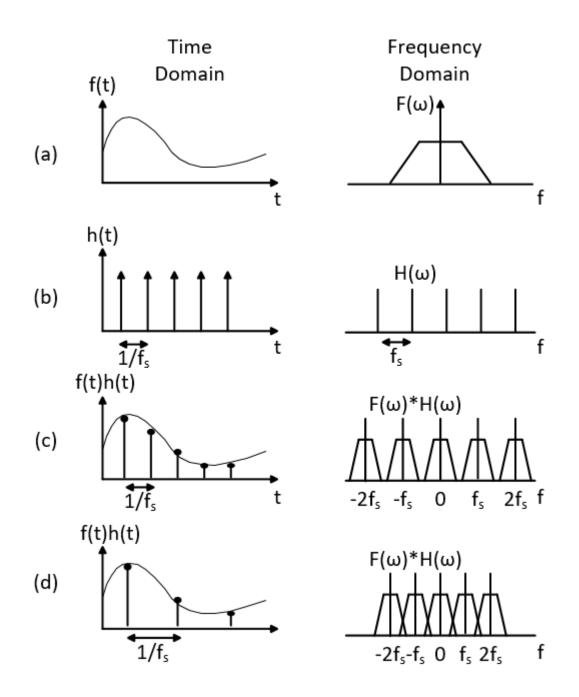

To better explain the Nyquist Criterion Fig. 2.3 will be used to help the reader visualize the aliasing concept. In this figure it can be seen that the signal is represented in both the time and frequency domains, the sampling function consisting of a unit impulse train, as well as two examples of the resulting sampled signal. Fig. 2.3 (a) shows a bandlimited signal with center frequency of  $f_0$ . This means the frequency range shown in the figure contains all of the frequency content found in the signal. As mentioned earlier the unit impulse train shown in Fig. 2.3 (b) represents the sampling function with a sampling period,  $T = 1/f_s$ . This part of the figure is displaying the action of sampling at discrete points in time. In the frequency domain it can be seen that the signals are spaced  $f_s$  apart.

All of the impulses shown have a value of 1 so that when this signal is multiplied with Fig. 2.3 (a), the ensuing signal is given in Fig. 2.3 (c). It can be seen from this part of the figure that the frequency domain representation for the sampled signal is simply multiple versions of the band-limited signal at multiples of the sampled frequency.

FIGURE 2.3. Explaining the effects of aliasing. (a) Input analog signal (b) Sampling function (c) Overall signal (d) Aliasing example

Fig. 2.3 (d) shows that as  $f_s$  is decreased the multiple versions that arise in the frequency domain squeeze closer and closer together. There comes a point where the signals finally overlap and cause the aliasing that been talked about and is shown by the frequency

domain side of Fig. 2.3 (d). The point at which the copies begin to overlap is called the folding frequency [8]. This effect is obviously undesirable as a loss of information occurs with the overlapping. One solution to this problem can be found by taking another look at Eqn. 2.2. The designer simply needs to increase the sampling frequency to avoid the folding effect. This solution may not always be feasible or desirable for an application, which leads to a more elegant solution. That solution comes in the form of an anti-aliasing filter.

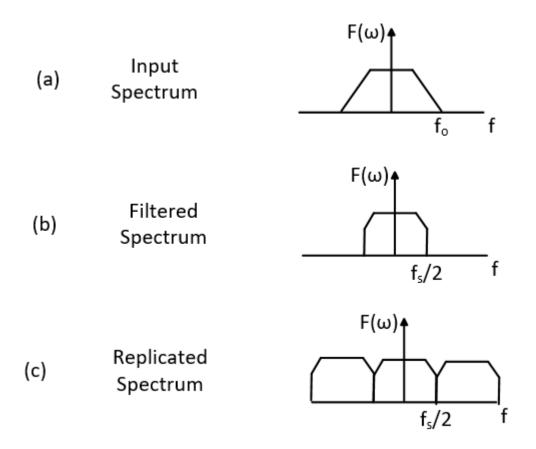

An anti-aliasing filter has a simple working principle. The filter cuts off the signal so as to prevent the information from overlapping as shown in Fig. 2.3 (d). To better demonstrate this principle please refer to Fig. 2.4. It can be seen that the input is the same as the one shown in the previous figure. We are now assuming that the frequency  $f_0$  does not meet the Nyquist criterion. This leads to Fig. 2.4 (b) where it is shown what an ideal case for a filtered signal would be. To prevent folding, the designer simply needs to limit the bandwidth to  $f_s/2$ . This will result in what is shown in Fig. 2.4 (c). When the full spectra in the frequency domain is shown the signals no longer overlap as they would without the filter. While it is clear that there is still a loss of information with this method, the integrity of the signal is still intact. The designer knows that the output of this signal is not tainted by operating under the folding frequency. To meet high performance requirements of today's systems, an anti-aliasing filter must have a strong stop-band suppression, high flatness in the band, as well as a large bandwidth [12].

#### 2.1. Architectures

With the fundamentals of ADCs now explained, we can get into some of the details associated with the different architectures found in the literature. As with all the basic building blocks in engineering and other disciplines, ADCs can be tailored by the designer for their exact specifications. For instance, if a designer values speed over accuracy then the most common solution is to use a Flash ADC [13]. If the system that is being designed for only has signals below 10 MHz, then pipeline ADC is the correct choice [14].

The rest of this section explains these two example architectures in more detail as well as others. While these are not the only architectures found in literature, they were

FIGURE 2.4. Demonstrating the effects of an anti-aliasing filter. (a) Input signal (b) Filtered signal (c) The effect of the filter

chosen to be representative of different requirements that ADCs have in practical designs.

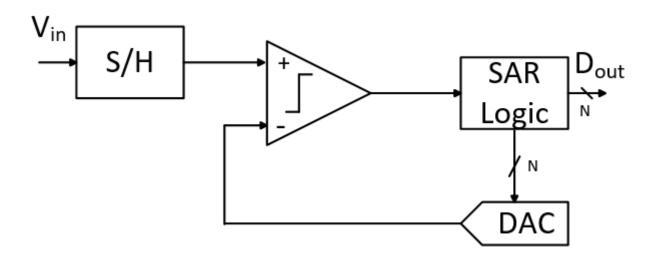

2.1.1. SAR

The first architecture that will be discussed is the successive approximation register (SAR). The SAR ADC architecture is widely used when the application requires high precision and medium speed processing of analog signals [15]. The block diagram for this architecture is shown in Fig. 2.5. The analog input,  $V_{in}$ , is fed to a sample and hold circuit. The output of this circuit is then fed into a comparator. This comparator is instrumental to the working principle of the SAR ADC, which is the binary search algorithm [16]. This algorithm that is carried out by the SAR logic block works as follows. The initial comparison is between the  $V_{in}$  and  $V_{ref}/2$ . In this instance,  $V_{ref}$  is meant to represent a full scale input. If true, then the comparator outputs a logic '1'. Then the algorithm compares the input signal to  $3V_{ref}/4$ . If the input signal is still higher, the SAR logic block compares the input to  $7V_{ref}/8$ . If the input was lower than  $3V_{ref}/4$  then it is compared to  $5V_{ref}/8$ . The binary search algorithm continues in this manner until the resolution of the ADC cannot get any finer.

FIGURE 2.5. SAR ADC Architecture

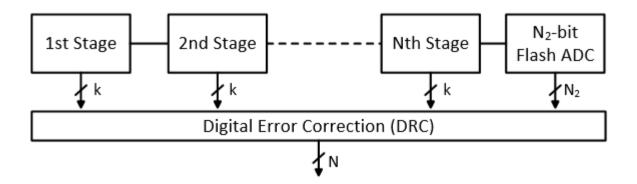

## 2.1.2. Pipeline

Another common architecture that can be found in literature is the Pipeline ADC. This architecture has grown popular due to its good balance between power dissipation, size, speed, and resolution [17]. The Pipeline ADC got its name because of how the stages are connected. As can be seen from Fig. 2.6, the architecture consists of stages that are connected end to end, resembling how a pipeline is laid out.

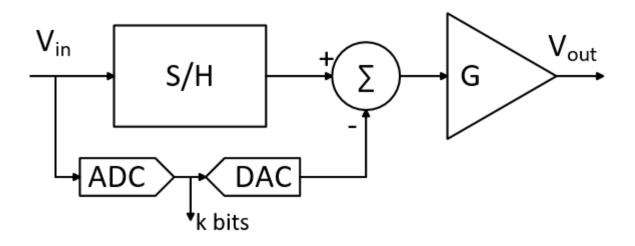

To better understand why the layout is as such, the operation of each stage will be discussed. Fig. 2.7 shows a close up of one of the stages. The input signal  $V_{in}$  is fed into a sample and hold circuit labeled S/H as well as to a sub-ADC. The output of the ADC is fed into the DAC and the digital error correction or similar stage. The DAC output is connected to the summing block which is followed by a gain block that leads to the output of

FIGURE 2.6. Pipeline ADC Architecture

the stage. The S/H, DAC, summing block, and the gain block are usually laid out together in one block called a Multiplying-DAC (MDAC) [18]. Now that the basic structure has been shown, it will be easier to explain what the purpose of each stage is. After the output of the sub-ADC is fed into the DAC and converted into an analog signal, it is subtracted from the original  $V_{in}$  to create a residue voltage [19]. This residue voltage is then gained up and fed into the next stage. The easiest way to look at this architecture is to think about each stage resolving certain bits in the output of the ADC. For instance, the first stage resolves the most significant bits in the output, while the Flash ADC located in the far right of Fig. 2.6 resolves the last N<sub>2</sub> bits in the output of the ADC. N<sub>2</sub> is used to distinguish between the two different N values found in the figure. Simply put, the number of stages, represented by N, does not necessarily have to equal the resolution of the Flash ADC, N<sub>2</sub>.

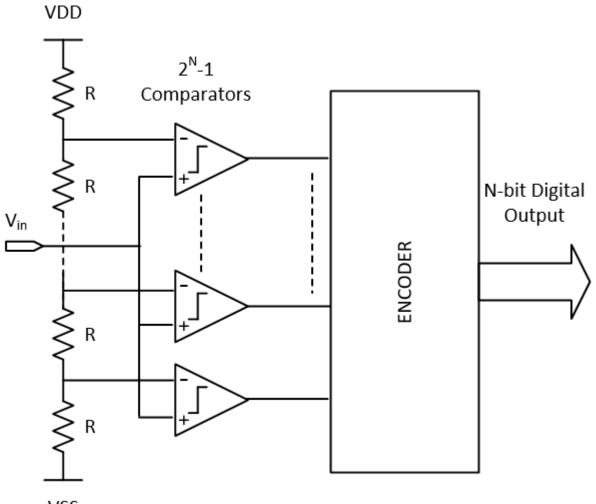

#### 2.1.3. Flash

As mentioned at the beginning of this section, flash analog-to-digital converters are used when speed is the most important factor in the design. This architecture achieves this speed due to the parallel nature of its operation. Fig. 2.8 shows a typical flash architecture.

As can be seen from Fig. 2.8, the architecture comprises of three stages. The first stage is a resistor ladder that sets the reference voltages. The number of resistors used in this ladder is  $2^{N}$ , where N is the resolution of the ADC [20]. These reference voltages are then fed to the second stage of comparators. The number of comparators is  $2^{N}$ -1, which is equal to the  $2^{N}$ -1 reference voltages generated in the resistor ladder. In terms of the ADC, each

FIGURE 2.7. Pipeline Stage Block Diagram

comparator is 1 LSB away from the comparators on either side of it [13]. These comparators output a logic high when the input voltage is higher than the reference voltage. The outputs are then fed into the third and final stage of the architecture which is the encoder. The encoder's job is to take the outputs of the  $2^{N}$ -1 comparators, called thermometer code, and transform them into a binary code [20].

## 2.1.4. $\Sigma$ - $\Delta$ ADC

The last architecture to be discussed for synchronous ADCs is the  $\Sigma$ - $\Delta$  type. This architecture is also referred to as an oversampling ADC in the literature. This name came about from the fact that this method samples the analog input at a rate higher than the *Nyquist Criterion* that was discussed earlier in this chapter. The main home for this type are applications wanting low silicon footprint, low power consumption, and a high resolution [21]. Some of the applications this type is useful for are data acquisitions, communications, and instrumentation [22]. To help explain the architecture, Fig. 2.9 shows some of the basic building blocks. V<sub>in</sub> is processed in the Sigma Delta Modulator block at the sampling rate,  $f_s$ . The output of this block is given as a 1-bit stream of data going to the digital filter. Then the digital and decimation filter reduces the data rate to a more usable value, as well as extract useful information from the stream coming from the Sigma Delta Modulator [23].

VSS

FIGURE 2.8. Flash ADC Architecture

FIGURE 2.9.  $\Sigma$ - $\Delta$  ADC Architecture

#### 2.2. Synchronous vs. Asynchronous

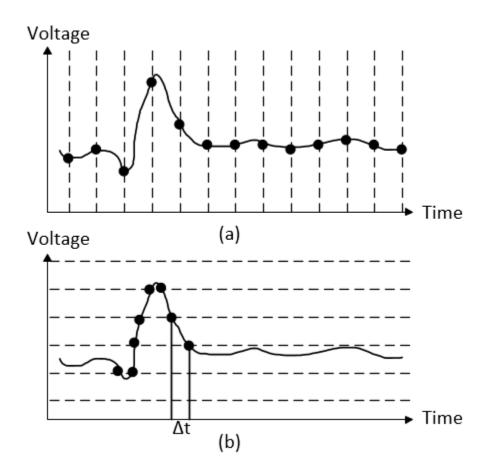

Until now, the focus of this chapter has been on synchronous architectures and concepts. This was important to explain in some amount of detail so that the differences between synchronous and asynchronous ADCs, also called level-crossing ADCs, could be more fully understood. The principle of level-crossing ADCs in literature can be traced back to papers as early as 1966 [24, 25]. At the time, the level-crossing architecture was referred to as delta modulation. This scheme works similar to a flash ADC, with the difference of only using two comparators in its design [26]. Fig. 2.10 will be used to help explain the differences in synchronous vs. asynchronous. Fig. 2.10 (a) shows how a uniform sampling scheme works in ADCs. As can be seen no matter how the signal is behaving, the synchronous system takes a data point, the black circles found on the signal, at every dotted line. The dotted line represents the sampling frequency for our example ADC. The level-crossing example shown in Fig. 2.10 demonstrates how this scheme only takes data points when certain voltage thresholds are crossed. Because of the nature of this method, the time between samples,  $\Delta t$  is also required for reconstruction. This value is kept track of using a timer circuit.

With the fundamentals of asynchronous sampling laid out, the applications for this architecture are easily comprehensible. Systems with signals that have varying activity over time and run on low power resources are suitable for this approach. Applications where this is true can be found in intelligent sensor networks and audio signal processing [27, 28]. These systems only require data transmission when their sensors indicate a significant change in level. One can also infer that speech signals would be a good use case for this approach due to their burst like nature with intervals of silence.

As the title of this thesis would suggest, a level-crossing scheme is well suited for biomedical devices that are wearable and implantable [29]. The time sparse nature for the output of these devices make them the perfect candidate for this technology. This approach can also facilitate a design to compress the output data, further increasing the power saving benefits for these systems [30].

To help explain how the system works more in depth a term I am borrowing from

FIGURE 2.10. Synchronous vs. Asynchronous(a) Uniform sampling (b) Asynchronous or level-crossing sampling

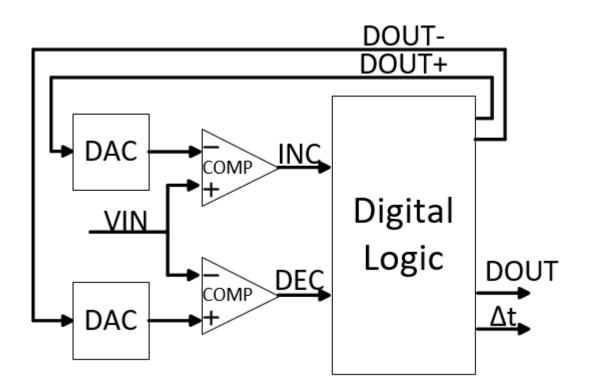

a paper by Agarwal, Trakimas, and Sonkusale will be used [31]. The architecture to be presented is a regular asynchronous method. Briefly put, this simply means that the voltage threshold levels the ADC uses to monitor the input signal only move up or down by 1 LSB regardless of how the input is behaving. The block level diagram for my design is shown in Fig. 2.11.

The figure shows that the architecture has three main components. These are the DAC, the comparator, and the digital logic. The inner workings of these blocks will be explored in the subsequent sections, but for now a discussion of the role each of these have in the overall level-crossing ADC will be had. To explore the interconnections of the block diagram the labels on the signal paths will be defined. See Table 2.1 for the explanations.

FIGURE 2.11. Asynchronous ADC architecture

| TABLE | 2.1. | Signal | Definitions |

|-------|------|--------|-------------|

|-------|------|--------|-------------|

| Signal Label | Purpose                                                 |

|--------------|---------------------------------------------------------|

| VIN          | Input signal                                            |

| INC          | Indicates when the upper voltage threshold has been hit |

| DEC          | Indicates when the lower voltage threshold has been hit |

| DOUT         | 10-bit output of the ADC                                |

| DOUT+        | Sets the upper voltage threshold                        |

| DOUT-        | Sets the lower voltage threshold                        |

| $\Delta t$   | Reports time in between samples                         |

As was mentioned in the table, the design for this thesis was chosen to have a resolution of 10 bits. The operation of the ADC will be described by first assuming that the digital logic block has just taken a sample and has stored the digital output in "DOUT". One of the first actions taken by the logic is to reset the internal timer that keeps track of the value for " $\Delta$ t". After this the logic needs to set to new values for "DOUT+" and "DOUT-" so that the voltage thresholds can be accurately set by the two DACs for the next sample. At this point the digital logic simply waits for either the "INC" or "DEC" lines to go high which signal that a voltage threshold has been crossed and the aforementioned process needs to start again.

As was mentioned earlier in this section, it was important to look at different synchronous architectures to help the reader understand the differences between those and asynchronous systems. While the technical details of the differences have just been laid out, there is another difference worth mentioning and exploring here. That is the different types of sub architectures found in asynchronously sampled biomedical systems. What is meant by this is that Section 2.1 laid out several different methods to synchronously take samples. All of these approaches vary in some fundamental way that changes what application the systems are suited for. For level crossing systems, the recent works have been tweaking the approach and not fundamentally changing how the process works. Some of the optimizations that are presented in prior works will now be discussed.

One of the methods found is the concept of an adaptive resolution [30, 32, 33]. Adaptive resolution means that the ADC can actually change the resolution it operates at. This has been proven to not only save power but also perform data compression, which is another desired feature for this application. This can be achieved in many ways but the principle is the same. In times that the input has a high enough slope, the ADC lowers the resolution so that the voltage thresholds used for comparison do not trigger as often. For instance, in one of the papers the authors designed the system to simply look at the time in between samples and decrease the resolution if they were too close together [30].

Another evolution found in the architecture is the advent of fixed-window comparisons [5, 26, 34, 35, 36]. For the conventional architecture discussed earlier in Section 2.2 a floating window structure is discussed. This simply means that the inputs to both of the comparators change with the input signal as it is moving. With a fixed window system the voltages used

for comparison are fixed, usually around the midpoint of the rail-to-rail voltage. Then whenever a threshold crossing has occurred the input voltage  $V_{in}$  is either subtracted or added to for a newly defined voltage  $V_m$ . This  $V_m$  value is halfway between the fixed voltage thresholds. In essence the tracked  $V_{in}$  is artificially made to stay within the fixed bounds of comparison by resetting the input voltage to  $V_m$  at every level crossing.

One of the biggest power draws for the conventional level crossing architecture are the continuous-time (CT) comparators. One way to improve upon this aspect is the use of dynamic comparators [34, 37]. Dynamic comparators only perform comparison upon receiving a clock signal and therefore only use power during those comparisons, saving power over their CT counterparts. The paper by Ghasemi et. al even goes the extra step by only having 1 comparator in the design to have an even further reduction in power [34].

Another change some designers have made is to replace the DAC circuits with a suitable alternative [33, 37]. A scaler circuit is used in one paper to replace the N-bit DAC [33]. Instead of a DAC circuit to add and subtract to the input voltage  $V_{in}$ , the scaler, as its name suggests, scales  $V_{in}$  based on a novel gain code generator that controls the ratio of the scaling. In the other paper that was cited, an analog memory cell is used for the replacement of the DAC [37]. This memory cell acts as a DAC in their proposed architecture by holding the last voltage level crossed. The paper mentions that the main drawback for this design is the voltage nature and hold times for the cell.

The main design goal for this thesis is being able to acquire the APs mentioned in Section 1.1. One of the often used methods to capture these are a bandpass filter followed by a simple threshold. However, much of the information about the shape of the spikes as well as sub threshold regions are lost [38]. Because of the low amplitudes found in APs, the design will use a 10-bit scheme to reliably capture these signals and will be discussed more in depth in Chapter 3.

#### 2.3. Performance Metrics

#### Mean Squared Error (MSE)

Mean squared error (MSE) is a well known measure of how close two signals are. The typical formula has been taken and adapted to fit with the variables in an ADC [39].

$$MSE = \frac{1}{n} \sum_{k=1}^{n} (V_{\rm in} - V_{\rm out})^2$$

(2.3)

In Eqn. 2.3 n stands for the number of samples,  $V_{in}$  represents the input voltage to the ADC, and  $V_{out}$  is the output voltage of the ADC after interpolating it's outputs.

#### Differential Nonlinearity (DNL)

The differential nonlinearity (DNL) for an ADC is a measure of the difference between non-ideal ADC step size and ideal ADC step size. A succinct view of this concept can be found in Eqn. 2.4 [8].

$$DNL = Actual step width - I deal step width$$

$$(2.4)$$

DNL can be defined with either the units of volts or LSBs. This is a result of the step widths property of being expressed by either of these units. Fig. 2.12 showcases what an example of a DNL would look like.

This figure may look familiar to the reader as it is a modified version of a previous figure in this chapter. That figure showcased the ideal 3-bit ADC. The original ideal case for an ADC is modified in Fig. 2.12 to help show what DNL looks like. Before continuing with the explanation there will be a brief discussion on the notation to be used. When referring to step widths the form  $DNL_x$  will be used, where x is the corresponding  $D_{out}$  value in decimal form. For example,  $DNL_2$  refers to the transition for the  $D_{out}$  value of 010. Now with that better explained a more detailed look at how to actually calculate the DNL will be presented.

As in Fig. 2.2 (b), Fig. 2.12 (b) shows the quantization error expressed in LSBs. For an ideal transition  $DNL_x = 0$ . The ideal transition points for this example can be found in  $DNL_0$ ,  $DNL_1$ ,  $DNL_3$   $DNL_5$ ,  $DNL_6$ , and  $DNL_7$ . One thing to note for these ideal cases is that  $DNL_7$  sticks out when one is looking at Fig. 2.12. This is simply because the ideal transition at this point is 1.5 LSB since this is the maximum value of our ADC.

FIGURE 2.12. Demonstrating DNL (a) Nonideal 3-bit ADC (b) DNL illustrated with quantization error

Now the calculation of the DNL for the non-ideal case will be looked at. It will discuss more in depth momentarily, but the non-ideal step width can be found in DNL<sub>2</sub>, DNL<sub>4</sub>. It can be seen that for  $D_{out} = 2$  that the step width shown is 1.5 LSB. This can be calculated by (3/8) - (3/16). This results in 3/16, and knowing that 1 LSB = 1/8 gives us the previously mentioned 1.5 LSB for DNL<sub>2</sub>. Through a similar process DNL<sub>4</sub> can be found to be equal to -0.5 LSB. One thing to observe is that when DNL = -1 then there is a guarantee that the ADC will have a missing code [8]. This means one of the values of  $D_{out}$  would not have a representation on a graph similar to 2.12 (a). One final note on DNL is that passive element mismatches are typically the cause of non-ideal DNL values [40].

#### Integral Nonlinearity (INL)

As with DNL, a modified version of Fig. 2.2 will be used to help explain integral nonlinearity (INL). This can be seen in Fig. 2.13. The first thing to point out in this figure is the location of the dotted line. Unlike in DNL, for the INL graph the dotted line is positioned to connect the first and last transitions by their end points. This allows us to define INL as the difference between  $D_{out}$  transition points and the straight line while all the other errors are set to zero [8]. The concise way to communicate this can be found in Eqn. 2.5.

## $INL = Actual \ transition \ point - I \ deal \ transition \ point$ (2.5)

To better explain the notation from the discussion on DNL will once again be used where  $INL_x$  represents the  $D_{out}$  value in decimal form. A quick inspection of Fig. 2.13 reveals that there are only two transitions not on the dotted line. This leaves us with  $INL_0$ ,  $INL_1$ ,  $INL_3$ ,  $INL_4$ ,  $INL_5$ ,  $INL_7$  being equal to zero.

We are left with the two points  $D_{out} = 010$  and 110. There are two ways to determine the INL with the graphs given. For INL<sub>2</sub>, one can use Eqn. 2.5 along with Fig. 2.13 (a) to come up with (2/8) - (3/16) = 1/16 or 0.5 LSB. To determine INL<sub>6</sub> we will now look at the quantization graph given in Fig. 2.13 (b). Whenever the error lies outside the  $\pm$  0.5 LSB band it will show where the non-ideal INL resides. As can be seen INL<sub>6</sub> is at -1 LSB, therefore INL<sub>6</sub> = -0.5. INL is also caused by passive element mismatches as well as active block non-linearities [40].

#### Signal to Noise Ratio (SNR)

SNR in ADCs is defined as the ratio of the value for the largest RMS input signal and the noise power [8]. The noise sources include the quantization noise and that of the passive and active devices used in the ADC. The SNR for asynchronous ADCs can be calculated by

FIGURE 2.13. Demonstrating INL (a) Nonideal 3-bit ADC (b) INL illustrated with quantization error

transforming the quantization error in time to an error in amplitude [41]. Eqn. 2.6 shows the result of such an analysis.

$$SNR = 20 \log OSR - 11.2 \, dB \tag{2.6}$$

This was first derived in a work by Sayiner et. al [42]. The term OSR in this equation stands for the clock oversampling ratio. This is calculated by taking the ratio of the timer frequency to the input signal frequency. The formula in Eqn. 2.6 works under the assumption that the value of OSR is high[26].

While this equation can be found in literature, there was an assertion made in [43] that the derivation for Eqn. 2.6 was done incorrectly and produced an erroneous result by a wrong method of calculating average slope and average power in a non uniformly sampled signal. The corrected expression is found in Eqn. 2.7

$$SNR = 20 \log OSR - 14.2 \, dB \tag{2.7}$$

As can be seen the result claims there is a 3 dB overstatement of the theoretical SNR as previously calculated. For the result shown in Table 3.5 the SNR calculation from Eqn. 2.6 will be used. These equations can be compared to the one found in Eqn. 2.8 that shows the SNR for a conventional ADC.

$$SNR = 6.02 \, n + 1.76 \, dB \tag{2.8}$$

In this formula n represents the number of bits for the output of the ADC. As you can see this equation only cares about the number of bits in the design. This makes a good amount of logic sense as in the conventional ADC structure a big source of noise comes from the quantization noise of the voltage, which is directly affected by the value for n in Eqn. 2.8

#### Signal to Noise and Distortion Ratio (SNDR)

This metric is a slightly modified version of the previously shown SNR. The signal to noise and distortion Ratio (SNDR) is defined as the ratio of the value for the largest RMS input signal to the noise and distortion power. This metric includes all distortion and noise sources in the ADC [40].

### Effective Number of Bits (ENOB)

The value for effective number of bits (ENOB) helps quantify how well the ADC performs in terms of the number of bits it can produce effectively. Nonlinearity and component noise will affect the value for this metric [40]. Eqn. 2.9 shows how the ENOB is calculated using the SNDR for the system.

$$ENOB = \frac{SNDR - 1.76 \, dB}{6.02 \, dB} \tag{2.9}$$

This metric is very useful and one that can be seen in much of the literature. It is derived by solving for n in Eqn. 2.8.

#### Figure of Merit (FOM)

This metric is a popular measurement across disciplines. While the exact meaning for a figure of metric (FOM) changes depending on the topic at hand, the rationale behind it is the same. A FOM is used to characterize the performance of a device, system, or method, relative to its alternatives [44]. For ADCs, a FOM is a quantity that describes how much energy is consumed per conversion step. For asynchronous ADCs the FOM is defined as seen in Eqn 2.10.

$$FOM = \frac{Power}{2^{ENOB} * 2 BW}$$

(2.10)

This equation encompasses most of the information for the ADC. By inspection it is easy to see how to design the ADC to improve the FOM. One option that is always good to consider is lowering the power consumption. Another direction to tackle the improvement of the FOM is to increase the value of either ENOB or the bandwidth, BW.

As with the SNR metric discussed earlier, the FOM also has a different version for uniform sampling systems. The only difference between the two equations is that the sampling frequency  $f_s$  replaces the 2BW term for the asynchronous case. This makes a good amount of intuitive sense as  $f_s$  is one of the most important parameters for synchronous sampling schemes.

$$FOM = \frac{Power}{2^{ENOB} * f_{s}}$$

(2.11)

One thing that is rather interesting is how the previous two metrics can be calculated. If you notice the FOM depends on ENOB and the ENOB depends on SNDR. As you can recall the SNDR is a measure of how much noise and distortion is in your system relative to your signal. It's a nice sanity check that these last two metrics, which are the most often cited metrics in literature, can be improved by improving the signal quality which makes a good amount of intuitive sense.

#### CHAPTER 3

# ASYNCHRONOUS ADC DESIGN

In this chapter, we will get into a more detailed look at the design for this thesis. The 10-bit resolution was chosen to help detect the APs in the signal. Assuming the AP can have a  $\mu$ V-level amplitude, as previously stated in this paper, the gain of the amplifier that would precede the ADC block in a typical neural signal recording system would need to be ~60 dB [3]. This puts the amplitude of the AP at a few mV after amplification. Given this requirement, the 10-bit resolution combined with the rail voltage of 1.8 V gives an LSB value of around 1.7 mV and thus is able to capture these events.

#### 3.1. DAC Design

While all of the blocks in this architecture are important, the DAC holds a very important place among the others. This block is responsible for setting up the threshold levels for the comparators based on the "DOUT+" and "DOUT-" 10-bit inputs. The accuracy of the two DACs is a major component of how the overall system performs. This assertion can be thought of intuitively by remembering how the overall architecture works. For conventional level crossing schemes, the error produced in the system is one in the value of " $\Delta$ t" and not the voltage level. So having an accurate output for the DAC to get as close to the ideal case is important to accomplish.

The topology chosen for this design is the popular charge-scaling DAC. While not ubiquitous in the literature for this application, it can be found in various forms over the years [45, 46]. To explain the architecture please refer to Fig. 3.1. As it can be seen from the figure there is a binary-weighted array of capacitors with a total value of  $2^{\rm N}$ C. A digital code  $D_0D_1...D_{\rm N-1}$  is sent to switches connected to the bottom plate of the capacitors. These switches are labeled as Selection Circuit in Fig. 3.1. The selection circuit switches between either V<sub>ref</sub> or ground depending on the corresponding bit in the digital code. This causes V<sub>out</sub> to be a function of voltage division between the capacitors.

To better understand this process one can find a formula to relate the input code

FIGURE 3.1. DAC block diagram

to the output voltage. To derive the equation simply take the impact that each individual capacitor has on the output and use the principle of superposition to get the entire output [8]. The result of such an analysis produces the formula shown in Eqn. 3.1.

$$V_{\rm out} = \sum_{k=0}^{N-1} D_k 2^{k-N} * V_{\rm ref}$$

(3.1)

To verify this equation we will take a simple example and analyze. Let us assume that the digital code consists of all zeros except the MSB  $D_{N-1}$ . This represents half of the range and as such we should expect  $D_{out}$  to be  $V_{ref}/2$ . Plugging into the equation we know that it will be all zeros except for the case when k = N-1. This leaves us with  $2^{k-N}$  as being equal to  $2^{N-1-N} = 2^{-1} = 1/2$ . Therefore the output voltage  $V_{out}$  is equal to  $V_{ref}/2$ , confirming our test case agrees logically and mathematically.

The switches in the selection circuit shown in Fig. 3.1 are realized with a pair of transmission gates shown in Fig. 3.2. Transmission gates are a powerful tool in digital logic designs as they have the capability of passing strong 1s and 0s. When  $D_{in}$  is high, then  $V_{ref}$  is passed to the output. On the other hand, GND is passed to  $V_{out}$  when  $D_{in}$  goes high. Transmission gates typically have a high W/L ratio. Transistors  $M_0$  and  $M_2$  have W/L ratio of 10/1, while devices  $M_1$  and  $M_3$  have a W/L ratio of 20/1.

#### 3.2. Comparator Design

Due to the asynchronous nature of the level crossing method, a continuous-time (CT) comparator is used in most of the literature. This paper is no different. The comparator

FIGURE 3.2. DAC selection circuit

designed for this equation is a Class-A amplifier that sharpens the transitions between 1s and 0s through a pair of inverters at the output [47]. The V<sub>bias</sub> voltage is generated through a current mirror using a bias current of 5  $\mu$ A. Table 3.1 presents a summary of the devices found in the comparator.

## 3.3. Digital Logic

The digital logic block is responsible for handling all the outputs for the system as well as telling the DACs where to set the voltage thresholds. To accomplish this, the block takes the "INC" and "DEC" lines shown in Fig. 2.11 as inputs. The block diagram for the logic is shown in Fig. 3.4.

The block labeled Output Logic controls the output lines of the system. Whenever a threshold is crossed in the system, as indicated by "INC" or "DEC" going high, an internal signal named "Change" is generated. This signal triggers 10 different D flip flops that take the now previous "DOUT" value and save it as a temporary signal "DOUT\_tempX". The X represents the bit of "DOUT" that it has saved. This temp signal is sent to an

FIGURE 3.3. CT Comparator

| Table $3.1$ . | Comparator | Summary |

|---------------|------------|---------|

| Device          | W/L                           | ${ m g_m/i_d}$ |

|-----------------|-------------------------------|----------------|

| M <sub>0</sub>  | $1.4~\mu{\rm m}/500~{\rm nm}$ | 8.92           |

| $M_1, M_2$      | 700  nm/500  nm               | 17.44          |

| $M_3, M_4$      | $1.2~\mu{\rm m}/500~{\rm nm}$ | 15.51          |

| M <sub>5</sub>  | $1.2~\mu{\rm m}/500~{\rm nm}$ | 15.20          |

| M <sub>6</sub>  | 700  nm/500  nm               | 8.32           |

| M <sub>7</sub>  | $1.2~\mu{\rm m}/500~{\rm nm}$ | 0.47           |

| M <sub>8</sub>  | 700  nm/500  nm               | 28.60          |

| M <sub>9</sub>  | $1.2~\mu{\rm m}/500~{\rm nm}$ | 30.83          |

| M <sub>10</sub> | 700  nm/500  nm               | 0.47           |

FIGURE 3.4. Digital logic block diagram

FIGURE 3.5. Output logic block

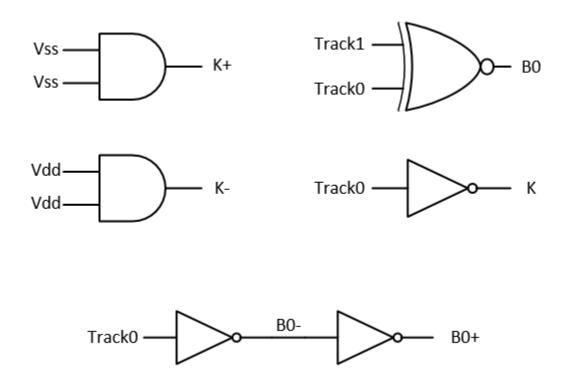

adder/subtractor circuit that has K and B0 as its other inputs. The new value for "DOUT" is set by these parameters. the value of K controls if the block is adding or subtracting, 1 is subtracting 0 is adding, and B0 is the LSB for the number being added to "DOUT" while

all of the other bits on that line are set to 0. After the new "DOUT" is generated, this signal is sent as an output as well as to two more adder/subtractor circuits that handle the generation of the "DOUT+" and "DOUT-" lines. Similar to "DOUT", the "DOUT+" and "DOUT-" signals are controlled with the variables K+, K-, B0+, and B0-. These variables used for the adder/subtractor circuits are generated inside of the Control Bits block found in Fig. 3.4.

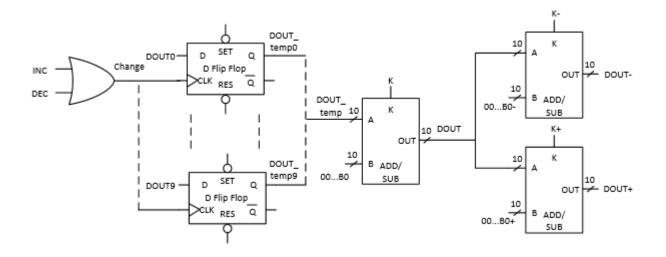

To better explain the logic behind setting the "DOUT+" and "DOUT-" there will be terminology borrowed from a paper by Li et al [26]. For this architecture there are two types of level crossings. These will be coined consecutive level crossings (CLC) and repeated level crossings (RLC).

FIGURE 3.6. Level crossings in the ADC. Consecutive level crossing (CLC) shown with black circles. Repeated level crossings (RLC) shown with white circles.

Fig. 3.6 shows the CLC and RLC concepts in action. RLC can be seen as when the signal comes back on itself and crosses over the previous threshold that was triggered. The CLC is when the signal crosses the threshold that it did not previously cross. Keeping track of this is important as it informs the system as to how "DOUT" is moving.

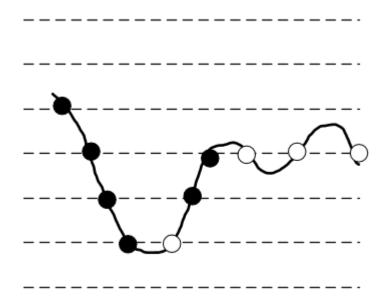

FIGURE 3.7. Track bits block

To accomplish this, the circuit shown in Fig. 3.7 has been employed. This represents the circuits found inside the Track Bits block found in the block diagram. The Track0 and Track1 lines are used for the memory of the level crossings. A pair of D flip flops are used to set these values. As can be seen in the figure the Track1 line is set by the previous level of Track0. At the same time the new Track0 is being set by either the "INC" or "DEC" lines going high. Assuming Set\_Track0 and Res\_Track0 are both low, the output of the NOR gates attached to the SET and RES have a high output while "INC" and "DEC" are low. As soon as either of these lines goes high, however, the respective NOR gate goes low and updates the value for Track0. An upper threshold crossing, indicated by "INC", corresponds to the Track bits being high, while the lower threshold crossing, indicated by "DEC", is represented by the Track bits being low.

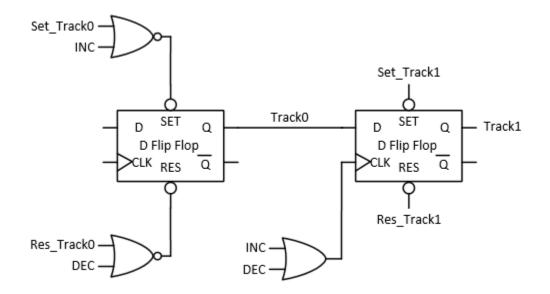

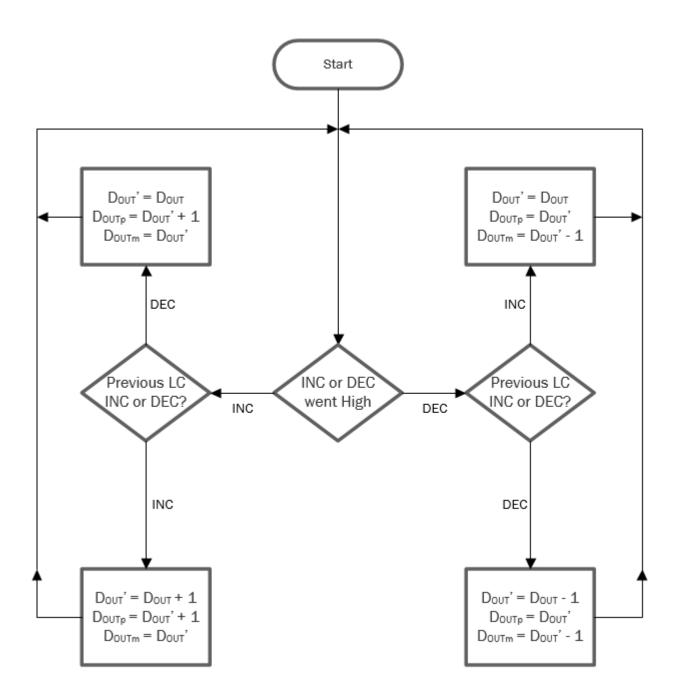

Now that we have a good system to keep track of the RLC and CLC instances, there needs to be a way to convert the Track bits into inputs for the Add/Sub circuits shown in Fig. 3.5. To accomplish this, a flowchart for the logic is shown in Fig. 3.8. DOUTp stands for "DOUT+" and DOUTm stands for "DOUT-". The logic starts off by asking if "INC" or "DEC" has gone high. For either answer, a follow up question of the previous level crossings

value is asked. With these two questions all four of the possibilities are covered. Let us first take the instances where the first and second answers are different, i.e. "INC" to "DEC" and "DEC" to "INC". The actions taken at the end of these branches are very similar. The value for "DOUT" will be the same as the signal crossed the threshold where "DOUT" is already at. Then if the signal was increasing the "DOUT+" line is set to one above the new "DOUT" value while "DOUT-" is set to the new "DOUT" value. A similar process is done if the signal is decreasing but instead the "DOUT-" line is set to one below "DOUT" and "DOUT+" is equal to the new "DOUT".

Now let us look at when the history of level crossings is the same. These branches are found when the sequence is "INC" to "INC" and "DEC" to "DEC". As with the other branches, these two have a very similar function to be performed. As can be seen in Fig. 3.8 when the signal is "INC" to "INC" then we know that the value for "DOUT" needs to increase by one. Then "DOUT+" is set to one above the new "DOUT" and "DOUT-" is the new "DOUT".

Following the flow shown in Fig. 3.8 we now have to create digital logic to accomplish all of these actions. Shown in Table 3.2 is the truth table that was created to help figure out the most efficient logic to achieve this.

| Track1 | Track0 | K | K- | K+ | <b>B0</b> | B0- | B0+ |

|--------|--------|---|----|----|-----------|-----|-----|

| 0      | 0      | 1 | 1  | Х  | 1         | 1   | 0   |

| 0      | 1      | X | Х  | 0  | 0         | 0   | 1   |

| 1      | 0      | X | 1  | Х  | 0         | 1   | 0   |

| 1      | 1      | 0 | Х  | 0  | 1         | 0   | 1   |

TABLE 3.2. Inputs to Add/Sub Circuits

There are many ways to approach designing a digital logic circuit, but in this case using the "don't care" values, represented by X, help to facilitate some patterns that evolve from the table. Before going further with the analysis there will be a brief reminder as to what the values represent. The K, K-, and K+ values control if the ADD/SUB circuits are

FIGURE 3.8. Keeping track of the level crossings. DOUTp = DOUT+, DOUTm = DOUT-, and DOUT' = new value of DOUT

adding or subtracting. The K values for this are 0 and 1 respectively. The B0 terms control the LSB for their respective outputs. The Track bits are there for tracking level crossings where 0 means "DEC" was triggered and an "INC" trigger is shown by a 1. Also the Track0 bit is the most recent crossing while Track1 is the crossing before that. The patterns that jump off of the page immediately are for K- and K+. K- is always high and K+ is always low no matter what the Track bits are doing. So these two values never have to change in the logic. The next bit looked at was K. This was another case where the don't care bits helped greatly in simplifying this logic. K can trivially be described as the inverse of Track0. It should also be pointed out that the other representation is the inverse of Track1, but for this design the Track0 bit was used. For B0, it can be seen that Track0 XNOR Track1 is the best way to describe it. The expression for B0- is simply realized by being the inverse of Track0. In the same vein, B0+ is just the inverse of B0-. Fig. 3.9 shows how all of these bits are laid out with actual logic gates. This figure represents the internals of the Control Bits block found in Fig. 3.4.

FIGURE 3.9. Control bits block

With the "DOUT", "DOUT-", and "DOUT+" logic all described that only leaves

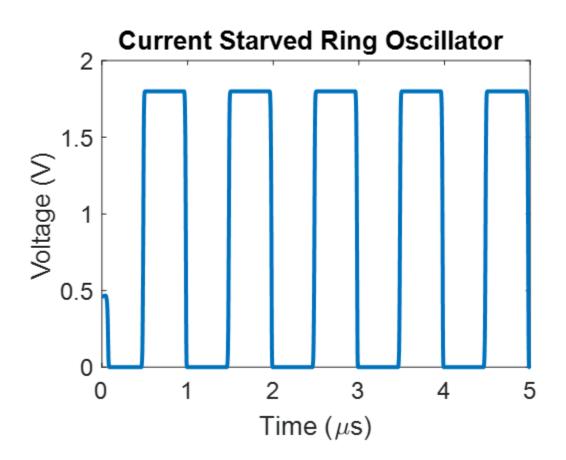

the method for " $\Delta$ t" left to be explained. This was realized through a combination of a ring oscillator and a counter circuit. For the counter circuit, a VerilogA code was written to count up to 10 bits. The code can be found in Appendix A. For the ring oscillator a current starved architecture was chosen. This allows the clock frequency to be set more accurately to the desired speed while designing it.

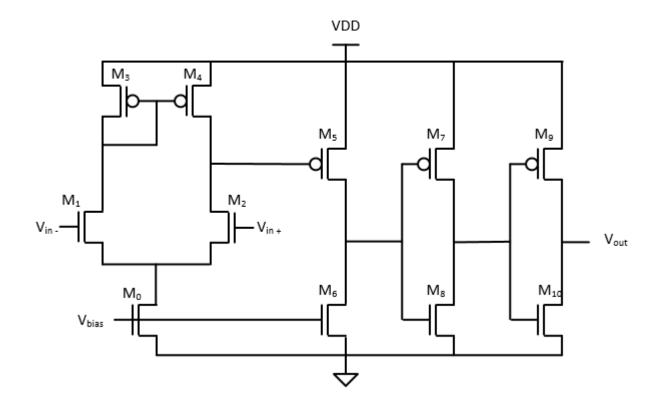

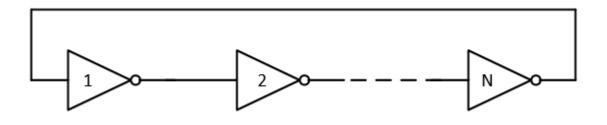

To explain the current starved ring oscillator more effectively a conventional ring oscillator's architecture will first be described. The traditional ring oscillator is comprised of a closed-loop of identical inverter stages that meet the Barkhausen criteria to oscillate [48]. The block diagram can be found in Fig. 3.10. In this figure, N must be odd and greater than 1 to be an effective ring oscillator.

FIGURE 3.10. Traditional ring oscillator

To compute the frequency of oscillation there are only two variables required. One is the total delay time for each inverter stage,  $t_d$ . The other is the number of stages labeled as N. Eqn. 3.2 shows how to calculate oscillation frequency given the previous values [49]. The 2 found in the denominator of the equation accounts for the full low to high and high to low cycle found in the oscillator.

$$f = \frac{1}{2 N t_{\rm d}} \tag{3.2}$$

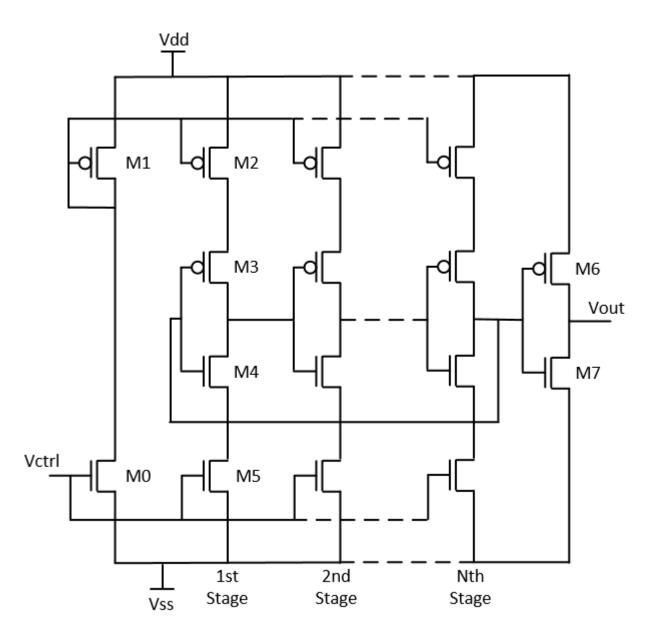

The current starved ring oscillator used has a similar working principle to the previously described traditional architecture with only one difference. The current starved version, as the name suggests, limits the amount of current available to the inverter stages [48]. As the current increases in the system there is less resistance in the transistors producing a smaller delay through each stage.

FIGURE 3.11. Current starved ring oscillator

Fig. 3.11 shows the design. Transistors M0 and M1 form the biasing stage that along with  $V_{ctrl}$  set the current available for each stage. Devices M3 and M4 form the inverter for the stage. M2 and M5 are the transistors that control the amount of current available to the inverter pair for the oscillation. Transistors M6 and M7 form a buffer for the output voltage

$V_{out}$ . Notice that between the N<sup>th</sup> stage and the out inverter that the signal gets rerouted back to the beginning of the circuit to carry on the oscillations. The value for N has the same restrictions found in Fig. 3.10. Table 3.3 shows a summary of the devices found in the ring oscillator circuit. One thing to point out that is not shown in Fig. 3.11 is that a 456 fF capacitor was introduced in between each inverter stage to help shape the delay time for each stage. The value of N was chosen to be 21 and the operating frequency of 1 MHz was achieved with a V<sub>ctrl</sub> voltage of 893 mV.

| Device         | W/L                           | ${\rm g_m/i_d}$ |

|----------------|-------------------------------|-----------------|

| M <sub>0</sub> | $1~\mu{\rm m}/500~{\rm nm}$   | 4.50            |

| M <sub>1</sub> | $3.5~\mu{\rm m}/500~{\rm nm}$ | 4.57            |

| $M_2$          | $3.5~\mu{\rm m}/500~{\rm nm}$ | 2.81            |

| M <sub>3</sub> | $3~\mu{ m m}/500~{ m nm}$     | 5.80            |

| $M_4$          | $1.5~\mu{\rm m}/500~{\rm nm}$ | 7.74            |

| M <sub>5</sub> | $1~\mu{\rm m}/500~{\rm nm}$   | 3.02            |

| M <sub>6</sub> | $1.4~\mu{\rm m}/300~{\rm nm}$ | 4.03            |

| M <sub>7</sub> | 700  nm/300  nm               | 4.74            |

TABLE 3.3. Ring Oscillator Summary

### 3.4. Simulation Results

The design for this level crossing ADC was implemented and simulated using a 180 nm CMOS process with a rail voltage of 1.8 V. This was accomplished using Cadence Virtuoso with the output data exported and processed in MATLAB to show the figures on display in this section. See Appendix B for the code used for processing.

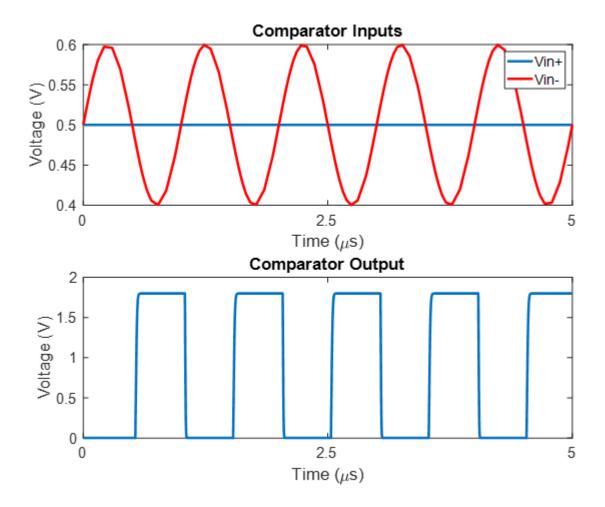

The first simulation to be shown is for the comparator. The attributes to look for are 1) the output is high when Vin + > Vin and 2) the output doesn't take too long to react to a change in Vin+ and Vin-. Fig. 3.12 shows the simulation results. As can be seen the

FIGURE 3.12. Comparator simulation results

comparator is only high when Vin+ is the greater signal and the circuit reacts very quickly to changes in this value.

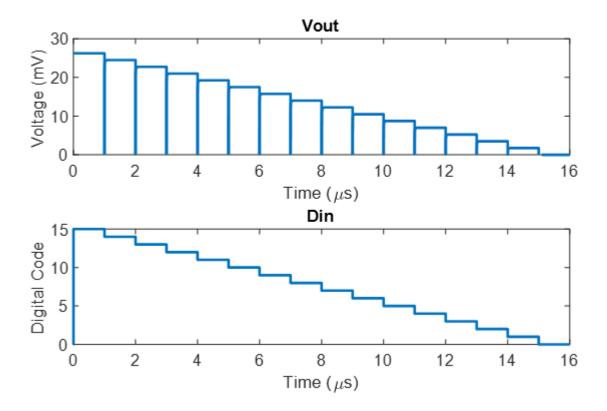

The next result to be shown is for the DAC. The design for this paper as previously mentioned is for 10 bits. With this and the fact of the rail voltage being 1.8 V in mind, we can calculate what an expected jump in the output voltage will be for a 1 LSB increase at the input of the DAC. Plugging these values into Eqn. 3.1 we get that 1 LSB =  $V_{ref}/2^{10} = 1.8/1024 = 1.7578$  mV. Fig. 3.13 shows the simulation output.

Since displaying the full 10 bit range on one graph would be unseemly, only the first 16 digital codes for the DAC are shown. This equates to showing the 4 LSB bits for the device. The results are divided into the output voltage on top and the input code on the

FIGURE 3.13. DAC simulation results

bottom. As can be seen we have the nice staircase effect for both graphs that we would expect. As the input code decreases by 1 LSB at each step, the output voltage decreases by approximately 1.7578 mV. To help illustrate the accuracy of the DAC a comparison of the ideal values and measured ones will be shown. See Table 3.4 for these results.

TABLE 3.4. DAC Results

| Din | Vout Ideal (mV) | Vout Measured (mV) |

|-----|-----------------|--------------------|

| 15  | 26.367          | 26.245             |

| 14  | 24.609          | 24.495             |

| 13  | 22.851          | 22.745             |

| 12  | 21.094          | 20.994             |

| 11  | 19.336          | 19.246             |

| 10  | 17.578          | 17.496             |

As can be seen the ideal case and the measured values agree very well. In fact there is a pattern that emerges from this sample size. The measured values are consistently around 100 nV below what the ideal step values are. This could be used to further increase the accuracy of the ADC by noting what the actual values are in the reconstruction of the signal to be shown later. This thesis does not employ this tactic but it is something to keep in mind when accuracy at that scale is paramount.

FIGURE 3.14. Ring oscillator simulation results

The next simulation to be discussed is for the ring oscillator. The timer resolution for this thesis was chosen to be 1  $\mu$ s so the frequency for this circuit needed to be 1 MHz. This value was chosen so that the design can react fast enough for the high input slope parts of the input signal. The data shown in Fig. 3.14 shows that the oscillator achieves this frequency by repeating every 1  $\mu$ s and thus being suitable for this design.

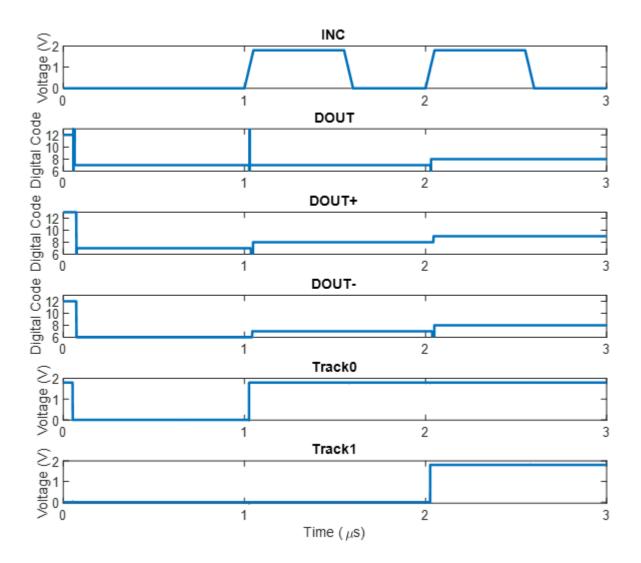

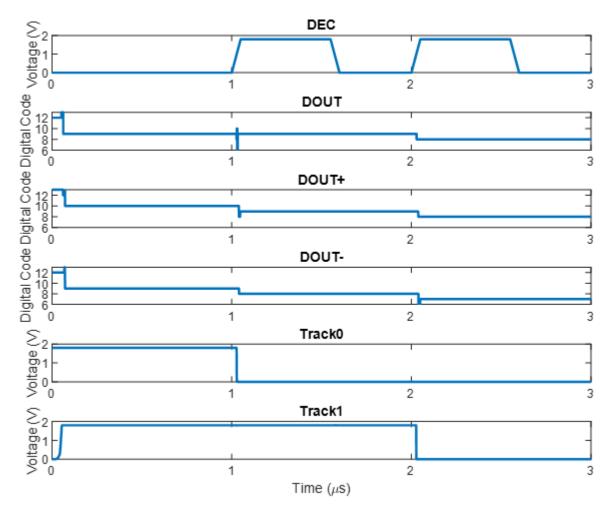

FIGURE 3.15. Digital logic simulation results 1

The last block of simulations to show are for the digital logic. To fully show that the design works as intended, the results have been split into two graphs. The first one, Fig. 3.15, shows when the Track bits both start low and then two "INC" pulses are sent into the circuit. Fig. 3.16 is similar in that it shows the Track bits starting high and then two "DEC" pulses are sent to verify the functionality of the design. One thing to note about Figures 3.15 and 3.16 is that the values at time 0 are the result of the initial states of the simulation and are quickly set to the actual starting values for the analysis.

The first case to be shown is in Fig. 3.15. The Track bits are representing that the

previous two level crossings were both "DEC". With this input to the logic, "DOUT" and "DOUT+" should be the same and "DOUT-" should be 1 below that value. From the simulation you can see that this assertion holds true. Then when the first "INC" pulse is sent at 1  $\mu$ s the value for "DOUT" should stay the same while the "DOUT+" and "DOUT-" lines both move up by one to account for the changing signal. This is also confirmed in Fig. 3.15. The final "INC" pulse for this simulation is sent at 2  $\mu$ s and sets both of the Track bits to high indicating the signal has increased in the past two cycles. For this case all three of the output lines "DOUT", "DOUT+", and "DOUT-" should increase by one and the simulation shows this happening.

FIGURE 3.16. Digital logic simulation results 2

The last simulation to show before the overall results are presented can be found in

Fig. 3.16. In this case the Track bits are initially set to be high, showing that the signal has been increasing for the past two cycles. For this case we expect "DOUT" and "DOUT-" to be the same while "DOUT+" is one above these two. This hold up in the simulation. Then similar to the previous case when the "DEC" signal is sent at 1  $\mu$ s the "DOUT" line will stay the same then "DOUT+" and "DOUT-" will both move down by one. Then on the next "DEC" pulse all three lines move down by one as expected.

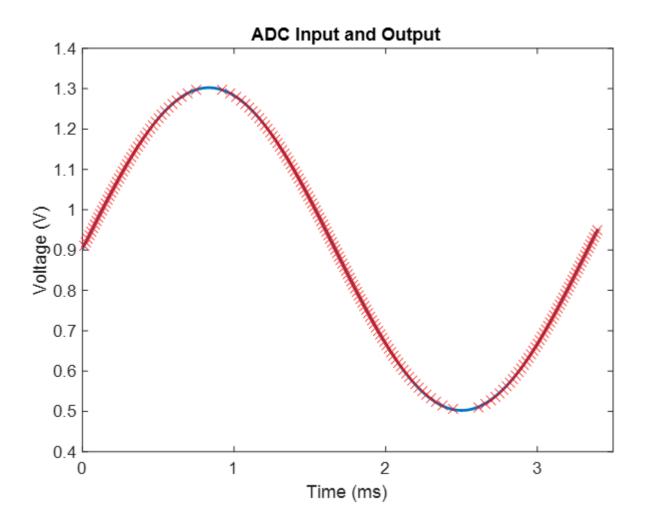

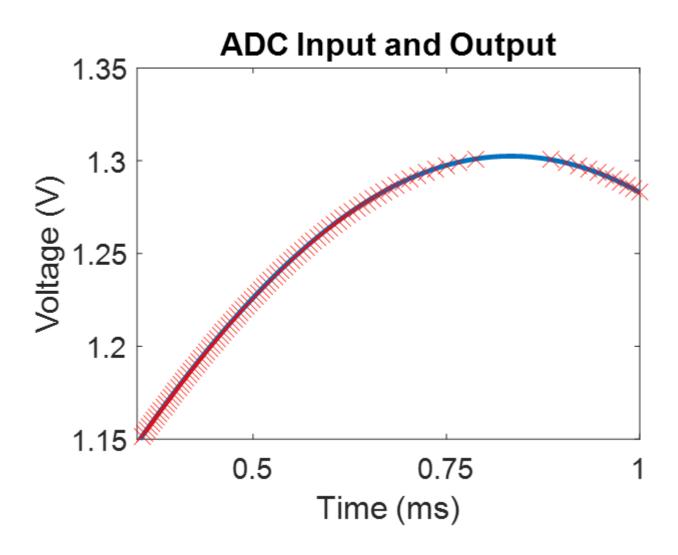

FIGURE 3.17. ADC simulation 1

Now that the individual blocks have been shown to be working as expected it is time to show how the overall ADC performs when integrated together. For this test an input sinusoid with an amplitude of 400 mV with a DC offset of 0.9 V and 300 Hz frequency was used. This amplitude and offset mimics what would be an expected output for an analog front end (AFE) found in biomedical devices. The simulation was performed for just over a full cycle of this sin wave, so about 3.4 ms to be exact. As mentioned in the first part of this chapter the data from this simulation was exported to MATLAB and processed to gather the actual "DOUT" and " $\Delta$ t" values. Appendix B goes into more detail on this process. Fig. 3.17 shows the entire cycle for this test case. The note about this figure is that only 1 in 5 samples is shown so the figure is more legible for this discussion. The full set of samples will be discussed in the next figure to be shown. The solid blue line shown is the actual input signal fed into the ADC. The red X's show a portion of the samples that the ADC took. The exact measurement of the error will be discussed later but to the naked eye there is a great deal of agreement between the ADC and the actual input signal.

Fig. 3.18 shows a more zoomed in look at output of the simulation. Unlike Fig. 3.17 this graph shows all of the samples taken in the ADC. Now the reason to show this zoomed in picture of the output is to verify that the level crossing nature of the designed ADC is functioning as intended. A reminder for the reader is that synchronous architectures do not change the amount of samples taken depending on the input signal. However, for the asynchronous design in this paper we should expect the rate of samples being taken to change as the slope of the signal increases and decreases. From Fig. 3.18 we can see this exact phenomenon happening. At the beginning of the graph the slope of the input signal is at its greatest. The amount of samples being taken in the system is also at its greatest as expected. As the signal begins to taper off at the zenith of the input, the amount of samples slows down and eventually we see a dead area at the absolute top. This is an easy sanity check to show that the proposed architecture is working as intended.

Up until this point the discussion over the results of the ADC and its individual blocks has been mostly qualitative. In the next section we will be taking a more quantitative look at this design as well as compare these performance parameters with the previous works found in the literature.

FIGURE 3.18. ADC simulation 2

## 3.5. Comparison With the State-of-the-Art

Before a comparison can be done we must first define how this design performs. The first metric to be looked at is the root mean square error (RMSE). While this metric isn't used extensively in the literature it used it to verify the accuracy of the ADC that Figures 3.17 and 3.18 suggested it had. To accomplish this an interpolation operation was performed on the outputs of the ADC in MATLAB. Then all of the time values from the input signal were plugged into the polynomial and compared with the actual voltage values found in the input. The code can be viewed in Appendix C. The result of this analysis found that the RMSE of the system was 0.65 mV. This confirms that the ADC has the high accuracy we thought it

had. The error found here can in part be attributed to the quantization error found in the time output.

The power calculation found in the table was calculated without the power drawn from the ring oscillator. Most of the previous works found in literature figures out the time in between samples via an outside source such as a logic analyzer or external clock signal and counter. The bandwidth was found by putting the timer resolution at 0.5  $\mu$ s and estimating the fastest full scale input signal that could be put through the system without multiple crossings in the system. The ENOB and FOM presented in the table are calculated with the theoretical SNR of this system. The equations for these were found in Section 2.3.

| [30]   | [50]                                                                | [37]                                                                                                                                                                       | This Work                                                                                                                                                                                                                                                                                                                                                        |

|--------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.18   | 0.18                                                                | 0.35                                                                                                                                                                       | 0.18                                                                                                                                                                                                                                                                                                                                                             |

| 0.7    | 0.8                                                                 | 1.8-2.4                                                                                                                                                                    | 1.8                                                                                                                                                                                                                                                                                                                                                              |

| 4-8    | 8                                                                   | 4-8                                                                                                                                                                        | 10                                                                                                                                                                                                                                                                                                                                                               |

| Yes    | No                                                                  | No                                                                                                                                                                         | No                                                                                                                                                                                                                                                                                                                                                               |

| 1      | -                                                                   | 1.0-62.5                                                                                                                                                                   | 0.5                                                                                                                                                                                                                                                                                                                                                              |

| 1      | 3.3                                                                 | 1                                                                                                                                                                          | 1.2                                                                                                                                                                                                                                                                                                                                                              |

| 8.4    | -                                                                   | 6-8                                                                                                                                                                        | $9.81^{b}$                                                                                                                                                                                                                                                                                                                                                       |

| $25^a$ | 0.062-106                                                           | 0.6-2.0                                                                                                                                                                    | $13.5^{c}$                                                                                                                                                                                                                                                                                                                                                       |

| 37     | 0.133-0.191.7                                                       | 3.9                                                                                                                                                                        | $6.25^{b}$                                                                                                                                                                                                                                                                                                                                                       |