14.88

DOE/JPL/954689-1

### METALLIZATION OF LARGE SILICON WAFERS

Quarterly Technical Report No. 1, August 26-December 31, 1977

Work Performed Under Contract No. NAS-7-100-954689

Motorola Incorporated Semiconductor Group Phoenix, Arizona

# **U.S.** Department of Energy

#### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency Thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## **DISCLAIMER**

Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.

#### NOTICE

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

This report has been reproduced directly from the best available copy.

Available from the National Technical Information Service, U. S. Department of Commerce, Springfield, Virginia 22161.

Price: Paper Copy \$4.50 Microfiche \$3.00

#### METALLIZATION OF LARGE SILICON WAFERS

QUARTERLY TECHNICAL REPORT No. 1 26 August 1977 - 31 December 1977

JPL Contract No. 954689

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately owned rights.

## Prepared by

Motorola Inc. Semiconductor Group 5005 East McDowell Road Phoenix, Arizona 85008

This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, under NASA Contract NAS7-100 for the U.S. Department of Energy (DOE), Division of Solar Energy.

The JPL Low-Cost Silicon Solar Array Project is funded by DOE and forms part of the DOE Photovoltaic Conversion Program to initiate a major effort toward the development of low-cost solar arrays.

Project 2344

#### **ABSTRACT**

This report covers initial studies on the Metallization of Large Silicon Wafers for the period of 26 August 1977 through 31 December 1977.

A proposed metallization system for large silicon solar cells is outlined and discussed. A baseline process sequence is delineated.

Initial studies of the chemical platiny solutions used for metal deposition are reported. An annotated bibliography of related work is presented.

## TABLE OF CONTENTS

| SECTION | <u>TITLE</u>                                          | PAGE |

|---------|-------------------------------------------------------|------|

| 1.0     | Summary                                               | 1    |

| 2.0     | introduction                                          | . 2  |

| 3.0     | Technical Discussion                                  | 3    |

| 3.1     | Plated Metal Contact Systems                          | 3    |

| 3.1.1   | Electroless Nickel Plating                            | 4    |

| 3.1.2   | Palladium Silicide Formation                          | 7    |

| 3.1.3   | Palladium Plating                                     | . 7  |

| 3.1.4   | Combined Pd <sub>2</sub> Si-Ni Contacts               | 8    |

| 3.2     | Baseline Nickel-Palladium Metallization System (NPMS) | 8    |

| 3.3     | Immersion Palladium Studies                           | 14   |

| 3.4     | Electroless Palladium Studies                         | 22   |

| 3.5     | Literature Survey                                     | 24   |

| 4.0     | Conclusions                                           | 27   |

| 5.0     | Recommendations                                       | 27   |

| 6.0     | New Technology                                        | 27   |

| 7.0     | NPMS Annotated Bibliography                           | 28   |

## LIST OF TABLES

| TABLE | TITLE                                                 | PAGE |

|-------|-------------------------------------------------------|------|

| 1     | Baseline NPMS (Nickel-Palladium Metallization System) | 10   |

| 2     | Electroless Nickel Plating Bath                       | 12   |

| 3     | Electroless Palladium Plating Bath                    | 13   |

## LIST OF FIGURES.

| FIGURE | TITLE                                                                                                                 | PAGE |

|--------|-----------------------------------------------------------------------------------------------------------------------|------|

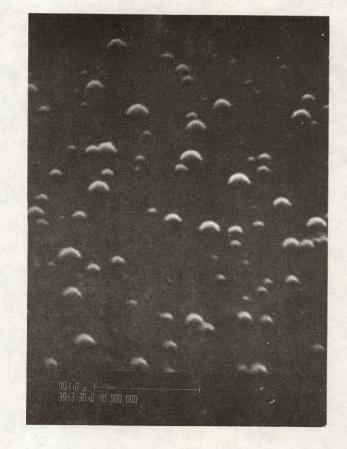

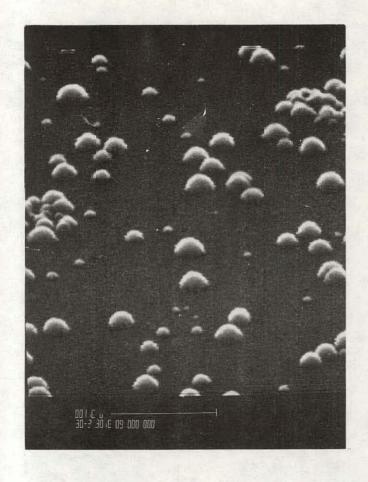

| 1      | Immersion palladium plating at one half standard palladium chloride concentration.                                    | 16   |

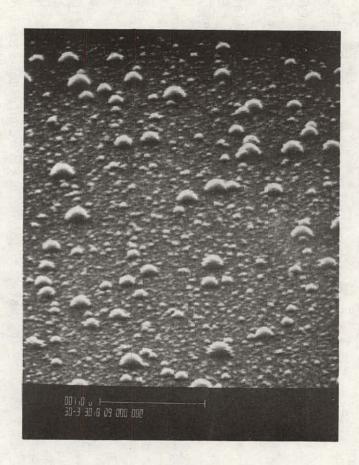

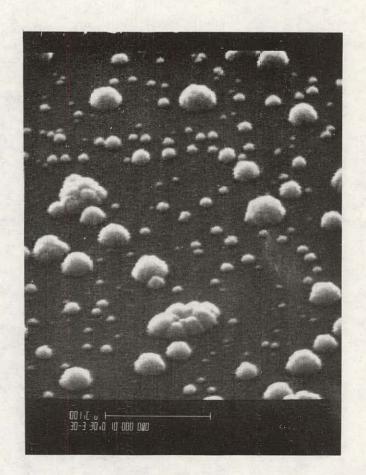

| 2      | Immersion palladium plating at standard palladium chloride concentration.                                             | 17   |

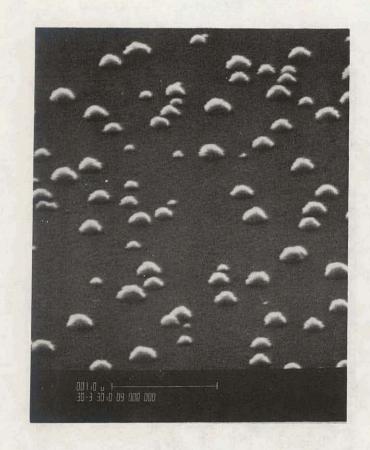

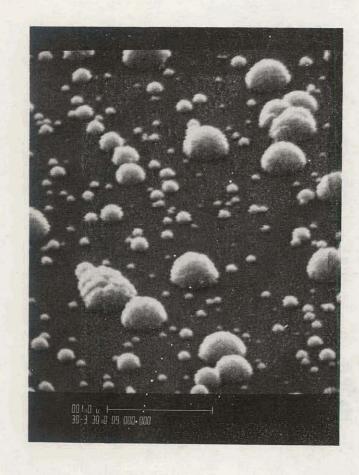

| 3      | Immersion palladium plating at twice standard palladium chloride concentration.                                       | 18   |

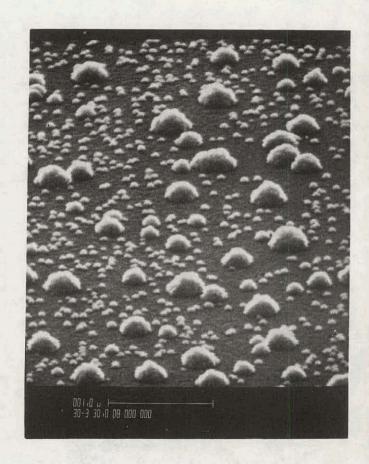

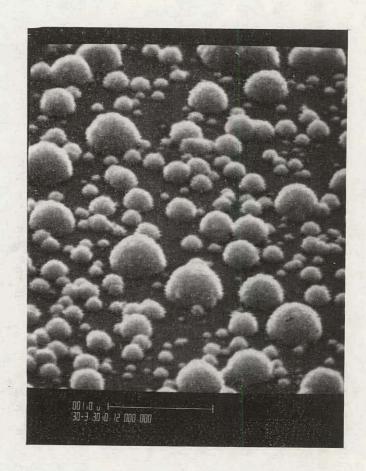

| 4      | Immersion palladium plating at five times standard palladium chloride concentration.                                  | 19   |

| 5      | Immersion palladium plating at five times standard palladium chloride concentration after sintering 15 min. at 700°C. | 21   |

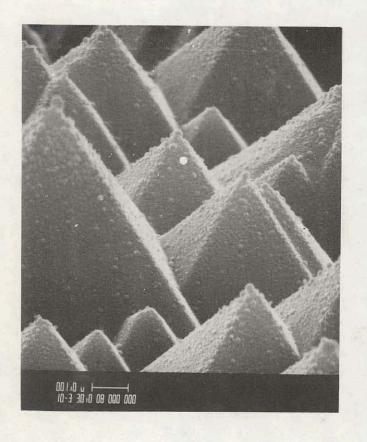

| 6      | Immersion palladium plating on <111> facets of n+ textured front surface.                                             | 23   |

| 7      | Electroless plated palladium layers.                                                                                  | 25   |

#### 1.0 SUMMARY

A proposed metallization system for large area silicon solar cells with shallow junctions is outlined; and its desirable features are discussed. A baseline process sequence for the nickel palladium metallization system (NPMS) is delineated. This baseline process sequence is serving as the starting point from which process variations are being performed. The eventual goal is optimization of the NPMS process and determination of the control ranges for NPMS process variables.

Initial studies of palladium displacement and electroless chemical plating solutions used in the baseline NPMS have begun and progress is reported. It support of this work, an annotated bibliography dealing primarily with palladium plating and palladium-silicon contact formation has been prepared (and will be subject to updating in future reports).

#### 2.0 INTRODUCTION

The Automated Array Assembly Task, LSSA Project, is concerned with a comprehensive assessment of the improvements in existing technology that may be needed to develop an industrial capability for low cost, mass production of very durable silicon solar photovoltaic modules and arrays.

This portion of the project involves investigation, advanced development, and characterization of a method, adaptable to large volume production, for the metallization of large silicon substrates which are suitable for use as terrestrial solar cells. The proposed metallization system is one which can be selectively plated to exposed silicon surfaces with no need to specially protect areas covered with a dielectric (such as an antireflection coating).

The metallization scheme is comprised of three layers. Palladium, through the formation of palladium silicide at elevated temperatures, forms the ohmic contact to the silicon surface. Nickel, plated on top of the palladium silicide/palladium layer, forms a solderable interface. Lead-tin solder on the nickel provides high conductivity at low cost, allows a convenient means for interconnection of cells, and yields some additional degree of protection against deleterious effects resulting from moisture ingression.

It is expected that this nickel-palladium metallization system (NPMS) will be cost effective and exhibit superior reliability.

#### 3.0 TECHNICIAL DISCUSSION

#### 3.1 PLATED METAL CONTACT SYSTEMS

Plated contacts, particularly those incorporating electroless nickel, have been utilized in the past for solar cells as well as in other semiconductor metallization applications. While plated nickel contacts still find broad utilization in very deep junction devices, such as some silicon rectifier products, lack of plating control and rapid solid state diffusion of nickel into silicon have caused problems requiring plated nickel contacts for solar cells with shallow junctions to be largely supplanted by other metallization techniques. Experience in the solar cell industry has shown that it is difficult to control consistency of both the electroless nickel plating rate and adherence of the resulting plated nickel to the solar cell surface. A heat treating (sintering) cycle can be used to promote adherence of nickel to silicon, but solar cell current-voltage characteristic degradation can occur by diffusion of nickel into the p-n junction region, lowering cell fill-factor and efficiency.

Provided that control and reliability are good, however, plated contacts offer distinct advantages over all other metallization techniques for solar cells. The plated contact requires a relatively small capital investment, is amenable to both batch and continuous type processing, and is the most tolerant with respect to varying surface structure. Future solar cells will be fabricated on large area sheets of silicon which will be thin and may not be flat and smooth. In fact, it is anticipated that such future silicon substrates for solar cells will have varying degrees of curvature, taper, warpage, surface ripple, and surface texturing. A plated contact scheme which gives satisfactory performance today will be directly applicable to such future cells.

If a solderable metal film such as nickel is formed as part of the plating sequence, the contacts can be coated with a thick solder layer to provide both an inexpensive conductor and an additional degree of environmental protection.

Energy R&D Department has evolved solar cell fabrication processes designed to be compatible with plated metallization. Prior to metallization, an anti-reflection coating, which passivates the p-n junction perimeter and the silicon surface, is formed on the solar cell. The desired metal contact areas can then be exposed photolithographically, patterning the antireflection coating (utilizing collimated light with either projection or proximity alignment methods, both of which are relatively insensitive to surface topology). If the metal plating reactions are selective, plating occurs only on the exposed silicon surface where the antireflection coating. Thus, the metal contacts are formed only where desired.

In plating metal contacts to exposed silicon, autocatalytic (electroless) plating reactions and displacement (immersion) plating reactions have advantages over electrolytic plating techniques, which require external electrical contacts to the solar cell while plating and which are inherently nonuniform in the presence of internal p-n junction structures (giving variable current densities) and wherever the contact geometry incorporates long lines.

#### 3.1.1 ELECTROLESS NICKEL PLATING

Nickel is a desirable contact because it is solderable and is capable of making ohmic contact to silicon. However, two major problem areas have

limited the use of electroless nickel for solar cell contacts. The first major problem area is uniformity control and repeatability of the plating process itself; the second problem area is ensuring good contact adherence, especially to shallow junction devices. Both of these problems contribute to questionable reliability.

The most appropriate electroless nickel bath for silicon contact application was found to be the ammonia-type, basic (high pH) bath utilizing sodium hypophosphite as a reducing agent. On a bare silicon surface, the basic bath plates more readily, consistently, and uniformly than acidic (low pH) baths. It has been observed, however, that the basic bath can chemically attack the silicon surface, forming a thin film between the silicon surface and the nickel layer. This film has been analyzed and found to be primarily SiO<sub>2</sub>. It is postulated that, during plating of electroless nickel onto a bare silicon surface, some amount of this thin oxide layer is always formed and that its thickness and uniformity are the major variables in the control of electroless nickel plating on silicon. The formation of this film is dependent upon temperature, composition, degree of activation, and pH of the plating bath. The interrelations of these bath parameters are complex and not always predictable.

The rate of plating from common electroless nickel baths is highly dependent upon the type and (surface) concentration of the silicon dopant. Heavily boron doped surfaces, for example, plate at a much lower rate than lightly doped surfaces under some bath conditions. Bath components can be adjusted to essentially eliminate such plating rate differences, usually at the expense of bath life or efficiency, however.

As plated on silicon, electroless nickel may exhibit limited adherence and poor contact resistance, probably due (at least in part) to the presence of an oxide layer between the silicon and nickel. Normal procedure is to heat treat the solar cell to allow nickel diffusion to penetrate through any oxide layer and to form a nickel silicide layer. The silicide formation requires interdiffusion of the nickel and silicon.

Part of the difficulty in controlling nickel-silicon interdiffusion is that formation and growth of the nickel silicide interface is primarily a result of the movement of nickel atoms through the existing silicide and into the silicon. On the order of 95% of the atomic motion is contributed by the nickel. \*,B10 Moreover, the first silicide formed is Ni<sub>2</sub>Si, which will transform at temperatures greater than 350°C into NiSi. The NiSi region is initiated at the Ni<sub>2</sub>Si-Si interface. This indicates that the binding energy of Ni<sub>2</sub>Si is not particularly strong and that nickel diffusion may occur well beyond the Ni<sub>2</sub>Si-Si interface.

If nickel penetrates to the region of a p-n junction, minority carrier lifetime near the junction decreases, junction characteristics degrade, and solar cell efficiency decreases. This phenomenon is seen primarily as an excess forward current which decreases the solar cell fill-factor. Too deep a nickel penetration can severely degrade solar cell efficiency.

On the other hand, nickel contact strength is strongly dependent upon adequate nickel silicide formation. In order to ensure this formation, a minimum time at an elevated temperature is required. In the case of very shallow junctions, formation of adequate nickel silicide for strength may

Reference numbers cited, such as B10, are to be found in the NPMS Annotated Bibliography, Section 7.0 of this report.

automatically mean sufficient nickel diffusion in advance of the nickel silicide layer to degrade the p-n junction. As a result, a fine line exists between contact reliability and solar cell efficiency for electroless nickel plated contacts.

#### 3.1.2 PALLADIUM SILICIDE FORMATION

Like nickel, palladium forms a silicide at temperatures as low as  $200^{\circ}\text{C}$ . However, the kinetics and mechanism of formation of the low temperature compound,  $Pd_2\text{Si}$ , are quite different from those of nickel silicides. First, marker experiments have shown that the interdiffusion of palladium and silicon occurs with nearly equal rates, silicon moving somewhat faster than palladium  $^{810}$ . Second, once  $Pd_2\text{Si}$  is formed, it is stable. Further time or increased temperature, at least up to  $500^{\circ}\text{C}$ , leave the layer unchanged  $^{818}$ . This indicates a reasonably strong binding energy for the intermetallic compound and a self-limiting depth of palladium diffusion. Further,  $Pd_2\text{Si}$  grows epitaxially at all temperatures on <111> silicon surfaces, indicating minimal stress at the silicide-silicon interface  $^{87}$ . These differences between palladium and nickel silicides give rise to the possibility that palladium contacts may provide excellent contact adherence while, at the same time, preserving p-n junction characteristics.

#### 3.1.3 PALLADIUM PLATING

Palladium may be selectively plated from at least two separate types of plating baths: an electroless bath, similar in composition and action to the basic nickel electroless bath, and a displacement type (immersion) bath. Experiments are being performed with both types of palladium plating baths.

Performance of an electroless palladium bath is quite similar to its nickel counterpart, and it does present some difficulties when used to plate bare silicon surfaces. Just as for electroless nickel baths, the plating rate depends dramatically on the type and conductivity of the silicon surface—the p+ back of an n-on-p solar cell is much more difficult to plate than the n+ front. In fact, good electroless plating on both solar cell surfaces has not yet been readily obtained without some surface preparation step, such as sensitizing with a displacement palladium (immersion) solution.

## 3.1.4 COMBINED PdoSi-Ni CONTACTS

Since palladium is more expensive than nickel, palladium may be utilized to form a  $Pd_2Si$  ohmic contact layer with a subsequent nickel layer providing a solderable contact surface. Electroless nickel will plate readily to both palladium and  $Pd_2Si$ . Plating occurs at relatively equal rates on  $Pd_2Si$  formed on silicon with different doping concentrations and types, eliminating the need to modify nickel baths to plate n+ and p+ regions simultaneously.

In addition to being relatively inexpensive, nickel provides a solderable surface which has very low rates of dissolution into lead-tin solders.

This characteristic allows for a wide control range of solder time and temperature, both in solder coating the solar cell metallization and in any subsequent reflow (or other high temperature interconnection) operation.

#### 3.2 BASELINE NICKEL-PALLADIUM METALLIZATION SYSTEM (NPMS)

Drawing upon observations discussed in preceding sections, a plating system is proposed to allow selective application of metal contacts to all exposed solar cell surfaces. The application is selective, in that metal

is applied (in additive fashion) only to those areas on which metal is desired to form a contact grid pattern, without the need to remove any metal. The proposed system is the "nickel-palladium metallization system" (NPMS). This system consists of three "layers" upon the silicon substrate: a palladium silicide/palladium first layer, a nickel second layer, and a lead-tin solder third layer.

In developing a feasible NPMS process sequence, care must be exercised at any step where a nickel layer undergoes a high (i.e., greater than approximately 250°C) temperature cycle. If the palladium/palladium silicide layer is not totally continuous, nickel can penetrate the junction, the amount of penetration depending on the time and temperature of sinter.

Experiments with solar cells have shown that extremely adherent contacts can be made by forming a layer of  $Pd_2Si$  upon which nickel is plated and soldered with no additional heat treatments after the  $Pd_2Si$  formation. Cells fabricated with this technique have been subjected to metal layer pull tests which resulted in failure due to silicon substrate fracture rather than lack of metal layer adhesion.

However, contacts to some test cells constructed in this manner have not proven that strong. Since the principal variable is not presently recognized, the baseline NPMS process includes a low temperature "bake" cycle after nickel deposition and before solder.

Listed in Table 1 is an outline of process steps which constitute the baseline NPMS sequence. This sequence has been shown to be feasible, and has provided a starting point for investigation of individual process steps and process variables. In developing a production-worthy process, some steps in the baseline NPMS sequence may be changed or even eliminated. Times and temperatures for chemical cleaning and plating steps and for thermal

TABLE 1

BASELINE NPMS (NICKEL-PALLADIUM METALLIZATION SYSTEM)

STARTING POINT: a) Solar Cell with AR Coat,

- b) Metal Pattern Etched Through Front Dielectric,

- c) Back Dielectric Totally Etched Away.

| STEP | PROCESS                           |

|------|-----------------------------------|

| 1    | Immersion Plate, Thin Pd Layer    |

| 2    | Sinter 5 Minutes @ 600°C          |

| 3    | Scrub Back to Remove Free Pd      |

| 4    | Electroless Plate, Thin Pd Layer  |

| 5    | Sinter 30 Minutes @ 600°C         |

| 6    | Electroless Plate, Thick Ni Layer |

| 7    | Bake 30 Minutes € 220°C           |

| 8    | Solder Dip 60-Sn/40-Pb Solder     |

All "Sinter" and bake steps to be in forming gas.

treatment cycles are certainly primary variables and have not yet been optimized. Production control limits for chemical plating solutions must be established and bath constituents must be optimized.

Electroless palladium and electroless nickel plating solutions which work with the baseline NPMS process of Table 1 are listed in Tables 2 and 3. These formulations are taken from Modern Electroplating A3, which references the original studies in the literature by Brenner and Riddell C1 and by Pearlstein and Weightman C5.

Success of the NPMS depends critically on performance of the immersion palladium plating step, and considerable effort must be devoted to its understanding and control. The immersion palladium bath must consist essentially of PdCl<sub>2</sub> in a solution which permits effective plating of silicon surfaces while simultaneously attacking any native silicon oxides present to enhance generalized plating.

As stated earlier, the baseline NPMS process may be subject to drastic change to make it more production worthy. For example, studies are being conducted to determine if the first three steps might be eliminated in favor of a single step which appropriately sensitizes the silicon surface to obtain a uniform, continuous electroless coating. (That is the sole reason for the existing steps 1, 2, and 3.) In the present step 3, some palladium which is not reacted to form  $Pd_2Si$  is removed from the back contact surface of the solar cell. This allows a more effective and intimately adherent coating to be formed in step 4, but is undesirable for incorporation in future low cost processes.

TABLE 2

ELECTROLESS NICKEL PLATING BATH

## Bath Constituents

| Nickel Chloride      | NiC1 <sub>2</sub> .6H <sub>2</sub> 0                               | 30 g/I |

|----------------------|--------------------------------------------------------------------|--------|

| Sodium Hypophosphite | NaH <sub>2</sub> P0 <sub>2</sub> ·H <sub>2</sub> 0                 | 10 g/I |

| Sodium Citrate       | Na 3 <sup>C</sup> 6 <sup>H</sup> 5 <sup>O</sup> 7·2H2 <sup>O</sup> | 84 g/I |

| Ammonium Chloride    | NH <sub>4</sub> CI                                                 | 50 g/I |

ENOUGH NH4OH IS ADDED TO MAINTAIN BATH PH BETWEEN 8 AND 10

MAXIMUM OPERATING TEMPERATURE: 95°C

<sup>\*</sup>REFERENCE NO. A3, page 713

TABLE 3

ELECTROLESS PALLADIUM PLATING BATH\*

## Bath Constituents

| Palladium Chloride   | PdC1 <sub>2</sub>                                  | 2   | g/I  |

|----------------------|----------------------------------------------------|-----|------|

| Hydrochloric Acid    | HCI (38%)                                          | 4   | m1/1 |

| Ammonium Hydroxide   | NH <sub>4</sub> OH (25% NH <sub>3</sub> )          | 160 | m1/1 |

| Ammonium Chloride    | NH <sub>4</sub> CI                                 | 27  | g/I  |

| Sodium Hypophosphite | NaH <sub>2</sub> PO <sub>2</sub> ·H <sub>2</sub> O | 10  | g/I  |

MAXIMUM OPERATING TEMPERATURE:

55<sup>0</sup>C

<sup>\*</sup>REFERENCE NO. A3, Page 740.

#### 3.3 IMMERSION PALLADIUM STUDIES

The baseline NPMS process outlined in Table 1 provides for the use of three chemical plating solutions. The first solution deposits a layer of elemental palladium (or a palladium compound) by means of a chemical displacement reaction at the silicon surface. The chemical bath used to achieve this reaction is a solution containing palladium chloride (PdCl<sub>2</sub>) and is called an immersion bath since the displacement reaction is initiated merely by immersing the silicon substrate into the bath.

A primary purpose of the immersion palladium layer is preparation of the silicon surface for subsequent deposition of the electroless palladium layer. Without such preparation, the silicon surfaces of solar cells have proven very difficult to plate in electroless palladium plating solutions. This difficulty is compounded by the high impurity concentrations and opposite conductivity types of the front and back cell surfaces. In order to provide a more catalytic surface, and to minimize electroless plating rate difference between n-type and p-type surfaces, a thin immersion palladium layer is deposited first.

Exact requirements of the immersion palladium layer are as yet unknown.

Optimum layer composition, thickness, grain size, and grain structure have yet to be determined. Studies have been initiated to define these unknowns.

Additional studies are being conducted on the chemistry of palladium solutions. The goal is to not only pick the most effective bath composition, but also to determine bath requirements and usage as they affect process control limits.

Several types of palladium chloride solutions are under consideration for use as the immersion palladium bath. Differences between the solutions manifest themselves as differences in plating rates on silicon surfaces of

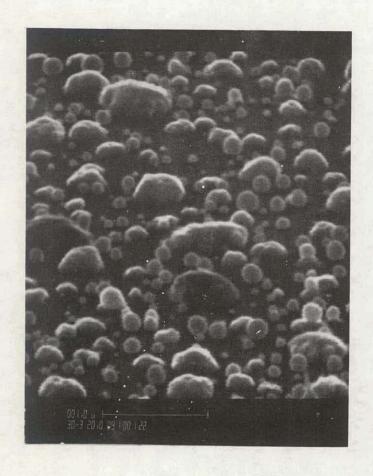

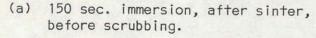

various conductivities and conductivity types. One thing various baths considered to date have in common is the fundamental structure of the palladium deposits. Scanning electron microscope (SEM) photographs show that the palladium is deposited in somewhat hemispherical clumps (grains) of metal (or metal compounds) scattered across the surface of the silicon.

In one experiment, for example, fluorinated solutions of palladium chloride  $(PdCl_2)$  were prepared with different  $PdCl_2$  concentrations: 0.5 standard, standard, 2 standard and 5 standard. Silicon wafers were immersed for 75 seconds and 150 seconds into each of these solutions. The results are shown in the SEM photographs of Figures 1, 2, 3, and 4.

Observed grain size of the deposits from these baths varies from much less than 0.1 micron diameter to as large as 0.5 micron diameter. Grain size, as well as the spacing between grains, is strongly dependent on the concentration of PdCl<sub>2</sub> in solution as well as the length of time for which the silicon is plated. As seen in Figures 1 through 4, as PdCl<sub>2</sub> concentration was increased the size of the largest grains deposited became greater. As plating time was increased there seemed to be a tendency to obtain greater coverage of the silicon surface by depositing small grains in the spaces between the large grains.

Whether any one of the deposits observed in Figures 1 through 4 is any-where near optimum is not yet known. Once heat treated (sintered), those deposits provide nucleation sites for the catalytic formation of electroless palladium films. It is believed that the electroless palladium will adhere only to the grains deposited in the immersion step. Thus, a major requirement on the initial immersion palladium layer is that it provide an adherent formation (of grains) for the electroless palladium. A shortcoming of the particular deposits shown in Figures 1 through 4 is that, even after sintering,

(a) 75 sec. immersion

(b) 150 sec. immersion

FIGURE 1: Immersion palladium plating at one half standard palladium chloride concentration.

(a) 75 sec. immersion

(b) 150 sec. immersion

FIGURE 2: Immersion palladium plating at standard palladium chloride concentration.

(a) 75 sec. immersion

(b) 150 sec. immersion

FIGURE 3: Immersion palladium plating at twice standard palladium chloride concentration.

(a) 75 sec. immersion

(b) 150 sec. immersion

FIGURE 4: Immersion palladium plating at five times standard palladium chloride concentration.

a substantial portion of the grains can be removed by mechanical abrasion or scrubbing, indicating that adherence is probably not adequate. This is illustrated in Figure 5 which shows an SEM shot of a solar cell surface after the first three steps of Table 1. Scrubbing (in this case with a cellulose tissue) has removed a considerable amount of the grains, and shows some smearing of metal.

Currently, the baseline NPMS process sequence (Table 1) incorporates

Step #3 for removal of any nonadherent palladium after the initial immersion

deposit and sinter. This scrubbing step appears to promote adherence of

subsequently deposited metal on the back surface. However, the inability

of effectively scrubbing the patterned front surface metal, particularly

with texture etched wafers, and the expense of scrubbing, make effective

elimination of this step a major program requirement.

Aside from the effects of solution concentration and plating times, it has been determined that the quality of plating depends very strongly on cleanliness of the silicon surface. Studies have been initiated to find a sufficient, yet simple, reproducible silicon cleaning procedure prior to the first (immersion) palladium deposition.

Both wet chemistry and plasma cleaning processes are being pursued. Experiments are being performed with organic contaminant removal solutions such as hot sulfuric acid, with oxide etching solutions such as various dilutions of hydrofluoric acid, and with weak silicon etching solutions such as those containing combinations of nitric acid and hydrofluoric acid. Plasma experiments are being conducted with both oxidizing plasmas  $(O_2)$  and etching plasmas  $(CF_A)$ .

(b) after sinter, after scrubbing

FIGURE 5: Immersion palladium plating at five times standard palladium chloride concentration after sintering 15 min. at  $700^{\circ}$ C.

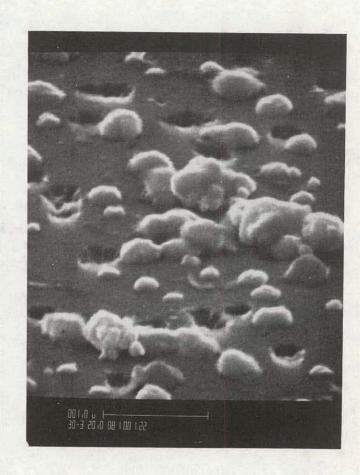

Immersion plating deposits on the facets of a texture-etched surface

look similar to those shown in Figures 1 - 4. The different crystallographic orientation (<111> for the textured facets vs <100> for the solar cell back surface) also may play a role (in addition to that of conductivity type).

Figure 6 shows grains of various sizes immersion plated on <111> facets of an n+ textured surface.

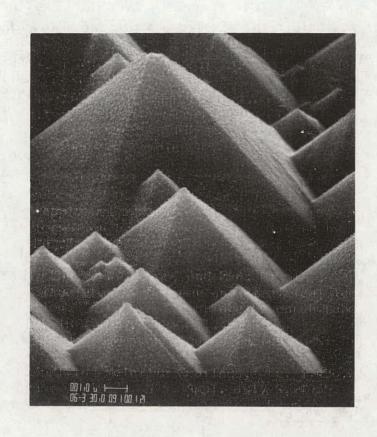

#### 3.4 ELECTROLESS PALLADIUM STUDIES

After the n-type and p-type silicon surfaces of the solar cell have been suitably prepared (Steps 1 - 3 of Table 1), a thicker and more continuous layer of palladium is applied with an electroless palladium bath. Since the electroless plating reaction is auto-catalytic, a reasonably thick layer of palladium can be applied without the need for several repeated immersions. The electroless palladium layer serves as the primary contact adhesion layer, being at least partially reacted by sintering at an elevated temperature to form palladium silicide (Pd<sub>2</sub>Si).

Requirements of the palladium silicide/palladium layer are excellent adhesion and low contact resistance. From a process control standpoint, the layer must be of uniform thickness across the solar cell, especially on the front surface where the junction is very shallow.

Several formulations of electroless palladium solutions utilizing sodium hypophosphite as a reducing agent are being investigated, although most experience to date has been with the formulation given in Table 3. Alternate solutions with different concentrations of sodium hypophosphite are under consideration. Experiments so far have not resulted in a preference for one particular solution formula.

FIGURE 6: Immersion palladium plating on <111> facets of n+ textured front surface.

Aside from the composition, temperature, and age of the electroless palladium bath, other factors influence the formation of the plated palladium layer. According to the baseline process sequence, prior to electroless palladium plating the solar cell has received an immersion palladium layer and has been sintered at temperatures near 600°C. Any oxides formed during this sinter would act to inhibit the electroless plating. Therefore, some sort of pre-plating clean is necessary to insure adequate plating action. To date, sufficient preparation seems to be a short rinse in dilute hydrofluoric acid solution, although this may not be optimum.

In addition to pre-plating cleans, ambient illumination has proven to have an influence on solar cell electroless plating rates. Increased illumination intensity will enhance n-type surface plating with respect to p-type surface plating. This appears to be a direct result of the photovoltage generated by the solar cell.

Figure 7 shows electroless palladium deposits on back (flat, p+) and front (textured, n+) surfaces of a solar cell.

#### 3.5 LITERATURE SURVEY

An annotated NPMS bibliography has been compiled and is appended to this report. This bibliography lists references to articles in the technical literature and to U. S. and foreign patent disclosures which are related to the "nickel-palladium metallization system". The bibliography is divided into three sections. There are three listings in Section A, General Reference. There are thirty-two listings in Section B, Metal-Silicide Contacts and Contact Formation. There are ten listings in Section C, Chemical Plating Solutions. As pertinent new references are found throughout the duration of this contract, the bibliography will be updated.

(a) textured n+ front surface

(b) flat p+ back surface

FIGURE 7: Electroless plated palladium layers

Additional detailed references to nickel plating solutions and techniques are easily found in one of the general references cited in Section A. Since electroless nickel plating is well established in the literature (and has been for sometime) most of the references given in the bibliography deal with palladium plating and the characterization of palladium contacts to silicon.

Each entry in the bibliography is accompanied by a short description of the contents of the reference.

#### 4.0 CONCLUSIONS

This contract effort is in the early stages and no firm conclusions can be drawn as yet. However, several pertinent observations can be summarized.

The technical and patent literature discussing palladium silicide formation and palladium-silicon contacts is strongly supportive of the use of palladium for solar cell metallization systems.

The application of metal contacts by chemical plating techniques, particularly using immersion and electroless plating solutions, provides a very desirable means for metallizing both regular and irregular silicon solar cell surfaces.

The success of the plated "nickel palladium metallization system" as judged by adherence, reliability, and uniformity during processing depends very strongly on maintaining a microscopically clean silicon surface immediately prior to the first plating (Pd) application.

#### 5.0 RECOMMENDATIONS

There are no specific recommendations at this time.

#### 6.0 NEW TECHNOLOGY

No new technology has been developed to completion during the course of this reporting period.

#### 7.0 NPMS ANNOTATED BIBLIOGRAPHY

#### A. GENERAL REFERENCES

- Feldstein, N., "Electroless Plating in the Semiconductor Industry," <u>Solid State Technology</u>, 16, 87 (Dec. 1973).

Review of the use of electroless metal plating, including nickel, on semiconductors.

- Graham, A.K., ed., <u>Electroplating Engineering Handbook</u>, Third Edition, Van Nostrand Reinhold Company, New York, 1971.

General reference work for plating techniques. Part 1, Chapter 15 discusses electroless plating solutions.

- 3. Lowenheim, F.A., ed., Modern Electroplating, Third Edition, John Wiley & Sons, Inc., New York, 1974. Excellent general reference for chemical plating techniques and solutions, including electroless nickel and palladium. In particular, see chapters 12, 14, and 31.

#### B. METAL-SILICIDE CONTACTS AND CONTACT FORMATION

barrier.

- Anand, Y., "Zero-Bias Schottky Barrier Detector Diodes,"

U.S. 3,968,272 (cl. 427-84; B05D5/12), July 6, 1976. Appl. 436,431, Jan. 25, 1974.

A Schottky diode using metal (Pd, Pt, Hf) silicide-silicon

- 2. Austen, H.E., and R.D. Fisher, "Internal Stress of Electroless Metal Films on Single Crystal Silicon," J. Electrochem. Soc. 116, 185

(1969).

Stress measurements for electroless Ni and Co films as a function of thickness.

- Bower, R.W., and J.W. Mayer, "Growth Kinetics Observed in the Formation of Metal Silicides on Silicon," <u>Appl. Phys. Lett.</u>, 20 (9), 359 361, (1972).

Brief discussion of silicide growth from evaporated metal films.

- Bower, R.W., D. Sigurd, and R.E. Scott, "Formation Kinetics and Structure of Pd<sub>2</sub>Si Films on Si," <u>Solid-State Electron.</u>, <u>16</u> (12), 1461 1471, (1973).

Rates of palladium silicide formation from evaporated Pd layers on different Si crystal orientations.

- 5. Bower, R.W., et. al., "Analysis of Semiconductor Structures by Nuclear and Electrical Techniques: Silicide Formation," Air Force Cambridge Research Laboratories Report No. AFCRL-TR-74-0247, April 30, 1974. Metal silicide formation studies including Ni<sub>2</sub>Si, NiSi, and NiSi<sub>2</sub>.

- 6. Buckley, W.D., "Electrodes for Amorphous Semiconductor Switch Devices," U.S. 3,877,049 (Cl. 357-2; HO1L), Apr. 8, 1975. Appl. 419,633, Nov. 28, 1973.

Palladium silicide used as a switch contact.

- Buckley, W. D., and S.C. Moss, "Structure and Electrical Characteristics of Epitaxial Palladium Silicide Contacts on Single Crystal Silicon and Diffused P-N Diodes," <u>Solid-State Electron</u>., <u>15</u> (12), 1331, (1972).

Analysis of  $\mathrm{Pd}_2\mathrm{Si}$  formed at several different temperatures, with attention 2 preservation of  $\mathrm{Si}$  crystal structure.

- 8. Calandrello, N.A., J. Hill, and J. Ryan, "Forming Semiconductor Contacts," <a href="Brit.1,010,398">Brit.1,010,398</a> (Cl. HOll, 17/46), Nov. 17, 1965. U.S. Appl. Feb. 6, 1963. Contact to silicon is made by plating Au or Pd on silicon, then plating Ni, then heating to alloy the layers. Ni is applied again to thicken the top metal layer. The metal layers are then solder dipped.

- 9. Castrucci, P.P., and R.P. Pecoraro, "Palladium Ohmic Contact to Silicon Semiconductor," <u>U.S. 3,431,472</u> (Cl. 317-324; HO1L), Mar. 4, 1969. Appl. Oct. 17, 1967.

Contact formation by Pd deposition followed by sintering to form Pd<sub>2</sub>Si.

- 10. Chu, W.K., S.S. Lau, J-W. Mayer, and M-A, Nicolet, "Analysis of Semiconductor Structures by Nuclear and Electrical Techniques: Silicide Formation." Air Force Cambridge Research Laboratories Report No. AFCRL-TR-75-0092, Jan. 31, 1975.

Metal silicide formation studies including Ni<sub>2</sub>Si and Pd<sub>2</sub>Si.

- 11. Chuss, J.T., "Applying Metallic Coatings," Fr. 1,486,263

(Cl. H01L), June 23, 1967. U.S. Appl. July 9, 1965.

Deposition of palladium on Si wafers by means of electroless plating solutions followed by electroless nickel.

- 12. Dorendorf, H., H. Eger, H. Weidlich, and H. Glawischnig, "Silicon Planar Transistor," <u>Ger. Offen. 2,044,467</u> (Cl. HO1L), Mar. 23, 1972. Appl. P 20 44 467.1, Sept. 8, 1970.

A device using Al over Pt\_Si or Pd\_Si contacts. The contacts are formed from 50 100Å of evaporated or sputtered metal.

- 13. Drobek, J., R. C. Sun, and T.C. Tisone, "Interdiffusion and Compound Formation in Thin Films of Pd or Pt on Si Single Crystals,"

Phys. Stat. Sol. (A), 8 (1), 243 248, (1971).

Silicide formation interpreted from electron microscope observations.

- 14. Dudko, G.N., A.G. Pilipenko, and V.I. Tarakanov, "Structure of Films and Phase Changes in the Palladium-Silicon Contact Zone," Isv. Vyssh. Ucheb. Zaved., Fiz., 17 (5), 21 (1974). Improvements in Pd<sub>2</sub>Si contact conductance by altering the silicide crystal structure by annealing.

- Hutchins, G.A., and A. Shepela, "The Growth and Transformation of Pd<sub>2</sub>Si on (111), (110) and (100) Si," <u>Thin Solid Films</u>, <u>18</u> (2), 343 363, (1973).

Thorough discussion of Pd<sub>2</sub>Si formation at different temperatures and on differently oriented Si crystals.

- 16. Iwasa, H., M. Yokozawa, and I. Teramoto, "Electroless Nickel Plating on Silicon," <u>J. Electrochem. Soc.</u>, <u>115</u> (5), 485 (1968). Differences in plating rates for n- and p- type silicon on wafers with p-n junctions.

- 17. Kahng, D., and M.P. Lepselter, "Barrier Diode with Metal Contact," U.S. 3,290,127 (Cl. 29-195), Dec. 6, 1966. Appl. March 30, 1964. Device illustrates use of palladium silicide as an electrical contact.

- Kircher, C.J., "Metallurgical Properties and Electrical Characteristics of Palladium Silicide-Silicon Contacts," <u>Solid-State Electron.</u>, <u>14</u>

(6), 507 513, 1971.

General characterization of Pd<sub>2</sub>Si contacts.

- 19. Lau, S.S., and D. Sigurd, "An Investigation of the Structure of Pd<sub>2</sub>Si Formed on Si," <u>J. Electrochem. Soc.</u>, <u>121</u> (11), 1538 1540, (1974).

Crystal size and formation kinetics of Pd<sub>2</sub>Si formed from Pd films on silicon.

- 20. Lee, D.H., R.R. Hart, D.A. Kiewit, and O.J. Marsh, "Alloying of Thin Palladium Films with Single Crystal and Amorphous Silicon," Phys. Stat. Sol. (A), 15 (2), 645 - 651, (1973). Conditions under which palladium silicide will form.

- 21. Mayer, A., "Forming Ohmic Contacts on Metal-Insulator-Semiconductor Components," Ger. Offen. 2,128,360 (Cl. H01L), Jan. 13, 1972. U.S. Appl. 50,506, June 29, 1970. Deposition of Pt or Pd from an acid solution onto Si substrate and formation of a silicide by heating the substrate.

- 22. Mayer, J.W., and K.N. Tu, "Analysis of Thin-Film Structures with Nuclear Backscattering and X-ray Diffraction," J. Vac. Sci. Technol., 11 (1), 86 (1974).

Includes general review of contemporary studies of silicide formation.

- 23. Michelet, P., "Electrical Contacts on the Surface of Semiconductors," <a href="fr.1,197,979">Fr. 1,197,979</a>, Dec. 3, 1959. Formation of a silicide by heating the substrate during metal deposition by evaporation.

- 24. Nakamura, K., J.O. Olowolafe, S.S. Lau, M.A. Nicolet, J.W. Mayer, and R. Shima, "Interaction of Metal Layers with Polycrystalline Si," J. Appl. Phys., 47 (4), 1278 1283, (1976).

Details of silicide formation on polycrystalline substrates.

- 25. Nuzillat, G., and C. Arnodo, "Adjusting the Threshold Voltage of Field Effect Transistors," Ger. Offen. 2,533, 460 (Cl. H01L), Feb. 5, 1976.

Description of a device with a gate composed of palladium silicide.

- 26. RCA Corp., "Semiconductor Ohmic Contact," <u>Brit. 1,321, 034</u> (cl. H01L), June 20, 1973. U.S. Appl. 151,340, Apr. 5, 1971. Contacts of platinum silicide are formed.

- 27. Shepela, A., "The Specific Contact Resistance of Pd<sub>2</sub>Si Contacts on n- and p- Si," <u>Solid-State Electron.</u>, <u>16</u> (4), 477 (1973). Effects of dopants and resistivity on contact resistance.

- 28. Sullivan, M.V., and J.H. Eigler, "Electroless Nickel Plating for Making Ohmics Contacts," J. Electrochem. Soc., 104 (4), 226 (1957).

A technique for plating nickel to silicon plus measurements of plating rate, contact adhesion, and contact resistance.

- 29. Tanaka, Y., and H. Hattori, "Semiconductor Devices," Fr. Demande 2,183,111 (Cl. HO1L), Jan. 18, 1974. Japan Appl. 72 44,141, May 2, 1972.

Contacts of platinum silicide were produced using chemically deposited platinum, heating to form the silicide, and over-

- 30. Teramoto, I., H. Iwasa, and H. Tai, "Contact Resistance of Electroless Nickel on Silicon," <u>J. Electrochem. Soc.</u>, <u>115</u> (9), 912 (1968). Contact resistance as a function of silicon resistivity and heat treatment.

plating with electroless nickel.

- 31. Tu, K.N., "Selective Growth of Metal-Rich Silicide of Near-Noble Metals," <u>Appl. Phys. Lett.</u>, <u>27</u> (4), 221 (1975).

A discussion of metal diffusion in the formation of metal silicides.

- 32. Tu, K.N., W.K. Chu, and J.W. Mayer, "Structure and Growth Kinetics of Ni<sub>2</sub>Si on Silicon," <u>Thin Solid Films</u>, <u>25</u>, 403 (1975). Formation mechanisms and rates for low temperature (200°C 325°C) nickel silicide.

#### C. CHEMICAL PLATING SOLUTIONS

Brenner, A., and G. Riddell, J. Res. National Bur. Stan., 37, 32 (1946); Proc. Am. Electroplating Soc., 33, 23 (1946).

Original references for electroless nickel plating.

- Honda, T., and Y. Usami, "Electroless Palladium Plating,"

Japan. 71 01,241 (Cl. C 23c), Jan. 13, 1971. Appl. Aug. 30, 1968.

An electroless palladium solution containing hydrazine sulfate.

- Korovin, N.V., S.B. Kalmykova, and S. Yu. Vereschinskii, "Solution for Chemical Palladium Plating," <u>U.S.S.R. 291,991</u> (Cl. C23c), Jan. 6, 1971. Appl. Sept. 15, 1969.

A solution for the chemical Pd plating of metals containing sodium hypophosphite.

- Murski, K., "Practical Electroless Nickel Plating," <u>Metal Finishing</u>, 68, 38 (1970).

Defines operational parameters and control techniques for electroless nickel plating.

- Pearlstein, F., and R.F. Weightman, "Electroless Palladium Deposition," <u>Plating</u>, 56, 1158 (1969).

Detailed discussion of electroless palladium solutions utilizing sodium hypophosphite.

- 6. Reinhardt, R.A., and K.J. Graham, "Equilibrium and Kinetics of Some Simple Complexes of Palladium (II)." <u>U.S. NTIS, AD Rep.</u>, AD A030089, 1976.

Chemical data on complexes and reactions present in electro-

- Chemical data on complexes and reactions present in electroless plating baths.

- 7. Rhoda, R.N., "Barrel Plating by Means of Electroless Palladium,"

J. Electrochem. Soc., 108, 707 (1961).

Discussion of plating metallic substrates with electroless palladium solution utilizing hydrazine.

- 8. Sergienko, A., "Bath for the Electroless Deposition of Palladium," U.S. 3,418, 143, Dec. 24, 1968. Appl. 660,588, Aug. 15, 1967.

A palladium solution utilizing hypophosphite ion.

- Vereschinskii, S. Yu., S.B. Kalmykova, and N.V. Korovin,

"Electroless Palladium Plating Process," <u>Zashch. Metal</u>, 9 (1),

227 (1973).

Depositing Pd on various metals, graphite, and glass using a

solution containing sodium hypophosphite.

- 10. Zayots, A.I., I.A. Stepanova, and A.V. Gorodyskii, "Chemical Reduction of Palladium by Sodium Hypophosphite," Zashch. Metal., 9, (1), 116 (1973).

Solution composition and conditions for depositing palladium on nickel.